Lab 1: Parking Lot Occupancy Counter

Overview

This lab is a refresher on finite state machines (FSMs) that you learned about and designed in EE271 or CSE369. Be sure to read the and before getting started so you know what information to collect and present as you go.

Parking Lot Occupancy Counter

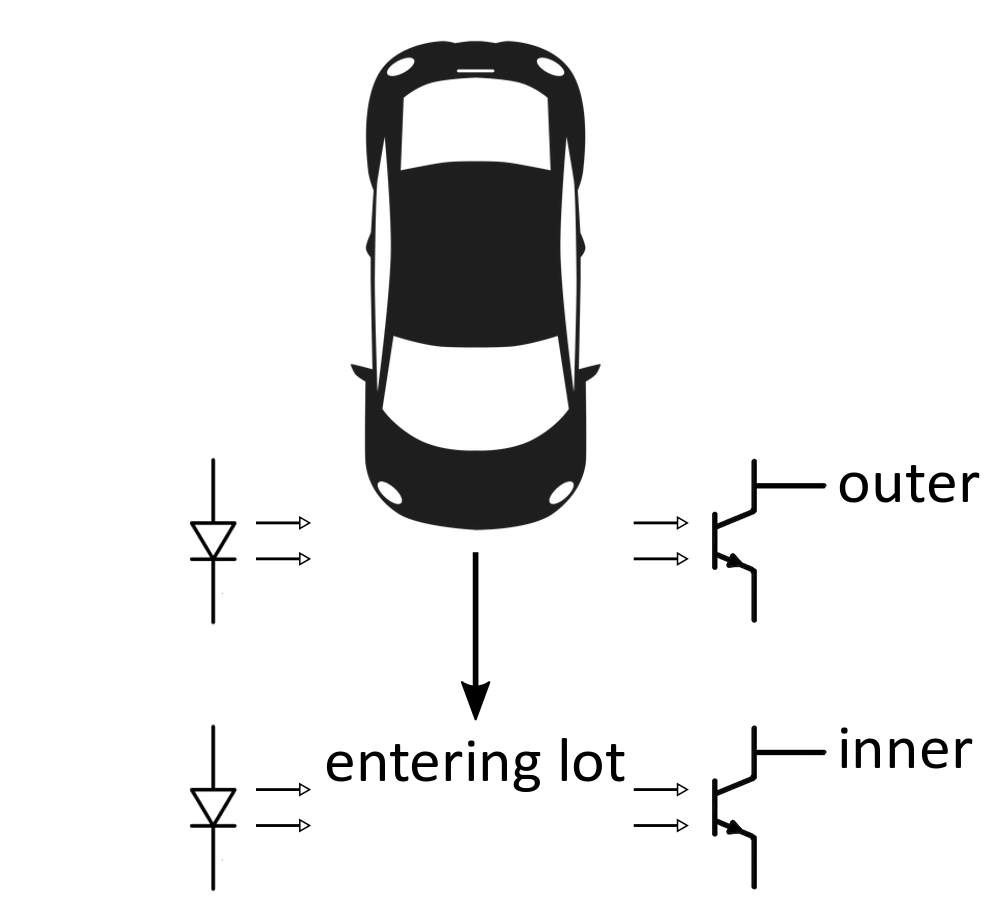

Consider a parking lot with a single gate for both entry and exit. To keep track of the occupancy of the lot, we decide to use two photosensors to track when cars enter or exit, as shown in the figure below.

When an object is between the photo transmitter and the photo receiver, the light is blocked and the corresponding output is asserted to 1. By monitoring the events of both sensors, we can determine whether a car is entering or exiting, or even if a pedestrian is passing through! You may assume that two cars won't be entering/exiting at the same time and that you don't have to worry about multiple pedestrians mimicking a car (i.e., if it looks like a car sequence, count it as a car).

For example, the following sequence indicates that a car entered:

- Initially, both sensors are unblocked (i.e., {outer, inner} == 2'b00).

- Sensor outer becomes blocked (i.e., 2'b10).

- Both sensors are blocked (i.e., 2'b11).

- Sensor outer becomes unblocked (i.e., 2'b01).

- Both sensors are unblocked (i.e., 2'b00).

Lab Code

Starting a Project

You can (1) start from a copy of an existing project folder from EE271 or CSE369 or (2) watch the following video on how to .

Helpful Project Files

The use of these are optional, depending on your preferred workflow. Versions of these should have been provided in EE271 and CSE369.

- (to launch ModelSim from the directory instead of through Quartus)

- (to script the ModelSim commands for simulation)

Code for this Lab

For .sv files, you may want to right-click and save/download instead of clicking.

Instructions

Design a Parking Lot Occupancy Counter as Follows

- Design and implement an FSM for the car detection with two

input signals, outer and inner, and two output

signals, enter and exit.

The enter and exit signals assert true for one

clock cycle when a car enters or exits the lot, respectively.

- You may assume that cars will not change direction while entering or exiting the parking lot.

- Make sure that your FSM does not detect/count invalid sensor sequences.

- Design and implement a car counter with two

control signals, incr and decr, which increment

and decrement the counter, respectively, when asserted.

- Assume that the maximum capacity of the parking lot is 16 spots.

- Design and implement a module for the parking

lot occupancy, which combines the car detection and counter.

Your system should have the following properties:

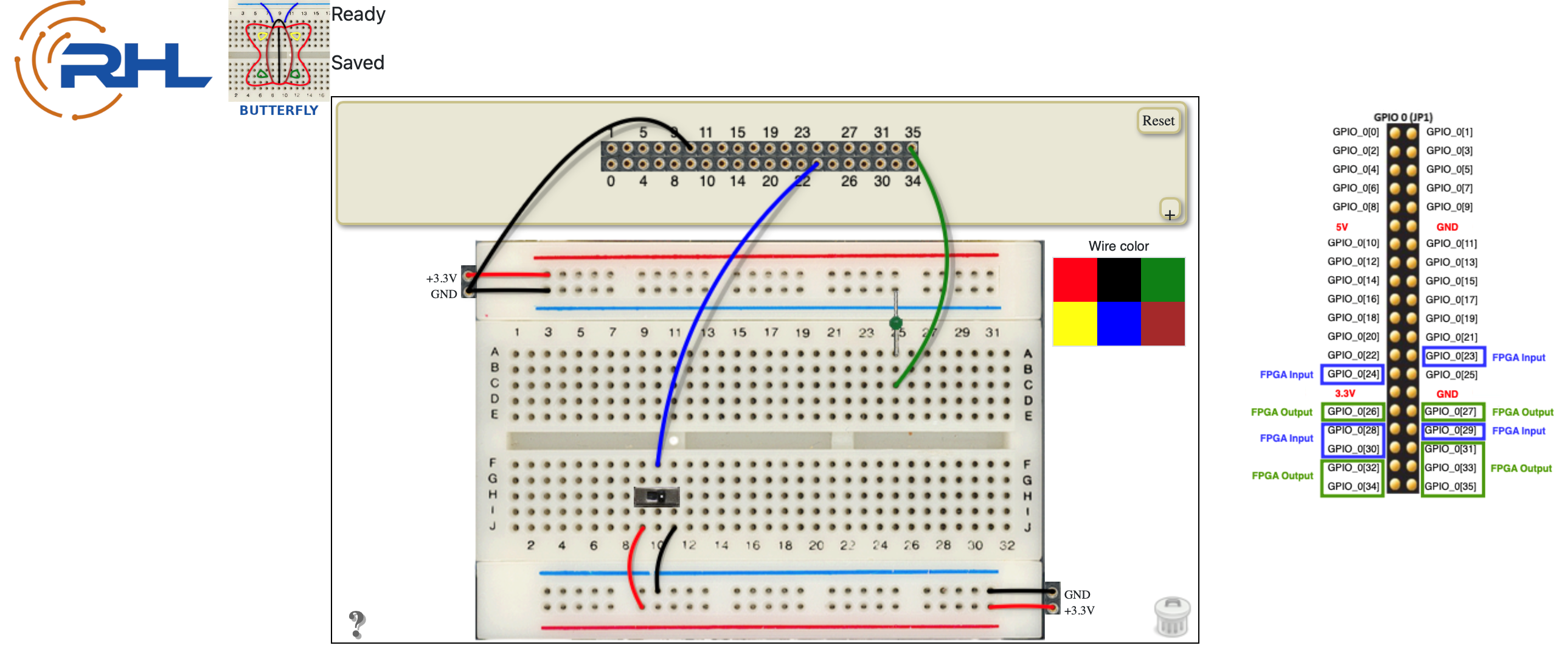

- Use off-board switches (i.e., not the SWs) to mimic the two photosensor outputs.

- Display the current car count on the seven-segment displays

HEX1 and HEX0, with the following exceptions:

- If the counter reaches 16, display "FULL" on HEX5 – HEX2.

- When the lot is empty, display "CLEAR" on HEX5 – HEX1 and the number "0" on HEX0.

- Use 2 off-board LEDs (i.e., not the LEDRs)

to indicate the values of the outer and inner

signals.

- A logical 1 should turn the corresponding LED on and a logical 0 should turn it off.

- Wire the anodes of 2 LEDs to FPGA output ports.

- Wire the middle pins of the 3 switches to FPGA input ports of your choosing as your three inputs (reset, outer, and inner).

Lab Requirements

Lab Report

Lab Demo

Due within one week of the lab report deadline, but typically during your assigned demo slot or a scheduled office hour.

- Demonstrate your working parking lot occupancy counter on the DE1-SoC.

- Demonstrate your reset functionality.

- Be prepared to answer 1-2 questions about your design to the TA.

Grading Rubric

- System block diagram and diagrams for car detection and counting

- Simulations for top-level and car detection (none needed for car counting)

- Present state included in all FSM simulations