## **Data Hazards**

- <sub>n</sub> Data dependence

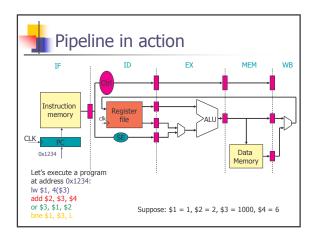

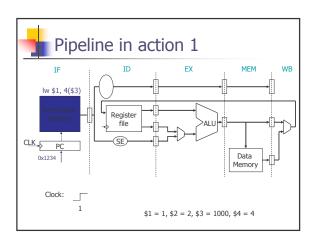

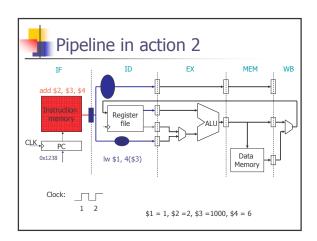

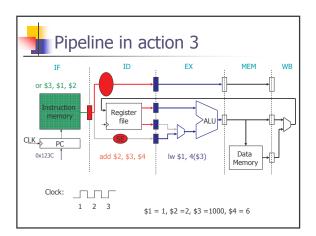

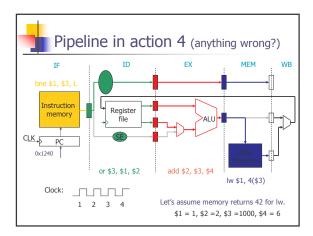

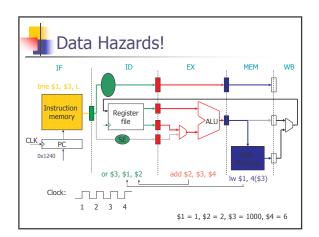

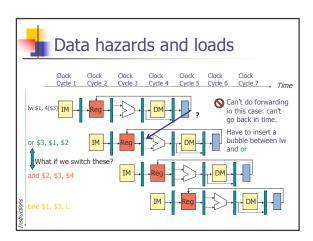

- result of an operation needed before it is stored back in reg. file:  $\frac{1}{2} \log \frac{1}{2} \frac{1}{$

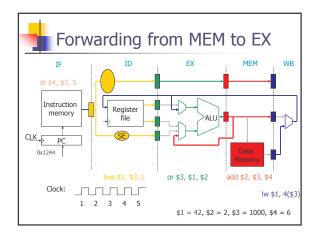

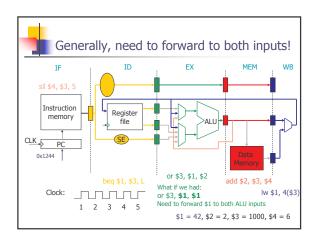

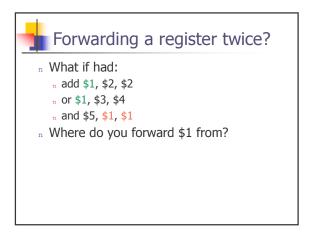

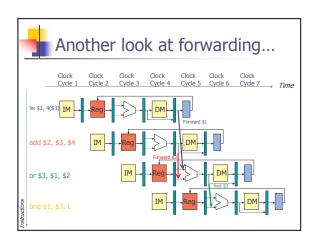

- lw <u>\$1</u>, 4(\$3) add <u>\$2</u>, \$3, \$4 or \$3, <u>\$1</u>, <u>\$2</u>

- The data hazard above is read after write (RAW)

- n Data dependence (RAW) occurs when:

- <sup>n</sup> An instruction wants to read a register in stage 2, and

- One instruction in stage 3 or stage 4 is going to write that register

- Note: if the instruction writing the register is in stage 5, this is fine since we can write a register and read it in the same cycle

- Hazard detection unit compares register fields across

## Resolving data dependencies

- n Have the compiler generate no-ops

- Don't have to deal with data hazards in hardware.

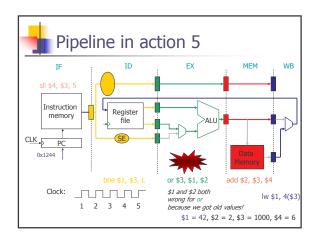

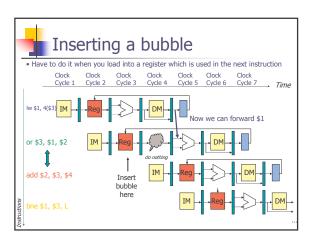

- <sup>n</sup> Stall the pipeline, i.e., create *bubbles*

- h the resulting delays are the same as for no-ops

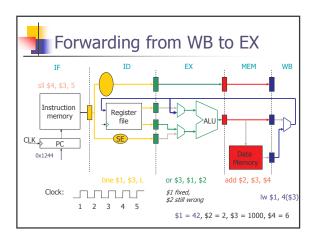

- Send the result generated in stage 3 or stage 4 to the appropriate input of the ALU.

- n This is forwarding or bypassing.

- More performance at the cost of more hardware

- a For one simple pipeline, cost is slightly more control and extra buses

- $_{\scriptscriptstyle \rm I\!\! I}$  For several pipelines, say n, communication grows as O(n²)

- - when an instruction in the pipeline is *dependent* on another instruction still in the pipeline.

- Resolved by:

- Bypassing/forwarding

- Stalling

## Other types of hazards:

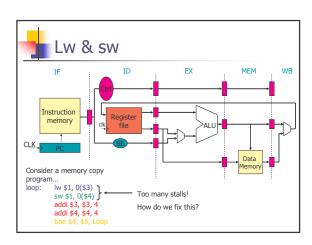

- Structural hazards

- where two instructions at different stages want to use the same resource.  $% \left( 1\right) =\left( 1\right) \left( 1\right)$

- Solved by using more resources (e.g., instruction and data memory; several ALU's). Won't happen in our pipeline.

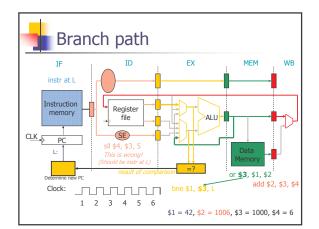

- Control hazards

- happens on a taken branch.

- Evaluation of branch condition and calculation of branch target is not completed before next instruction is fetched.

## Resolving control hazards

- Stall until result of the condition & target are known

- n too slow

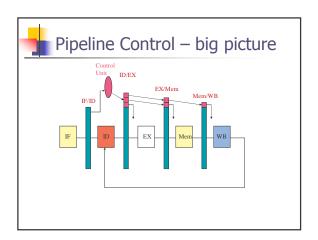

- Reduce penalty by redesigning the pipeline:

- move branch calculation to ID stage

- move branch comparison to ID stage how to do quick compare?

- use both edges of the clock

- Delay slots

- specify in ISA that instruction after branch is always executed.

- n Branch prediction

- n in IF stage, guess branch outcome

- n correct it if turns out to be wrong.