# A Common Framework for Memory Hierarchies

Caching, paged virtual memory and TLBs all use the same underlying concepts

| Feature                                                                 | Cache | Paged Mem                                                   | TLB                                                    |

|-------------------------------------------------------------------------|-------|-------------------------------------------------------------|--------------------------------------------------------|

| Size, Blocks<br>Size, Bytes<br>Blk Size, B<br>Miss Penalty<br>Miss Rate |       | 2K-250K<br>8MB-8GB<br>4KB-64KB<br>1M-10Mclk<br>10^-4-10^-5% | 32-4000<br>128B-8000B<br>4-32<br>10-100clk<br>0.01%-2% |

D Larry Snyder, 2000 All rights reserved

### Four Questions for Classification

- Where can a block be placed? Block placement

- direct mapped, set associative, fully associative

- · How is a block found? Block identification

- indexing, set search, separate lookup table

- What block is replaced on a miss? Block replacement

- LRU, Random, FIFO, MRU

- How are writes handled? Write strategy

- write through or write back

Summary and Review

O.L. serv. Smoder. 2000 All rights rese

### **Block Placement**

The extremes of cache mapping -- direct mapped and fully associative are end points on a spectrum

Blocks are assigned to a cache by directly indexing any of its *n* sets and matching any of the *m* entries of the set associatively by the tag

Indexing is "block number modulo number of sets"

Larry Sayder, 2000

# Block Identification Placement of a block whose address is 12 varies for direct, set associative, and fully associative Directed Mapped 12 MOD 8 = 4 Tag Data 12 MOD 2 = 0 Tag Data Tag DataTag DataTag DataTag DataTag Data Fully Associative

Tag DataTag DataTag DataTag DataTag DataTag DataTag DataTag DataTag Data

# **Block Replacement**

- · Replacement candidates are --

- Any block in a fully associative cache

- Any block in a raily associative cache

Any block of a set in set associative caches

- The indexed block for direct mapped

- · Replacement strategies --

- Opt is best, but impossible

- Least Recently Used (LRU) approximates Opt. Expensive

- Random is easy, but impossible for software management

- For 2-way s.a., random has 1.1 times higher miss rate than I RII

- "Use" bit can approximate LRU

Write Strategy

- Write through simultaneously updates the cache and the lower level in the memory hierarchy on each write.

- Write back only updates the cache copy until the block is replaced, at which point the next lower level of the hierarchy is updated.

- Write through advantages --

- Read misses are cheaper due to not waiting for write. Easier to implement, though it needs a write buffer.

- Write back advantages --

- Multiple writes to a block require only one memory write.

- Can utilize wider channel to lower level memory.

- Write back is always needed between memory & disk.

- Dirty bit in page table determines if write back needed.

© Larry Snyder, 2000 All rights reserve

# Mapping Choices in Hierarchy

- Tradeoff cost of miss vs cost of associativity.

- · VM uses fully associative mapping

- Reduces miss rate, because miss penalty is high

- Mapping done in software

- Large page size means page table size overhead is small

- Note that page table is indexed, but full map provides fully associative placement

- · Small caches (TLB) often use set associative placement

- · Large caches never use fully associative placement

- High cost and hit time penalties

- Small performance advantage to set associative

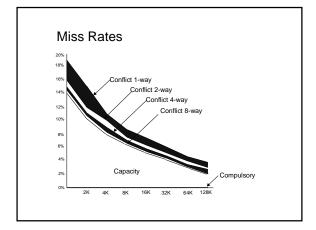

### The Three Cs

Missing in the cache can be caused by three different circumstances:

- Compulsory misses -- miss on first access

- Capacity misses -- miss due to cache not having enough blocks

- Conflict misses -- miss due to cache organization

In cache design, larger is always better ... but there are always trade-offs

### The Problem with Miss-rate

It doesn't tell the whole story:

Consider increasing direct-mapped cache from 32K to 64K Miss Rate drops from 5% to 4%. If the larger cache implies a cycle time of 18ns and the smaller cache implies a cycle time of 15ns, the smaller cache machine has better performace

Postulate: CPI w/o stalls is unchanged

Miss penalty 180ns

Memory references per instruction = 1.5 CPU Time = (CPU execution clock cycles + Memory-stall clock

cycles) × Clock cycle time

# Cache Analysis, Continued

$\label{eq:memory-stall} \mbox{Memory-stall clock cycles} = \mbox{$\frac{Instructions}{Program}$} \times \mbox{$\frac{Misses}{Instruction}$}$ × Miss penalty

$\label{eq:misses} \mbox{Misses} \ = \ \mbox{Instruction miss rate} + \mbox{Data miss rate} \times \frac{\mbox{Data references}}{\mbox{Instructions}}$

Let IC be instructions per program

Smaller Cache Memory stall clock cycles =  $IC \times (0.05 + 0.05 \times 0.5) \times$ Absolute miss penalty

Clockcycle time = IC × 0.075 × 180/15 = .9IC

Larger Cache Memory stall clock cycles =  $IC \times (0.04 + 0.04 \times 0.5) \times$ Absolute miss penalty

Clockcycle time = IC × 0.06 × 180/18 = .6IC

Cache Analysis, Continued

Memory-stall clock cycles = 0.9IC (Small) and 0.6IC (Large cache).

Substituting into the CPU time equation, letting CPI w/o stalls be C:

CPU Time = (CPU execution clock cycles + Memory-stalls clock cycles) × Clock cycle time

Small Cache Large Cache CPU time CPU time =( (C × IC) + (0.6 × IC) × 18ns = 18×C×IC + 10.8 × IC = (18C + 10.8)IC =  $((C \times IC) + (0.9 \times IC) \times 15$ ns =  $15 \times C \times IC + 13.5 \times IC$ = (15C + 13.5)IC

For  $C \ge 1$  the smaller cache is better