#### Overview

- Last lecture

- Sequential Logic Examples

- Today

- State encoding

- ✓ One-hot encoding

- **∠** Output encoding

CSE370, Lecture 24

## One-hot encoding

- One-hot: Encode n states using n flip-flops

- Assign a single "1" for each state

∠ Example: 0001, 0010, 0100, 1000

- Propagate a single "1" from one flip-flop to the next ∠ All other flip-flop outputs are "0"

- The inverse: One-cold encoding

- Assign a single "0" for each state

∠ Example: 1110, 1101, 1011, 0111

Propagate a single "0" from one flip-flop to the next

∠ All other flip-flop outputs are "1"

- "almost one-hot" encoding

- Use no-hot (000...0) for the initial (reset state)

- Assumes you never revisit the reset state

CSE370, Lecture 24

### State encoding

- ◆ Assume n state bits and m states

- $2^{n}! / (2^{n} m)!$  possible encodings  $[m \ge n \ge log_{2}(m)]$

- ✓ From binomial expansion

✓ Example: 3 state bits, 4 states, 1680 possible state assignments

- Hard problem, with no known algorithmic solution

- Can try heuristic approaches

- Can try to optimize some metric

- ✓ FSM dependencies (decomposition)

- Need to consider startup

- Self-starting FSM or explicit reset input

CSE370, Lecture 24

## One-hot encoding (con't)

- Often the best approach for FPGAs

- FPGAs have many flip-flops

- One-hot machines use the least next-state logic

- ◆ Draw FSM directly from the state diagram

- One product term per incoming arc

- $\qquad \hbox{\bf But complex state diagram} \Rightarrow \hbox{\bf complex design} \\$

- ◆ One-hot designs have many possible failure modes

- All states that aren't one-hot

Can create logic to reset the FSM if it enters illegal state

- ◆ Large machines require many flip-flops

- Decompose design into smaller one-hot encoded sub-designs

CSE370, Lecture 24

#### State-encoding strategies

- No guarantee of optimality

- An intractable problem

- Most common strategies

- Binary (sequential) number states as in the state table

- Random computer tries random encodings

- Heuristic rules of thumb that seem to work well **∠** e.g. Gray-code – try to give adjacent states (states with an arc between them) codes that differ in only one bit position

- One-hot use as many state bits as there are states

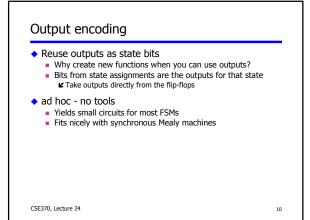

- Output use outputs to help encode states

CSE370, Lecture 24

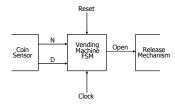

#### Vending machine again...

- Release item after receiving 15 cents

- Single coin slot for dimes and nickels ✓ Sensor specifies coin type

- Machine does not give change

CSE370, Lecture 24

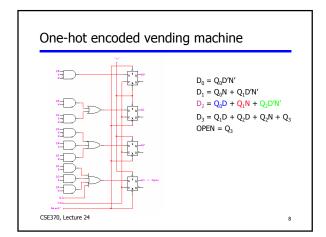

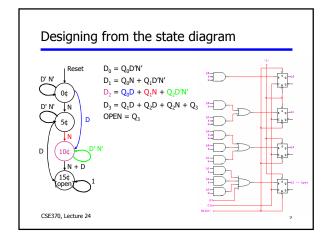

#### One-hot encoded transition table present state inputs next state output $Q_3Q_2Q_1Q_0$ D N $D_3D_2D_1D_0$ open $D_0 = Q_0 D' N'$ 0 0 0 1 0 0 0 1 0001 00 0 $\mathsf{D}_1 = \mathsf{Q}_0 \mathsf{N} + \mathsf{Q}_1 \mathsf{D}' \mathsf{N}'$ $D_2 = Q_0D + Q_1N + Q_2D'N'$ 0 1 0 0 1 0 0 $D_3 = Q_1D + Q_2D + Q_2N + Q_3$ 0 0 1 0 0 0 0 0 1 0 0 OPEN = $Q_3$ 0 1 0 1 0 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 1000 -- 1000 CSE370, Lecture 24

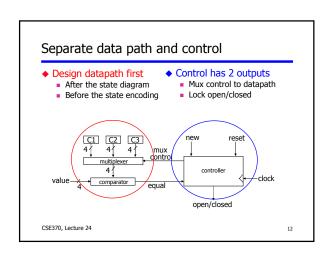

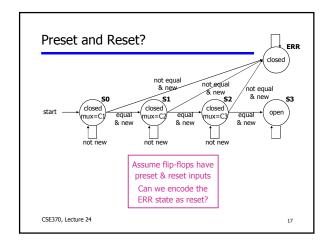

# FSM has 4 state bits and 2 inputs...

- Output encoded!

- Outputs and state bits are the same

- ◆ How do we minimize the logic?

- FSM has 4 state bits and 2 inputs (equal, new)

- 6-variable kmap?

- ◆ Notice the state assignment is close to one-hot

- ERR state (0000) is only deviation

- Is there a clever design we can use?

CSE370, Lecture 24

16

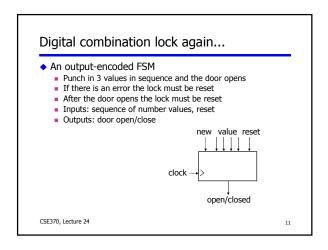

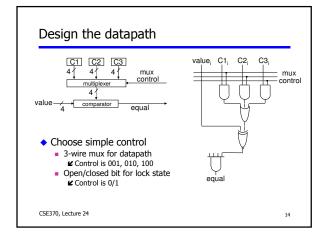

# Output encode the FSM

- FSM outputs

- Mux control is 100, 010, 001

- Lock control is 0/1

- ◆ State are: S0, S1, S2, S3, or ERR

- Can use 3, 4, or 5 bits to encode

- Have 4 outputs, so choose 4 bits

- **∠** Encode mux control and lock control in state bits

- ∠ Lock control is first bit, mux control is last 3 bits

- S0 = 0001 (lock closed, mux first code) S1 = 0010 (lock closed, mux second code)

- S2 = 0100 (lock closed, mux third code) S3 = 1000 (lock open) ERR = 0000 (error, lock closed)

15

CSE370, Lecture 24

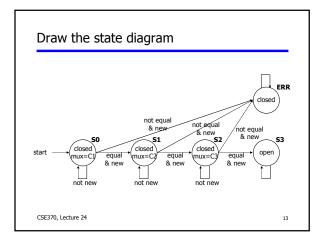

Answer: Yes! ERR not equal & new not equal not equal & new S2 & new **S**1 S0 egual mux=C not new not new

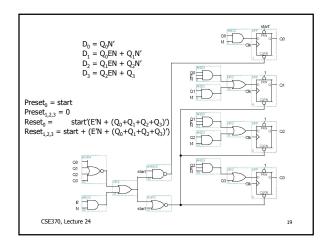

$$\begin{split} & D_0 = Q_0 N' \\ & D_1 = Q_0 E N + Q_1 N' \\ & D_2 = Q_1 E N + Q_2 N' \end{split}$$

Preset<sub>o</sub> = start Preset<sub>1,2,3</sub> = 0 Reset<sub>0</sub> = start'(E'N + (Q<sub>0</sub>+Q<sub>1</sub>+Q<sub>2</sub>+Q<sub>3</sub>)') Reset<sub>1,2,3</sub> = start + (E'N + (Q<sub>0</sub>+Q<sub>1</sub>+Q<sub>2</sub>+Q<sub>3</sub>)')  $D_3 = Q_2 EN + Q_3$ CSE370, Lecture 24

# FSM design: A 5-step process

- 1. Understand the problem

- State diagram and state-transition table

- 2. Determine the machine's states

- Consider missing transitions: Will the machine start?

Minimize the state diagram: Reuse states where possible

- 3. Encode the states

- Encode states, outputs with a reasonable encoding choice

Consider the implementation target

- 4. Design the next-state logic

- Minimize the combinational logic

- Choices made in steps 2 & 3 affect the logic complexity

- 5. Implement the FSM

CSE370, Lecture 24

20