## Sequential logic implementation

- Implementation

- random logic gates and FFs

- programmable logic devices (PAL with FFs)

- Design procedure

- state diagrams

- state transition table

- state assignment

- next state functions

CSE370 - VIII - Sequential Logic Technology

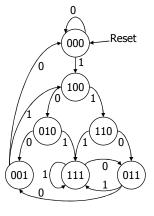

### Median filter FSM

Remove single 0s between two 1s (output = NS3)

| Ι                                                                                  | PS1              | PS2                                                           | PS3                        | NS1                                                                | NS2                        | NS3                   |

|------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------|----------------------------|--------------------------------------------------------------------|----------------------------|-----------------------|

| 0                                                                                  | 0                | 0                                                             | 0                          | 0                                                                  | 0                          | 0                     |

| 0                                                                                  | 0                | 0                                                             | 1                          | 0                                                                  | 0                          | 0                     |

| 0                                                                                  | 0                | 1                                                             | 0                          | 0                                                                  | 0                          | 1                     |

| 0                                                                                  | 0                | 1                                                             | 1                          | 0                                                                  | 0                          | 1                     |

| 0                                                                                  | 1                | 0                                                             | 0                          | 0                                                                  | 1                          | 0                     |

| 0                                                                                  | 1                | 0                                                             | 1                          | Χ                                                                  | Χ                          | Χ                     |

| 0                                                                                  | 1<br>1<br>1      | 0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0 | 1<br>0<br>1<br>0<br>1<br>0 | 0                                                                  | 0<br>0<br>0<br>1<br>X<br>1 | 1<br>0<br>X<br>1<br>1 |

| 0                                                                                  | 1                | 1                                                             | 1                          | 0                                                                  | 1                          | 1                     |

| 1                                                                                  | 0<br>0<br>0<br>0 | 0                                                             | 1<br>0<br>1<br>0<br>1      | 1                                                                  | 0<br>0                     | 0                     |

| 1                                                                                  | 0                | 0                                                             | 1                          | 1                                                                  | 0                          | 0                     |

| 1                                                                                  | 0                | 1                                                             | 0                          | 1                                                                  | 1                          | 1                     |

| 1                                                                                  | 0                | 1                                                             | 1                          | 1                                                                  | 1                          | 1<br>1                |

| 1                                                                                  | 1                | 0                                                             | 0                          | 1                                                                  | 1                          | 0                     |

| 1                                                                                  | 1                | 0                                                             | 0<br>1                     | Χ                                                                  | 1<br>X<br>1                | Χ                     |

| $\begin{array}{c} \underline{I} \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 1 \\ 1 \\ 1$ | 1                | 1                                                             | 0                          | 0<br>0<br>0<br>0<br>X<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>X<br>1 | 1                          | 1                     |

| 1                                                                                  | 1                | 1                                                             | 1                          | 1                                                                  | 1                          | 0<br>X<br>1<br>1      |

|                                                                                    |                  |                                                               |                            |                                                                    |                            |                       |

CSE370 - VIII - Sequential Logic Technology

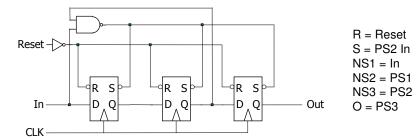

# Median filter FSM (cont'd)

Realized using the standard procedure and individual FFs and gates

| 0 0 1 0 0 0 1<br>0 0 1 1 0 0 0 1<br>0 1 1 0 0 0 1 NS |

|------------------------------------------------------|

| 0 0 1 1 0 0 1 NS                                     |

|                                                      |

|                                                      |

|                                                      |

| 0   1 0 1   X X X NS2                                |

| 0   1 1 0   0 1 1 NS3 =                              |

| 0   1 1 1   0 1 1 O = P                              |

| 1 0 0 0 1 0 0                                        |

| 1   0 0 1   1 0 0                                    |

| 1   0 1 0   1 1 1                                    |

| 1   0 1 1   1 1 1                                    |

| 1   1 0 0   1 1 0                                    |

| 1   1 0 1   X X X                                    |

| 1   1                                                |

| 1   1   1   1   1   1                                |

CSE370 - VIII - Sequential Logic Technology

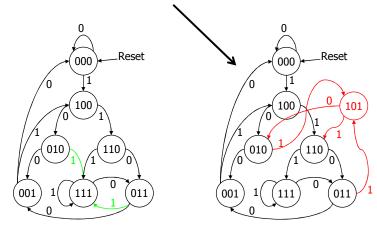

# Median filter FSM (cont'd)

But it looks like a shift register if you look at it right

CSE370 - VIII - Sequential Logic Technology

### Median filter FSM (cont'd)

An alternate implementation with S/R FFs

The set input (S) does the median filter function by making the next state 111 whenever the input is 1 and PS2 is 1 (1 input to state x1x)

CSE370 - VIII - Sequential Logic Technology

5

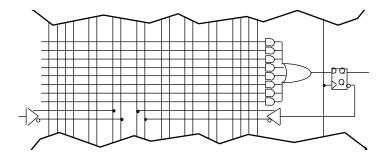

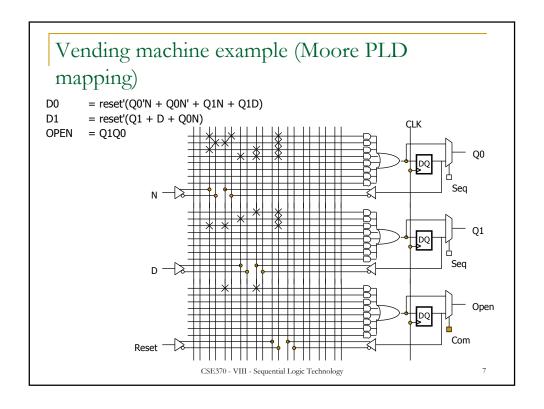

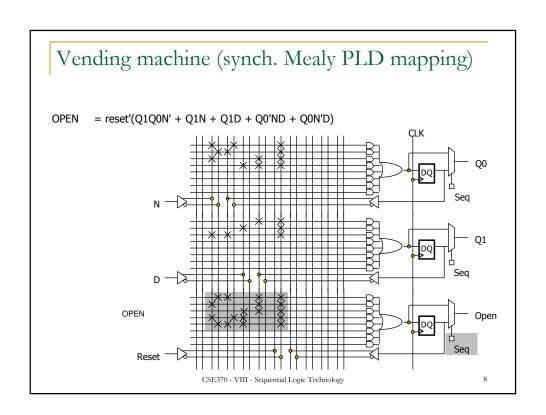

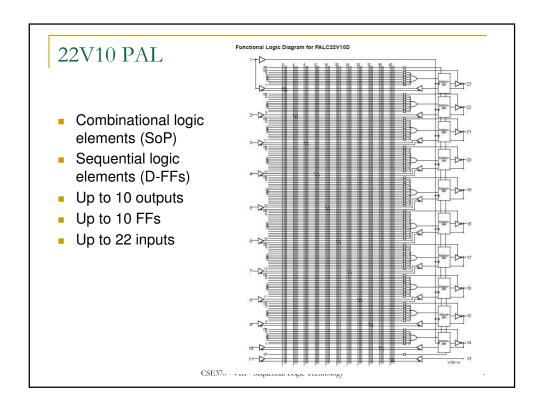

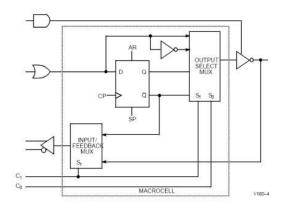

### Implementation using PALs

- Programmable logic building block for sequential logic

- macro-cell: FF + logic

- D-FF

- two-level logic capability like PAL (e.g., 8 product terms)

CSE370 - VIII - Sequential Logic Technology

### 22V10 PAL Macro Cell

Sequential logic element + output/input selection

CSE370 - VIII - Sequential Logic Technology

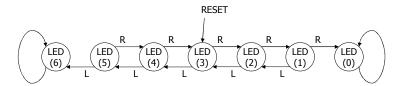

### Light Game FSM

- Tug of War game

- □ 7 LEDs, 2 push buttons (L, R)

CSE370 - VIII - Sequential Logic Technology

11

12

# Light Game FSM Verilog module Light\_Game (LEDS, LPB, RPB, CLK, RESET);

```

input LPB ;

input RPB ;

combinational logic

input CLK ;

wire L, R;

input RESET;

assign L = ~left && LPB;

output [6:0] LEDS;

assign R = ~right && RPB;

assign LEDS = position;

reg [6:0] position;

reg left;

reg right;

sequential logic

always @(posedge CLK)

begin

right <= RPB;

if (RESET) position <= 7'b0001000;</pre>

else if ((position == 7'b0000001) || (position == 7'b1000000));

else if (L) position <= position << 1;</pre>

else if (R) position <= position >> 1;

end

endmodule

```

CSE370 - VIII - Sequential Logic Technology

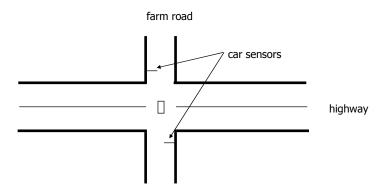

### Example: traffic light controller

- A busy highway is intersected by a little used farmroad

- Detectors C sense the presence of cars waiting on the farmroad

- u with no car on farmroad, light remain green in highway direction

- if vehicle on farmroad, highway lights go from Green to Yellow to Red, allowing the farmroad lights to become green

- these stay green only as long as a farmroad car is detected but never longer than a set interval

- when these are met, farm lights transition from Green to Yellow to Red, allowing highway to return to green

- even if farmroad vehicles are waiting, highway gets at least a set interval as green

- Assume you have an interval timer that generates:

- a short time pulse (TS) and

- a long time pulse (TL),

- □ in response to a set (ST) signal.

- TS is to be used for timing yellow lights and TL for green lights

CSE370 - VIII - Sequential Logic Technology

13

### Example: traffic light controller (cont')

Highway/farm road intersection

CSE370 - VIII - Sequential Logic Technology

### Example: traffic light controller (cont')

Tabulation of inputs and outputs

inputs description outputs description

reset place FSM in initial state C detect vehicle on the farm road TL long time interval expired

outputs description

Outputs description

HG, HY, HR assert green/yellow/red highway lights

FG, FY, FR assert green/yellow/red highway lights

ST start timing a short or long interval

Tabulation of unique states – some light configurations imply others

state description

HG highway green (farm road red)

HY highway yellow (farm road red)

FG farm road green (highway red)

FY farm road yellow (highway red)

CSE370 - VIII - Sequential Logic Technology

13

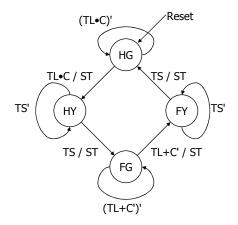

### Example: traffic light controller (cont')

State diagram

CSE370 - VIII - Sequential Logic Technology

### Example: traffic light controller (cont')

- Generate state table with symbolic states

- Consider state assignments

output encoding – similar problem to state assignment (Green = 00, Yellow = 01, Red = 10)

| Inputs |    |    | Present State | Next State | Outputs |        |        |

|--------|----|----|---------------|------------|---------|--------|--------|

| C .    | TL | TS |               |            | ST .    | Н      | F      |

| 0      | -  | _  | HG            | HG         | 0       | Green  | Red    |

| _      | 0  | _  | HG            | HG         | 0       | Green  | Red    |

| 1      | 1  | _  | HG            | HY         | 1       | Green  | Red    |

| _      | -  | 0  | HY            | HY         | 0       | Yellow | Red    |

| _      | _  | 1  | HY            | FG         | 1       | Yellow | Red    |

| 1      | 0  | _  | FG            | FG         | 0       | Red    | Green  |

| 0      | _  | -  | FG            | FY         | 1       | Red    | Green  |

| _      | 1  | _  | FG            | FY         | 1       | Red    | Green  |

| _      | -  | 0  | FY            | FY         | 0       | Red    | Yellow |

| _      | -  | 1  | FY            | HG         | 1       | Red    | Yellow |

|        |    |    | I             | I          |         |        |        |

CSE370 - VIII - Sequential Logic Technology

17

### Logic for different state assignments

```

SA1

NS1 = C \cdot TL' \cdot PS1 \cdot PS0 + TS \cdot PS1' \cdot PS0 + TS \cdot PS1' \cdot PS0' + C' \cdot PS1 \cdot PS0 + TL \cdot PS1' \cdot PS0 \\ NS0 = C \cdot TL \cdot PS1' \cdot PS0' + C \cdot TL' \cdot PS1' \cdot PS0 + PS1' \cdot PS0 \\

ST = C•TL•PS1'•PS0' + TS•PS1'•PS0 + TS•PS1*PS0' + C'•PS1*PS0 + TL•PS1*PS0

H1 = PS1

H0 = PS1'•PS0

F1 = PS1'

F0 = PS1•PS0

SA2

NS1 = C•TL•PS1' + TS'•PS1 + C'•PS1'•PS0

NS0 = TS•PS1•PS0' + PS1'•PS0 + TS'•PS1•PS0

ST = C•TL•PS1' + C'•PS1'•PS0 + TS•PS1

H1 = PS0

F1 = PS0'

H0 = PS1•PS0'

F0 = PS1 \cdot PS0

SA3

NS3 = C'•PS2 + TL•PS2 + TS'•PS3

NS1 = C•TL•PS0 + TS'•PS1

NS2 = TS•PS1 + C•TL'•PS2

NS0 = C'•PS0 + TL'•PS0 + TS•PS3

ST = C \cdot TL \cdot PS0 + TS \cdot PS1 + C \cdot PS2 + TL \cdot PS2 + TS \cdot PS3 + PS1 + PS3 + PS2 + PS1 + P

F1 = PS1 + PS0

```

CSE370 - VIII - Sequential Logic Technology

## Sequential logic implementation summary

- Models for representing sequential circuits

- finite state machines and their state diagrams

- Mealy, Moore, and synchronous Mealy machines

- Finite state machine design procedure

- deriving state diagram

- deriving state transition table

- assigning codes to states

- determining next state and output functions

- implementing combinational logic

- Implementation technologies

- random logic + FFs

- □ PAL with FFs (programmable logic devices PLDs)

CSE370 - VIII - Sequential Logic Technology