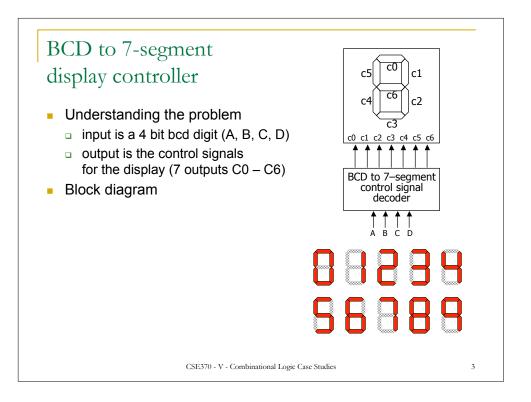

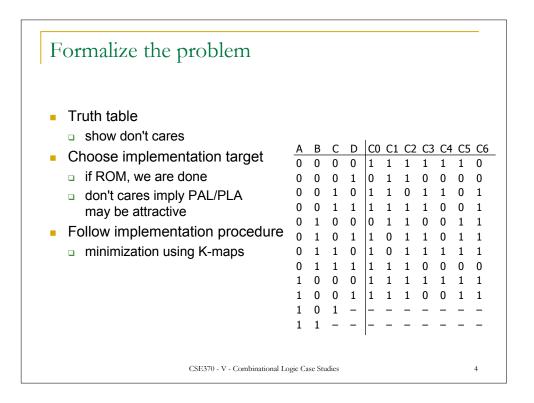

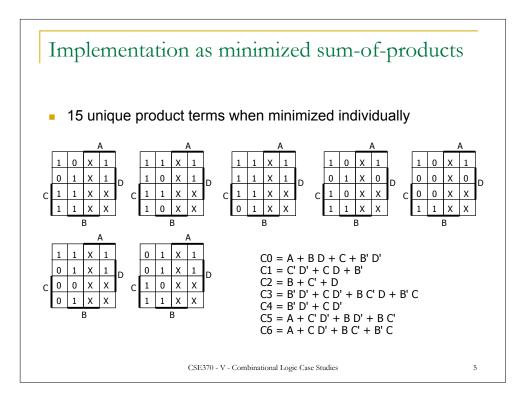

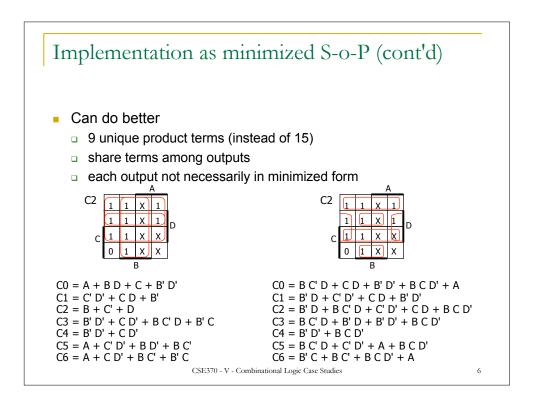

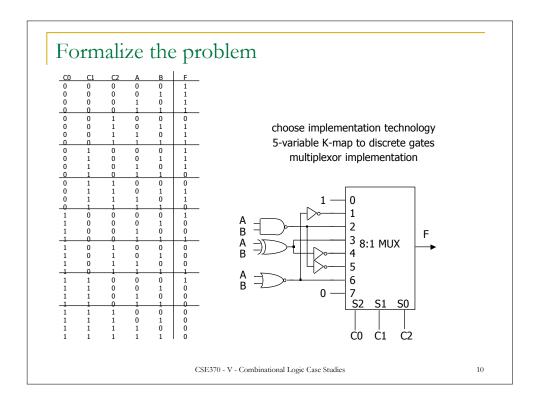

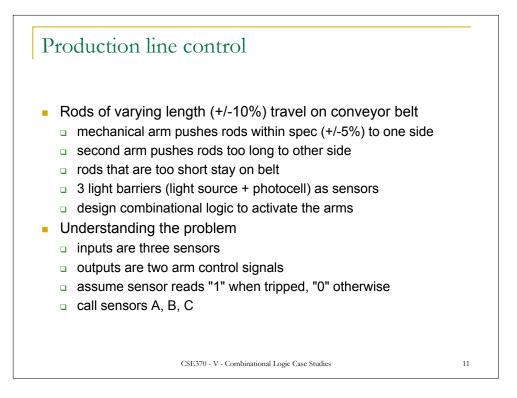

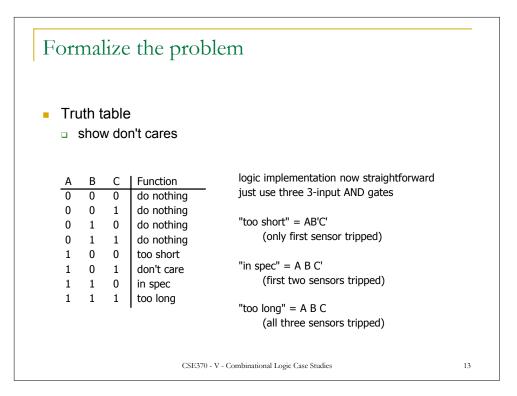

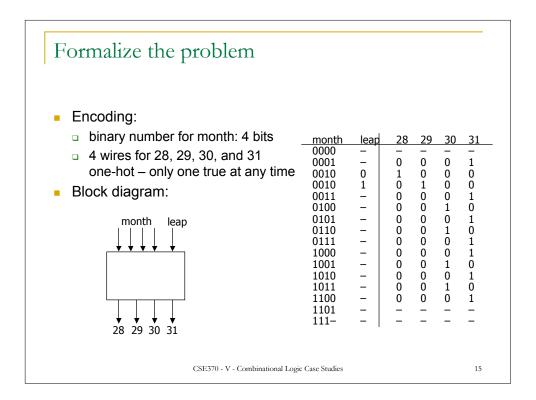

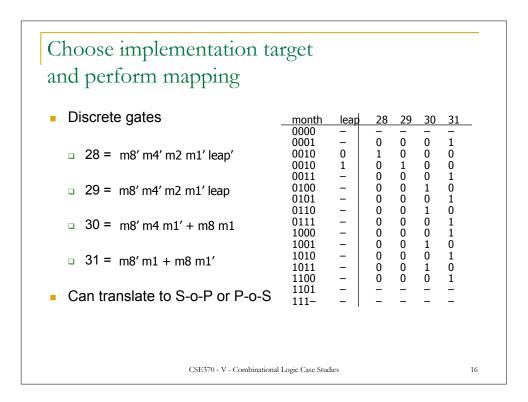

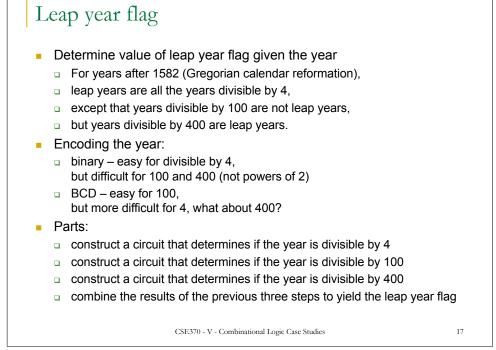

## General design procedure for combinational logic 1. Understand the problem what is the circuit supposed to do? write down inputs (data, control) and outputs draw block diagram or other picture 2. Formulate the problem using a suitable design representation • truth table or waveform diagram are typical may require encoding of symbolic inputs and outputs 3. Choose implementation target ROM, PAL, PLA mux, decoder and OR-gate discrete gates 4. Follow implementation procedure K-maps for two-level, multi-level design tools and hardware description language (e.g., Verilog) 2 CSE370 - V - Combinational Logic Case Studies