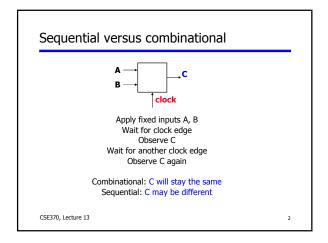

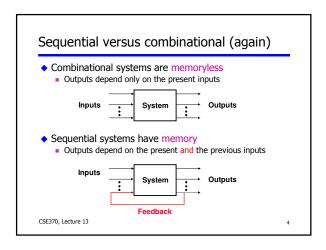

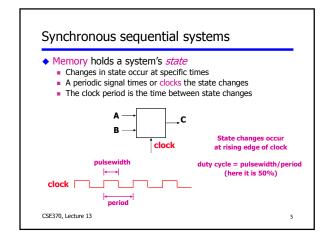

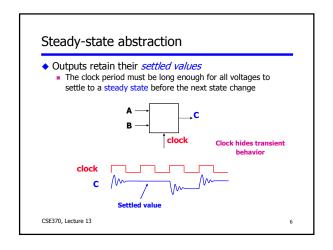

# Sequential logic Two types Synchronous = clocked Asynchronous = self-timed Has state State = memory Employs feedback Assumes steady-state signals Signals are valid after they have settled State elements hold their settled output values

## Example: A sequential system

- Door combination lock

- Enter 3 numbers in sequence and the door opens

- If there is an error the lock must be reset

- After the door opens the lock must be reset

- Inputs: Sequence of numbers, reset

- Outputs: Door open/close

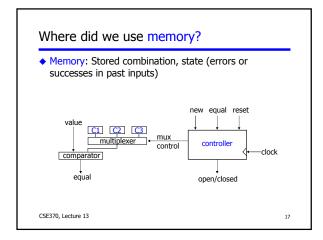

- Memory: Must remember the combination

CSE370, Lecture 13

70, Lecture 13

# Understand the problem Consider I/O and unknowns How many bits per input? How many inputs in sequence? How do we know a new input is entered? How do we represent the system states? new value reset

## Implement using sequential logic

- Behavior

- Clock tells us when to look at inputs

- ✔ After inputs have settledSequential: Enter sequence of numbers

- Sequential: Remember if error occurred

- ◆ Need a finite-state diagram

- Assume synchronous inputs

- State sequence

✓ Enter 3 numbers serially

✓ Remember if error occurred

- All states have outputs

- Lock open or closed

CSE370, Lecture 13

##

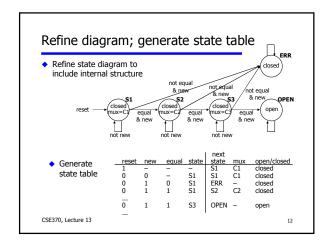

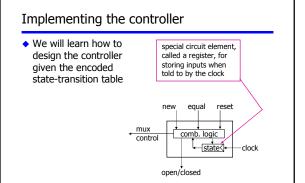

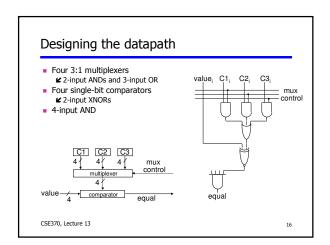

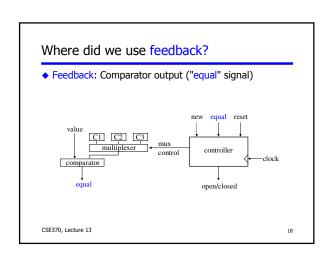

## Separate data path and control Data path Stores combination Compares inputs with combination State changes clocked CSE370, Lecture 13 Control Finite state-machine controller Control or data path State changes clocked

### Encode state table

- ◆ State can be: S1, S2, S3, OPEN, or ERR

- Need at least 3 bits to encode: 000, 001, 010, 011, 100

Can use 5 bits: 00001, 00010, 01000, 01000, 10000

Choose 4 bits: 0001, 0010, 0100, 1000, 0000

- Output to mux can be: C1, C2, or C3

- Need 2 or 3 bits to encode

Choose 3 bits: 001, 010, 100

- ◆ Output open/closed can be: Open or closed

- Need 1 or 2 bits to encode

- Choose 1 bit: 1, 0

CSE370, Lecture 13

CSE370, Lecture 13

13

15

## Encode state table (con't)

- Good encoding choice!

- Mux control is identical to last 3 state bits

- Open/closed is identical to first state bit

- $\,\blacksquare\,$  Output encoding  $\Rightarrow$  the outputs and state bits are the same

| reset | new | equal | state | next<br>state | mux | open/closed |

|-------|-----|-------|-------|---------------|-----|-------------|

| 1     | -   | -     | -     | 0001          | 001 | 0           |

| 0     | 0   | -     | 0001  | 0001<br>0001  | 001 | 0           |

| 0     | 1   | 0     |       | 0000          | _   | 0           |

| 0     | 1   | 1     | 0001  | 0010          | 010 | 0           |

| 0     | 1   | 1     | 0100  | 1000          | -   | 1           |

CSE370, Lecture 13

14

## Where did we use clock?

- ◆ Clock synchronizes the inputs

- Accept inputs when clock goes high

- ◆ Controller is clocked

- Mux-control and open/closed signals change on the clock edge

## Then next 5 weeks...

- ◆ We learn the details

- Latches, flip-flops, registersShift registers, countersState machines

- Timing and timing diagrams

Synchronous and asynchronous inputs

Metastability

- Clock skew

- Moore and Mealy machines

- One-hot encoding

- More...

CSE370, Lecture 13

20