## **Finite State Machines**

- - □ combinational logic

- ★ Models for representing sequential circuits

- ☐ finite-state machines (Moore and Mealy)

- 器 Basic sequential circuits revisited

- □ counters

- - □ next state functions

Winter 2001

CSE370 - VII - Finite State Machines

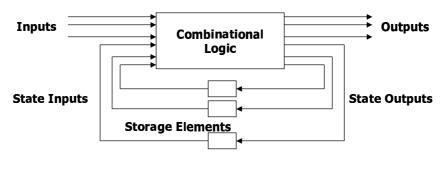

#### **Abstraction of state elements**

- ₩ Divide circuit into combinational logic and state

- ★ Implementation of storage elements leads to various forms of sequential logic

Winter 2001

CSE370 - VII - Finite State Machines

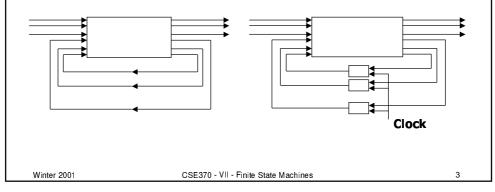

## Forms of sequential logic

- \*\* Asynchronous sequential logic state changes occur whenever state inputs change (elements may be simple wires or delay elements)

- Synchronous sequential logic state changes occur in lock step across all storage elements (using a periodic waveform the clock)

Synchronous sequential logic state changes occur in lock step across all storage elements (using a periodic waveform the clock)

Synchronous sequential logic state changes occur in lock step across all storage elements (using a periodic waveform the clock)

Synchronous sequential logic state changes occur in lock step across all storage elements (using a periodic waveform the clock)

Synchronous sequential logic state changes occur in lock step across all storage elements (using a periodic waveform the clock)

Synchronous sequential logic state changes occur in lock step across all storage elements (using a periodic waveform the clock)

Synchronous sequential logic state changes occur in lock step across all storage elements (using a periodic waveform the clock)

Synchronous sequential logic state changes occur in lock step across all storage elements (using a periodic waveform the clock)

Synchronous sequential logic state changes occur in lock step across all state all sta

## Finite state machine representations

- ★ States: determined by possible values in sequential storage elements

- 署 Transitions: change of state

- 第 Clock: controls when state can change by controlling storage elements

- ★ Sequential logic

- □ sequences through a series of states

- □ based on sequence of values on input signals

- □ clock period defines elements of sequence

Winter 2001

CSE370 - VII - Finite State Machines

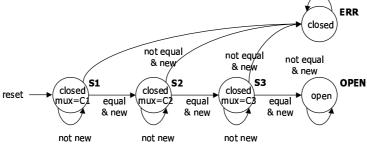

# Example finite state machine diagram

- ★ Combination lock from introduction to course

- △ 5 states

- □ 5 self-transitions + 1 reset to state S1

- △ 6 transitions + 4 resets

Winter 2001

CSE370 - VII - Finite State Machines

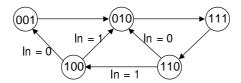

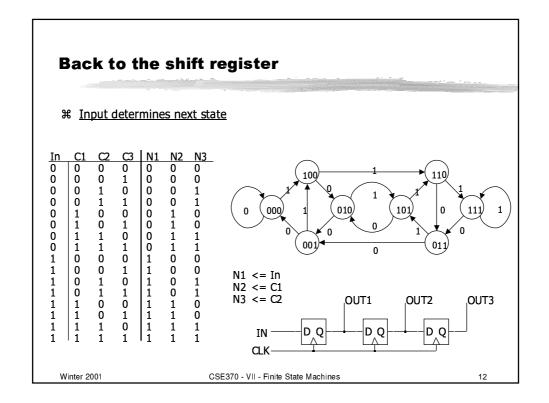

# Can any sequential system be represented with a state diagram?

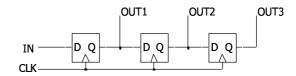

- 第 Shift register

- ☐ output values shown within state node

Winter 2001

CSE370 - VII - Finite State Machines

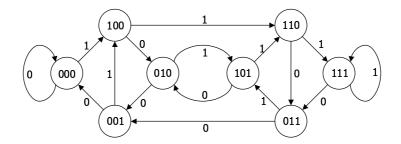

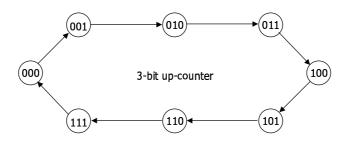

## Counters are simple finite state machines

#### 業 Counters

△ proceed through well-defined sequence of states in response to enable

#### ₩ Many types of counters: binary, BCD, Gray-code

- △ 3-bit up-counter: 000, 001, 010, 011, 100, 101, 110, 111, 000, ...

- △ 3-bit down-counter: 111, 110, 101, 100, 011, 010, 001, 000, 111, ...

Winter 2001

CSE370 - VII - Finite State Machines

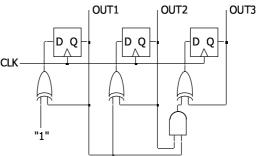

## How do we turn a state diagram into logic?

#### **光** Counter

- ☐ 3 flip-flops to hold state

- □ logic to compute next state

- ☐ clock signal controls when flip-flop memory can change

- ⊠wait long enough for combinational logic to compute new value

- ☑don't wait too long as that is low performance

Winter 2001

CSE370 - VII - Finite State Machines

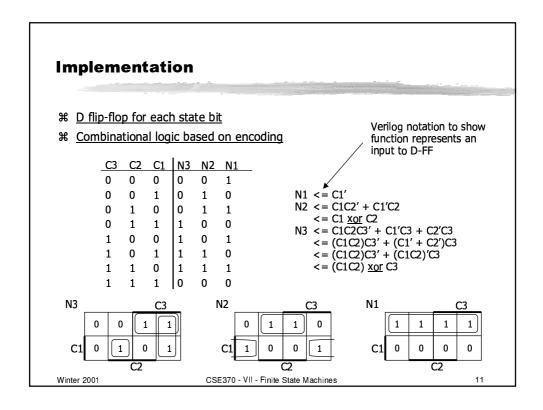

## FSM design procedure

#### 第 Start with counters

- □ simple because output is just state

#### ★ State diagram to state transition table

- □ tabular form of state diagram

- □ like a truth-table

#### 業 State encoding

- □ decide on representation of states

- ☐ for counters it is simple: just its value

####

- ☐ flip-flop for each state bit

- □ combinational logic based on encoding

Winter 2001

CSE370 - VII - Finite State Machines

С

# FSM design procedure: state diagram to encoded state transition table

- 署 Tabular form of state diagram

- ★ Like a truth-table (specify output for all input combinations)

| cur | rent state | next state |   |  |

|-----|------------|------------|---|--|

| 0   | 000        | 001        | 1 |  |

| 1   | 001        | 010        | 2 |  |

| 2   | 010        | 011        | 3 |  |

| 3   | 011        | 100        | 4 |  |

| 4   | 100        | 101        | 5 |  |

| 5   | 101        | 110        | 6 |  |

| 6   | 110        | 111        | 7 |  |

| 7   | 111        | 000        | 0 |  |

Winter 2001

CSE370 - VII - Finite State Machines

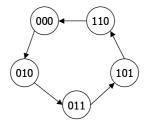

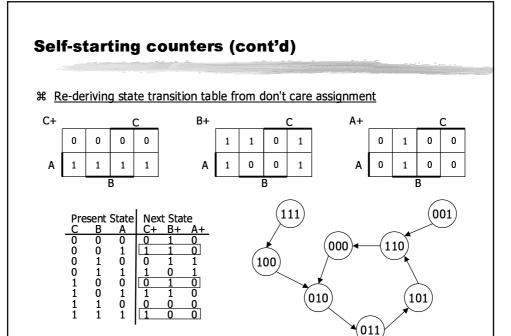

## More complex counter example

第 Complex counter

△ repeats 5 states in sequence

□ not a binary number representation

₩ Step 1: derive the state transition diagram

△ count sequence: 000, 010, 011, 101, 110

第 Step 2: derive the state transition table from the state transition diagram

| Pre<br>C | sent :<br>B | State<br>A | Nex<br>C+ | t Stat<br>B+ | te<br>A+_ |

|----------|-------------|------------|-----------|--------------|-----------|

| 0        | 0           | 0          | 0         | 1            | 0         |

| 0        | 0           | 1          | -         | _            | _         |

| 0        | 1           | 0          | 0         | 1            | 1         |

| 0        | 1           | 1          | 1         | 0            | 1         |

| 1        | 0           | 0          | _         | _            | _         |

| 1        | 0           | 1          | 1         | 1            | 0         |

| 1        | 1           | 0          | 0         | 0            | 0         |

| 1        | 1           | 1          | _         | -            | _         |

note the don't care conditions that arise from the unused state codes

Winter 2001

CSE370 - VII - Finite State Machines

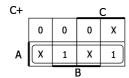

# More complex counter example (cont'd)

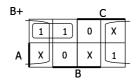

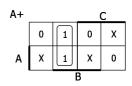

★ Step 3: K-maps for next state functions

$$B+ <= B' + A'C'$$

$$A+ <= BC'$$

Winter 2001

CSE370 - VII - Finite State Machines

14

CSE370 - VII - Finite State Machines

15

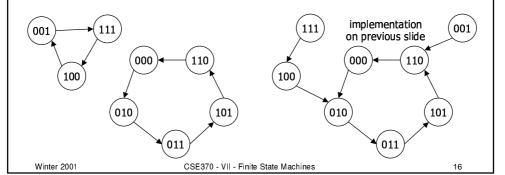

## **Self-starting counters**

####

Winter 2001

$\hfill \triangle$  at power-up, counter may be in an unused or invalid state

△ designer must guarantee that it (eventually) enters a valid state

#### ★ Self-starting solution

riangle design counter so that invalid states eventually transition to a valid state riangle may limit exploitation of don't cares

| Activity                                                                                                                                                              |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <ul> <li>         2-bit up-down counter (2 inputs)         □ direction: D = 0 for up, D = 1 for down         □ count: C = 0 for hold, C = 1 for count     </li> </ul> |    |

|                                                                                                                                                                       |    |

|                                                                                                                                                                       |    |

|                                                                                                                                                                       |    |

| Winter 2001 CSE370 - VII - Finite State Machines                                                                                                                      | 17 |

| Activity (cont'd) |                                      |    |

|-------------------|--------------------------------------|----|

|                   |                                      |    |

|                   |                                      |    |

|                   |                                      |    |

|                   |                                      |    |

|                   |                                      |    |

|                   |                                      |    |

|                   |                                      |    |

|                   |                                      |    |

|                   |                                      |    |

|                   |                                      |    |

|                   |                                      |    |

| Winter 2001       | CSE370 - VII - Finite State Machines | 18 |

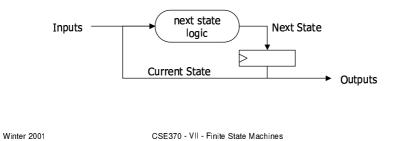

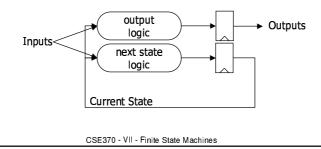

## Counter/shift-register model

- ★ Combinational logic computes:

□ next state

☑function of current state and inputs

Outputs

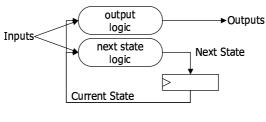

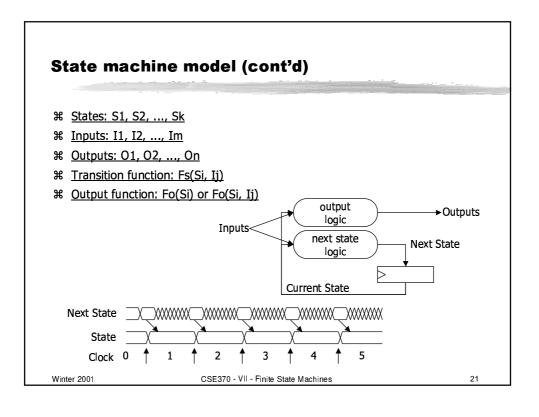

#### **General state machine model**

- 署 Values stored in registers represent the state of the circuit

- 第 Combinational logic computes:

□ next state

☑function of current state and inputs

Outputs

Outputs

☑function of current state and inputs (Mealy machine) ☑function of current state only (Moore machine)

Winter 2001

CSE370 - VII - Finite State Machines

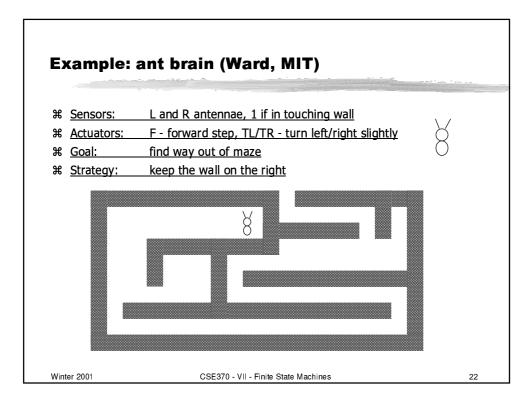

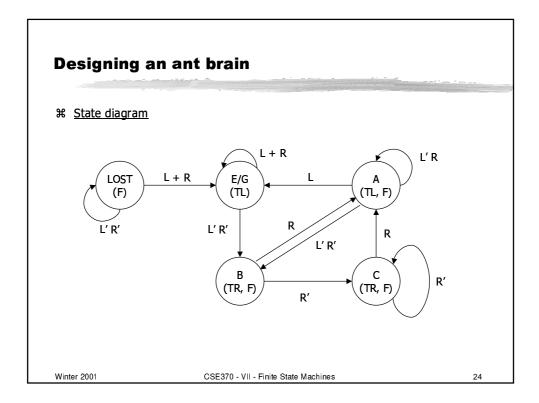

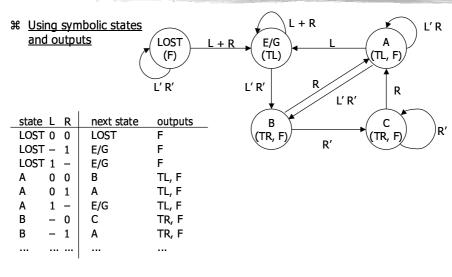

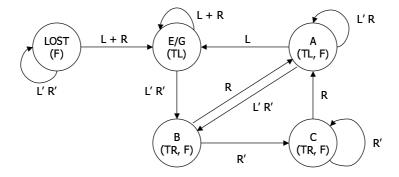

## Synthesizing the ant brain circuit

- 第 Encode states using a set of state variables

- △ arbitrary choice may affect cost, speed

- 策 Use transition truth table

- ☐ define next state function for each state variable

- △ define output function for each output

- 第 Implement next state and output functions using combinational logic

- △ 2-level logic (ROM/PLA/PAL)

- □ next state and output functions can be optimized together

Winter 2001

CSE370 - VII - Finite State Machines

25

## **Transition truth table**

Winter 2001

CSE370 - VII - Finite State Machines

## **Synthesis**

$\sharp$  5 states : at least 3 state variables required (X, Y, Z) LOST - 000  $\bigtriangleup$  state assignment (in this case, arbitrarily chosen) E/G - 001 A - 010 B - 011 C - 100

state

L R

next state

outputs

X,Y,Z

X+, Y+, Z+

F TR TL

0 0 0 0 0 0

0 0 0

1 0 0

it now remains X,Y,Z to synthesize these 6 functions ... ...... 010 01 010 010 10 001 101 010 11 001 101 1 1 0 011 0 1 010 1 1 0

Winter 2001 CSE370 - VIII - Finite State Machines

... ...

## Synthesis of next state and output functions

27

| state inputs  X,Y,Z L R  0 0 0 0 0  0 0 0 - 1  0 0 1 - 1  0 0 1 1 -  0 1 0 0 0  0 1 0 1 -  0 1 0 0 1  0 1 0 1 -  0 1 1 - 0  0 1 1 - 1  1 0 0 - 0  1 0 0 - 1 | next state     X+,Y+,Z+     0 0 0     0 0 1     0 1 1     0 1 0     0 1 1     0 1 0     0 1 1     0 1 0     0 1 1     0 1 0     0 1 1     0 0 0 1     1 0 0     0 1 0     1 0 0     0 1 0     1 0 0     0 1 0 | outputs F TR TL  1 0 0 1 0 0 1 0 0 0 0 1 0 0 1 0 0 1 1 0 1 1 0 1 1 1 0 1 1 1 0 1 1 0 1 1 0 1 1 0 1 1 0 1 1 0 | e.g.<br>TR = X + Y Z<br>X+ = X R' + Y Z R' = R' TR |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|                                                                                                                                                             |                                                                                                                                                                                                               |                                                                                                              |                                                    |

Winter 2001 CSE370 - VII - Finite State Machines

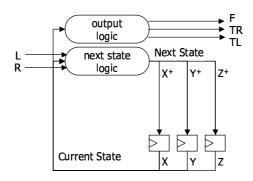

## **Circuit implementation**

第 Outputs are a function of the current state only - Moore machine

Winter 2001

CSE370 - VII - Finite State Machines

## Don't cares in FSM synthesis

- ₩ What happens to the "unused" states (101, 110, 111)?

- ※ They were exploited as don't cares to minimize the logic

△ if the states can't happen, then we don't care what the functions do

△ if states do happen, we may be in trouble

Winter 2001

CSE370 - VII - Finite State Machines

#### **State minimization**

- 第 Fewer states may mean fewer state variables

- ₩ High-level synthesis may generate many redundant states

- **X** Two state are equivalent if they are impossible to distinguish from the outputs of the FSM, i. e., for any input sequence the outputs are the same

- 署 Two conditions for two states to be equivalent:

- □ 1) output must be the same in both states

Winter 2001

CSE370 - VII - Finite State Machines

31

#### Ant brain revisited

★ Any equivalent states?

Winter 2001

CSE370 - VII - Finite State Machines

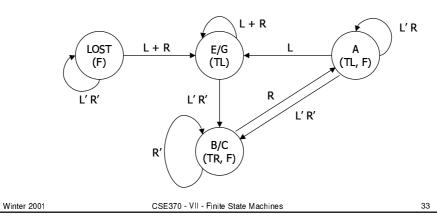

# New improved brain

- ₩ Behavior is exactly the same as the 5-state brain

- ₩ We now need only 2 state variables rather than 3

# New brain implementation

Winter 2001

| state | inputs | next st | ate outputs | v v                                                  |

|-------|--------|---------|-------------|------------------------------------------------------|

| X,Y   | LR     | X+,Y+   | F TRTL      | $X^+ \underline{X} Y^+ \underline{X}$                |

| 0 0   | 0 0    | 0 0     | 1 0 0       | $egin{array}{ c c c c c c c c c c c c c c c c c c c$ |

| 0 0   | - 1    | 0 1     | 100         | 0 0 1 1 1   R   1 0 0 0 1   R                        |

| 0 0   | 1 -    | 0 1     | 100         |                                                      |

| 0 1   | 0 0    | 1 1     | 0 0 1       | <u>Y</u> <u>Y</u> <u>Y</u>                           |

| 0 1   | - 1    | 0 1     | 0 0 1       | I I                                                  |

| 0 1   | 1 -    | 0 1     | 0 0 1       |                                                      |

| 10    | 0 0    | 1 1     | 101         | F <u>X</u> TR X TL                                   |

| 10    | 0 1    | 10      | 101         | 1 0 1 1 0 0 1 0 0 1                                  |

| 10    | 1 -    | 0 1     | 101         | 1 0 1 1   R                                          |

| 11    | - 0    | 1 1     | 1 1 0       |                                                      |

| 11    | - 1    | 10      | 1 1 0       |                                                      |

|       | ,      |         |             | Y                                                    |

|       |        |         |             |                                                      |

CSE370 - VII - Finite State Machines

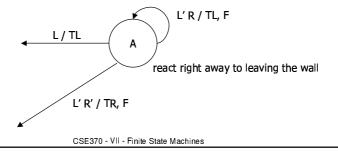

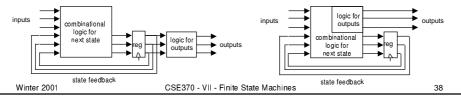

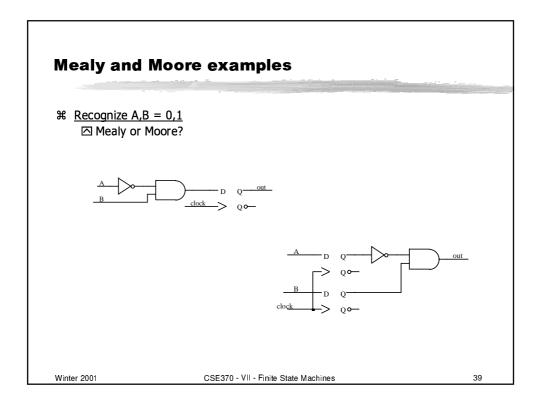

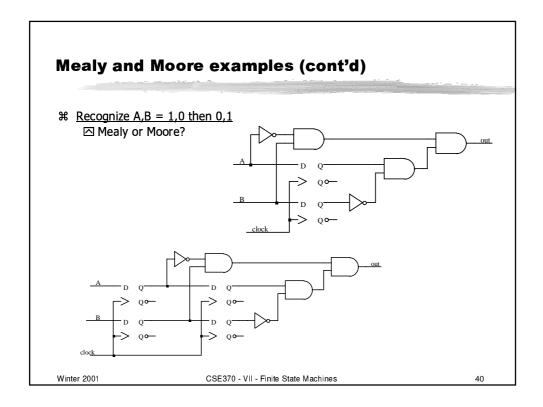

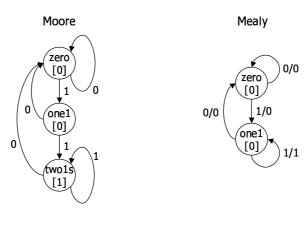

## Mealy vs. Moore machines

- 器 Mealy: outputs may depend on current state and current inputs

- ₩ We could have specified a Mealy FSM

□ outputs have immediate reaction to inputs

△ as inputs change, so does next state, doesn't commit until clocking event

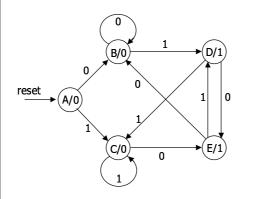

## **Specifying outputs for a Moore machine**

★ Output is only function of state

△ specify in state bubble in state diagram

△ example: sequence detector for 01 or 10

|       |       | current | next  |        |

|-------|-------|---------|-------|--------|

| reset | input | state   | state | output |

| 1     | _     | _       | Α     |        |

| 0     | 0     | Α       | В     | 0      |

| 0     | 1     | Α       | С     | 0      |

| 0     | 0     | В       | В     | 0      |

| 0     | 1     | В       | D     | 0      |

| 0     | 0     | С       | Е     | 0      |

| 0     | 1     | С       | С     | 0      |

| 0     | 0     | D       | Е     | 1      |

| 0     | 1     | D       | С     | 1      |

| 0     | 0     | E       | В     | 1      |

| 0     | 1     | E       | D     | 1      |

Winter 200

Winter 2001

CSE370 - VII - Finite State Machines

## Specifying outputs for a Mealy machine

- ₩ Output is function of state and inputs

- □ specify output on transition arc between states

- △ example: sequence detector for 01 or 10

|       |       | current | next  |        |

|-------|-------|---------|-------|--------|

| reset | input | state   | state | output |

| 1     | _     | _       | Α     | 0      |

| 0     | 0     | Α       | В     | 0      |

| 0     | 1     | Α       | С     | 0      |

| 0     | 0     | В       | В     | 0      |

| 0     | 1     | В       | С     | 1      |

| 0     | 0     | С       | В     | 1      |

| 0     | 1     | С       | С     | 0      |

|       |       |         |       |        |

Winter 2001

CSE370 - VII - Finite State Machines

37

## **Comparison of Mealy and Moore machines**

- - $\triangle$  different outputs on arcs (n^2) rather than states (n)

- - △ outputs change at clock edge (always one cycle later)

- - ☐ react in same cycle don't need to wait for clock

- △ in Moore machines, more logic may be necessary to decode state into outputs more gate delays after

## **Registered Mealy machine (really Moore)**

- ★ Synchronous (or registered) Mealy machine

- ☐ registered state AND outputs

- □ avoids 'glitchy' outputs

- △ easy to implement in PLDs

- - △ outputs computed on transition to next state rather than after entering

- □ view outputs as expanded state vector

# Hardware Description Languages and Sequential Logic

¥ Flip-flops

Winter 2001

- □ representation of clocks timing of state changes

- □ asynchronous vs. synchronous

- ₩ FSMs

- △ behavioral view (synthesis of sequencers not in this course)

- ☆ Data-paths = data computation (e.g., ALUs, comparators) + registers

- □ use of arithmetic/logical operators

- □ control of storage elements

# Example: reduce-1-string-by-1

★ Remove one 1 from every string of 1s on the input

Winter 2001 CSE370 - VII - Finite State Machines

## **Verilog FSM - Reduce 1s example**

####

Winter 2001

CSE370 - VII - Finite State Machines

44

#### Moore Verilog FSM (cont'd) always @(in or state) ← crucial to include case (state) all signals that are `zero: input to state determination // last input was a zero begin if (in) next\_state = `onel; else next\_state = `zero; end note that output `one1: // we've seen one 1 depends only on state begin if (in) next\_state = `two1s; else next\_state = `zero; end `two1s: always @(state) // we've seen at least 2 ones case (state) begin `zero: out = 0; `one1: out = 0; `two1s: out = 1; if (in) next\_state = `two1s; else next\_state = `zero; endcase endcase endmodule Winter 2001 CSE370 - VII - Finite State Machines 45

#### **Mealy Verilog FSM** module reduce (clk, reset, in, out); input clk, reset, in; output out; reg out; reg state; // state variables reg next\_state; 0/0 zero \_[0] always @(in or state) case (state) 1/0 0/0 // last input was a zero `zero: begin out = 0; if (in) next\_state = `one; else next\_state = `zero; one1 [0] `one: if (in) begin // we've seen one 1 next\_state = `one; out = 1; end else begin next\_state = `zero; out = 0; endcase endmodule Winter 2001 CSE370 - VII - Finite State Machines

## **Synchronous Mealy Machine**

```

module reduce (clk, reset, in, out);

input clk, reset, in;

output out;

reg out;

reg state; // state variables

always @(posedge clk)

if (reset) state = `zero;

else

else

case (state)

`zero: // last input was a zero

begin

out = 0;

if (in) state = `one;

else state = `zero;

end

// we've seen one 1

`one:

if (in) begin

state = `one; out = 1;

end else begin

state = `zero; out = 0;

end

endcase

endmodule

```

Winter 2001

CSE370 - VII - Finite State Machines

47

## **Sequential logic implementation summary**

- - △ abstraction of sequential elements

- ☐ finite state machines and their state diagrams

- - □ deriving state diagram

- □ deriving state transition table

- △ determining next state and output functions

Winter 2001

CSE370 - VII - Finite State Machines