Page 2

## Generate a Sine Tone Digitally (2)

- Compute the sine tone once, store it in a table, and have all oscillators look in the table for needed values.

- Advantages: Much more efficient, hence faster, for the computer. You are not, literally, re-inventing the wheel every time.

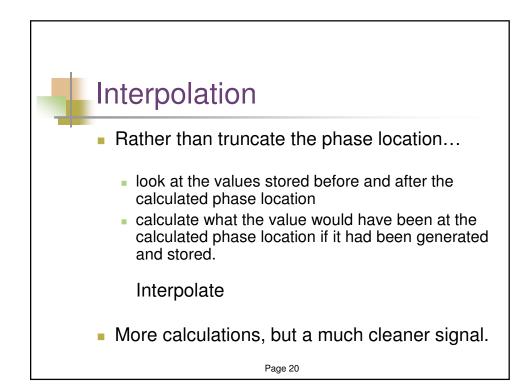

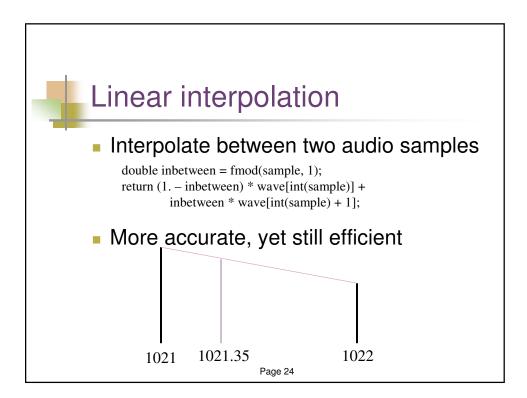

- Disadvantages: Table values are discrete points in time. Most times you will need a value that falls somewhere in between two already computed values.

Page 15

Page 31

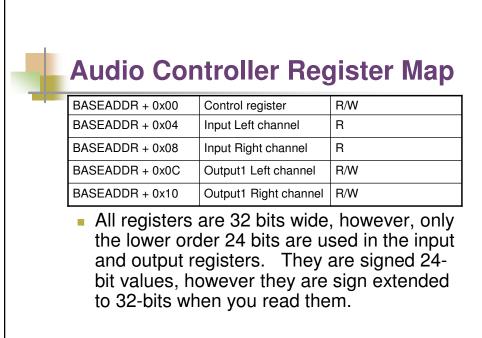

| BASEADDR + 0x00                                                                    | Control register                                                                                                                                                   | gister Map                                                                         |

|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| BASEADDR + 0x04                                                                    | Input Left channel                                                                                                                                                 | R                                                                                  |

| BASEADDR + 0x08                                                                    | Input Right channel                                                                                                                                                | R                                                                                  |

| BASEADDR + 0x0C                                                                    | Output1 Left channel                                                                                                                                               | R/W                                                                                |

| BASEADDR + 0x10                                                                    | Output1 Right channel                                                                                                                                              | R/W                                                                                |

| order bit (0x0000<br>codec. It is tied to<br>the interrupt enab<br>generated every | flags in the control regi<br>0001) is the enable bit<br>o the PDN pin. The nex<br>ole. When this is high, a<br>time the codec is ready<br>leared by writing or rea | and enables the<br>t bit (0x00000002) is<br>an interrupt is<br>t for a new sample. |

| Lab- Main                                                                                                                                                                                                                                                      |       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| int main()                                                                                                                                                                                                                                                     |       |

| /* TODO: initialization code should go here */                                                                                                                                                                                                                 |       |

| curr_value = 0;<br>climbing = 1;                                                                                                                                                                                                                               |       |

| /* register for the interrupts */<br>XInto_InterruptVectorTable[0].Handler = audio_interrupt_hand<br>XInto_InterruptVectorTable[0].CallBackRef = NULL;<br>XInto_mEnableIntr(XPAR_INTC_SINGLE_BASEADDR, XPAF<br>XInto_mMasterEnable(XPAR_INTC_SINGLE_BASEADDR); | ,     |

| /* globally enable the interrupts on the microblaze */ microblaze_enable_interrupts();                                                                                                                                                                         |       |

| /* enable the audio codec and make it interrupt me every tin<br>XAudio_mSetControlReg(XPAR_AUDIO_BASEADDR, AUDIO_AUDIO_CR_ENABLE_MASK);                                                                                                                        |       |

| for(;;)<br>{<br>/* do nothing, just let the interrupts handle the rest of the wor<br>}                                                                                                                                                                         | rk */ |

| return 0; /* never reached */ } Page 35                                                                                                                                                                                                                        |       |

| Page 35                                                                                                                                                                                                                                                        |       |