## **Cache Coherency**

#### **Cache coherent processors**

- · most current value for an address is the last write

- · all reading processors must get the most current value

#### Cache coherency problem

• update from a writing processor is not known to other processors

#### Cache coherency protocols

- · mechanism for maintaining cache coherency

- · coherency state associated with a cache block of data

- bus/interconnect operations on shared data change the state

- · for the processor that initiates an operation

- for other processors that have the data of the operation resident in their caches

Autumn 2006 CSE P548 - Cache Coherence

### **Cache Coherency Protocols**

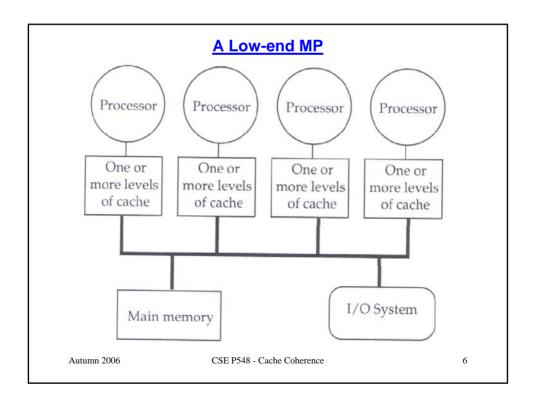

#### Write-invalidate

(Sequent, SGI, Sun)

- processor obtains exclusive access for writes (becomes the "owner") by invalidating data in other processors' caches

- coherency miss (invalidation miss)

- · cache-to-cache transfers

- good for:

- multiple writes to same word or block by one processor

3

· migratory sharing from processor to processor

Autumn 2006 CSE P548 - Cache Coherence

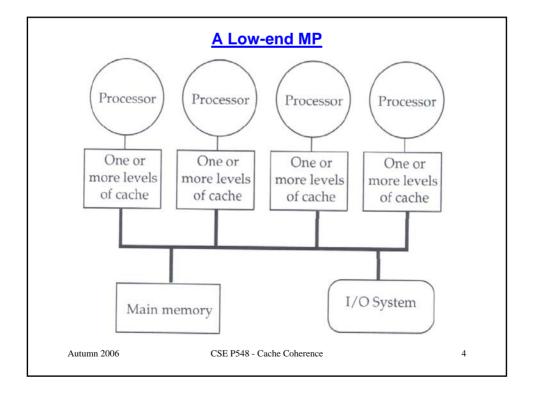

# **Cache Coherency Protocols**

### Write-update

(SPARCCenter 2000)

- · broadcast each write to actively shared data

- each processor with a copy snoops/takes the data

- good for inter-processor contention

We will focus on write-invalidate.

Autumn 2006

CSE P548 - Cache Coherence

5

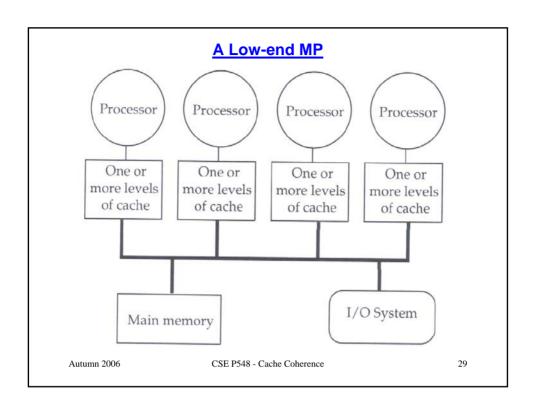

# **Cache Coherency Protocol Implementations**

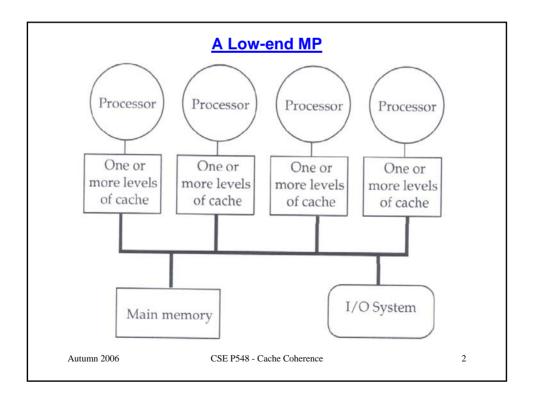

### **Snooping**

- · used with low-end MPs

- few processors

- · centralized memory

- bus-based

- distributed implementation: responsibility for maintaining coherence lies with each cache

### **Directory-based**

- · used with higher-end MPs

- · more processors

- · distributed memory

- · multi-path interconnect

- centralized for each address: responsibility for maintaining coherence lies with the directory for each address

Autumn 2006

CSE P548 - Cache Coherence

7

# **Snooping Implementation**

A distributed coherency protocol

- · coherency state associated with each cache block

- · each snoop maintains coherency for its own cache

Autumn 2006

CSE P548 - Cache Coherence

### **Snooping Implementation**

#### How the bus is used

- · broadcast medium

- entire coherency operation is atomic wrt other processors

- keep-the-bus protocol: master holds the bus until the entire operation has completed

- split-transaction buses:

- · request & response are different phases

- state value that indicates that an operation is in progress

- do not initiate another operation for a cache block that has one in progress

Autumn 2006

CSE P548 - Cache Coherence

9

# **Snooping Implementation**

#### Snoop implementation:

- · snoop on the highest level cache

- another reason L2 is physically-accessed

- property of inclusion:

- all blocks in L1 are in L2

- therefore only have to snoop on L2

- may need to update L1 state if change L2 state

- separate tags & state for snoop lookups

- processor & snoop communicate for a state or tag change

Autumn 2006

CSE P548 - Cache Coherence

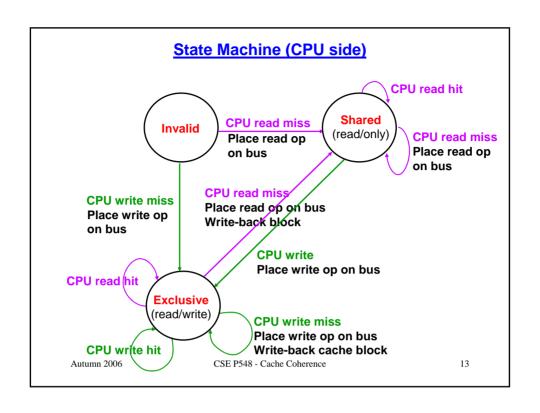

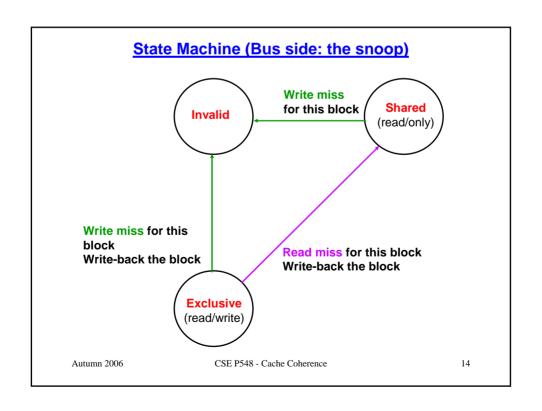

### **An Example Snooping Protocol**

#### Invalidation-based coherency protocol

Each cache block is in one of three states

- shared:

- · clean in all caches & up-to-date in memory

- block can be read by any processor

- exclusive:

- · dirty in exactly one cache

- only that processor can write to it (it's the owner of the block)

- invalid:

- · block contains no valid data

Autumn 2006

CSE P548 - Cache Coherence

11

### **State Transitions for a Given Cache Block**

State transitions caused by:

- events caused by the requesting processor, e.g.,

- · read miss, write miss, write on shared block

- · events caused by snoops of other caches, e.g.,

- read miss by P1 makes P2's owned block change from exclusive to shared

- write miss by P1 makes P2's owned block change from exclusive to invalid

Autumn 2006

CSE P548 - Cache Coherence

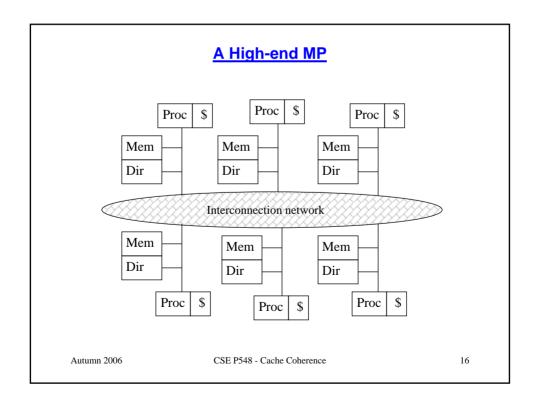

### **Directory Implementation**

#### Distributed memory machine

- processor-memory pairs are connected via a multi-path interconnection network

- · point-to-point communication

- snooping with broadcasting is wasteful of the parallel communication capability

- · each processor (or cluster of processors) has its own memory

- a processor has fast access to its local memory & slower access to "remote" memory located at other processors

- NUMA (non-uniform memory access) machines

Autumn 2006 CSE P548 - Cache Coherence

15

### **Coherence on High-end Machines**

How cache coherency is handled

- no caches (1st Cray MTA)

- disallow caching of shared data (Cray 3TD)

- software coherence (research machines)

- hardware directories that record cache block state (most others)

Autumn 2006

CSE P548 - Cache Coherence

17

### **Directory Implementation**

Coherency state is associated with memory blocks that are the size of cache blocks

- · directory tracks state of cache blocks

- shared:

- at least 1 processor has the data cached & memory is upto-date

- · block can be read by any processor

- exclusive:

- 1 processor (the owner) has the data cached & memory is stale

- · only that processor can write to it

- invalid:

- no processor has the data cached & memory is up-to-date

- · directory tracks shared memory blocks

- bit vector in which 1 means the processor has cached the data

- · write bit to indicate if exclusive

Autumn 2006

CSE P548 - Cache Coherence

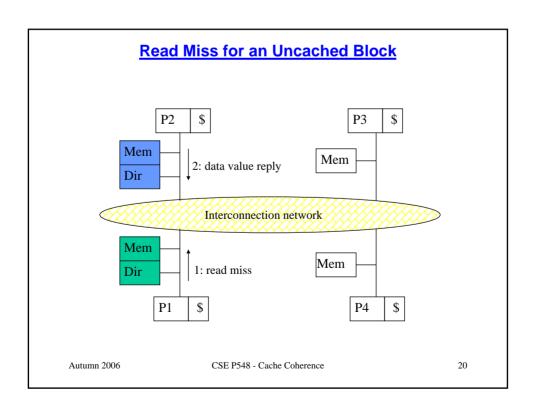

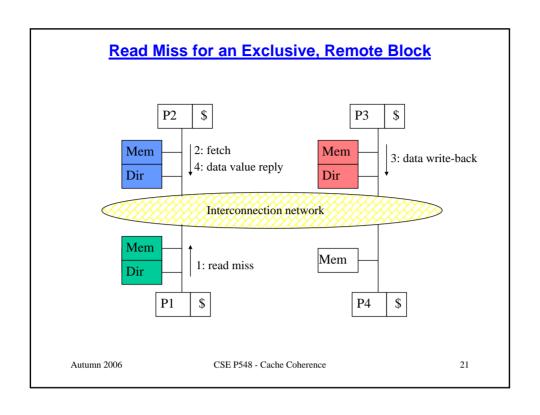

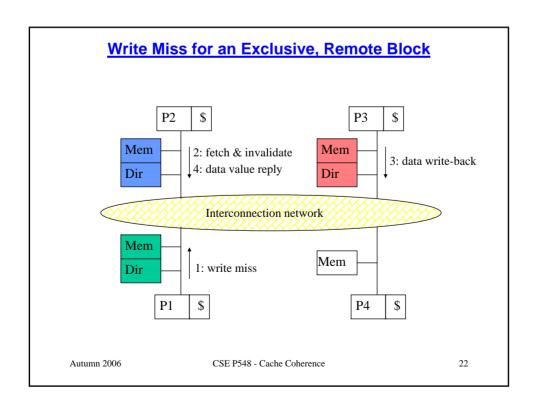

## **Directory Implementation**

Directory blocks play different roles during a memory operation

- home node: the memory location of the requested data

- · local node: where the memory request initiated

- remote node: an alternate location for the data if this processor has requested & cached it

In satisfying a memory request:

- messages sent between the different types of nodes in point-topoint communication

- · messages get explicit replies

Some simplifying assumptions for using the protocol

- · processor blocks until the access is complete

- · messages processed in the order received

Autumn 2006 CSE P548 - Cache Coherence

19

### **Directory Protocol Messages**

Message typeSourceDestinationMsg ContentRead missLocal cacheHome directoryP, A

Processor P reads data at address A;

make P a read sharer and arrange to send data back

Write miss Local cache Home directory P, A

- Processor P writes data at address A;

make P the exclusive owner and arrange to send data back

Invalidate Home directory Remote caches A

- Invalidate a shared copy at address A.

Fetch Home directory Remote cache A

- Fetch the block at address A and send it to its home directory

Fetch/Invalidate Home directory Remote cache A

Fetch the block at address A and send it to its home directory; invalidate the block in the cache

Data value reply Home directory Local cache Data

- Return a data value from the home memory (read or write miss response)

Data write-back Remote cache Home directory A, Data

- Write-back a data value for address A (invalidate response)

Autumn 2006 CSE P548 - Cache Coherence 23

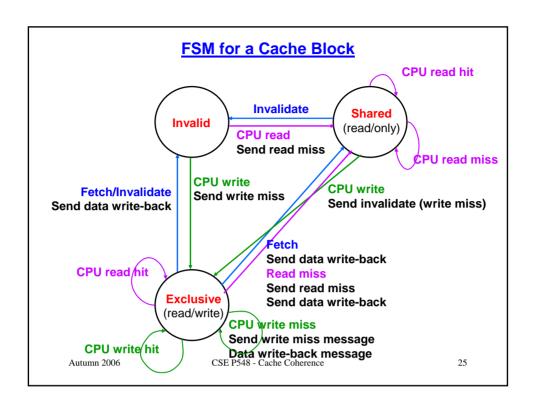

### **CPU FSM for a Cache Block**

States identical to the snooping protocol

Transactions very similar

- · read & write misses sent to home directory

- invalidate & data fetch requests to the node with the data replace broadcasted read/write misses

Autumn 2006 CSE P548 - Cache Coherence

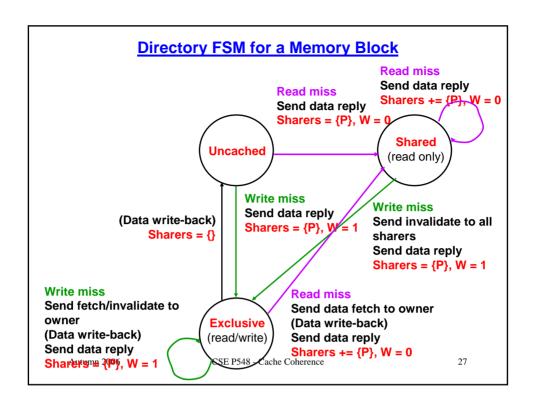

### **Directory FSM for a Memory Block**

Same states and structure as for the cache block FSM

Tracks all copies of a memory block

Makes two state changes:

- · update coherency state

- alter the number of sharers in the sharing set

Autumn 2006 CSE P548 - Cache Coherence

# **False Sharing**

Processors read & write to different words in a shared cache block

- cache coherency is maintained on a cache block basis

- · processes share cache blocks, not data

- block ownership bounces between processor caches

Autumn 2006

CSE P548 - Cache Coherence

# **False Sharing**

### Impact aggravated by:

block size: why?cache size: why?

· large miss penalties: why?

#### Reduced by:

- coherency protocols (coherence state per subblock)

- let cache blocks become incoherent as long as there is only false sharing

- make them coherent if any processor true shares

- compiler optimizations (group & transpose, cache block padding)

- cache-conscious programming wrt initial data structure layout

Autumn 2006 CSE P548 - Cache Coherence