The reduced instruction set computer is an alternative to the general trend toward increasingly complex instruction sets.

It executes most instructions in a single, short cycle.

#### David A. Patterson and Carlo H. Séquin

University of California, Berkeley

A general trend in computers today is to increase the complexity of architectures commensurate with the increasing potential of implementation technologies, as exemplified by the complex successors of simpler machines. Compare, for example, the DEC VAX-11<sup>1</sup> to the PDP-11, the IBM System/38<sup>2</sup> to the System/3, and the Intel iAPX-432<sup>3,4</sup> to the 8086. The complexity of this class of computers, which we call CISCs for complex instruction set computers, has some negative consequences: increased design time, increased design errors, and inconsistent implementations.<sup>5</sup>

Investigations of VLSI architectures indicate that the delay-power penalty of data transfers across chip boundaries and the still-limited resources (devices) available on a single chip are major design limitations. Even a million-transistor chip is insufficient if a whole computer has to be built from it. 6 This raises the question of whether the extra hardware needed to implement a CISC is the best use of "scarce" resources.

The above findings led to the Reduced Instruction Set Computer Project. The purpose of the RISC Project is to explore alternatives to the general trend toward architectural complexity. The hypothesis is that by reducing the instruction set one can design a suitable VLSI architecture that uses scarce resources more effectively than a CISC. We also expect this approach to reduce design time, design errors, and the execution time of individual instructions.

An earlier version of this article, entitled "RISC I: A Reduced Instruction Set VLSI Computer," appeared in the *Proc. Eighth Int'l Symp. Computer Architecture*, May 1981, pp. 443-457.

Our initial version of such a computer is called RISC I. To meet our goals of simplicity and effective single-chip implementation, we somewhat artificially placed the following design constraints on the architecture:

- (1) Execute one instruction per cycle. RISC I instructions should be about as fast and no more complicated than microinstructions in current machines such as the PDP-11 or VAX.

- (2) Make all instructions the same size. This again simplifies implementation. We intentionally postponed attempts to reduce program size.

- (3) Access memory only with load and store instructions; the rest operate between registers. This restriction simplifies the design. The lack of complex addressing modes also makes it easier to restart instructions.

- (4) Support high-level languages. The degree of support is explained below. Our intent is to optimize the performance of RISC I for use with high-level languages.

RISC I supports 32-bit addresses, 8-, 16-, and 32-bit data, and several 32-bit registers. We intend to examine support for operating systems and floating-point calculations in the future.

It would appear that these constraints, based on our desire for simplicity and regularity, would result in a machine with substantially poorer code density, poorer performance, or both; but in spite of these constraints, the resulting architecture competes favorably with other

th

mic

to

reg

SL

ne

sh

gu

m

le

ro

#### Recent developments

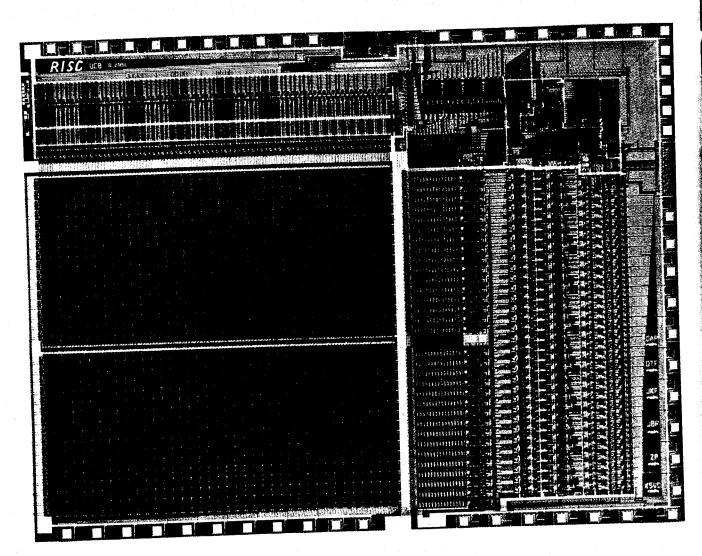

Since this article was submitted, we have received our first good silicon, and it looks like beginner's luck applies to VLSI. These chips correctly ran all diagnostic programs used to verify our original design. We (foolishly) created new diagnostics and uncovered a design error associated with the optional setting of condition codes on the load and shift instructions. Defying historical precedent for solving the problem by announcing a new architectural "feature," we decided to cover this minor error by modifying the RISC I assembler. (This was possible because ALU operations properly set all condition codes, whereas load and shift instructions do not set the negative condition bit. The patch consists of inserting an arithmetic test instruction when a conditional jump needs the N condition from a load or shift operation.)

The fastest of these chips runs all diagnostics at 1.5 MHz, or 2 µsec per RISC I instruction. Several factors explain the difference between expected and measured performance. The chief one is inexperience; this was the first chip that any of us had built. A second is raw speed of transistors from this fabrication. Test structures ran about half the speed of other runs. The last stage of design involved connecting cells, and we concentrated our resources on logical

correctness rather than circuit speed. We recently reexamined the design and found four long clocked control lines that an analog circuit simulator predicts will limit the maximum clock speed to 4 MHz. Furthermore, many of our diagnostics can be run with a 3-MHz clock, suggesting that only a few RISC instructions are limiting performance. Finally, as we have still tested only 20 percent of the chips, we may well find faster RISC I's.

Even at 1.5 MHz and the assembler correction of the error, RISC I still runs programs faster than commercial microprocessors. RISC I was put onto a board with memory, I/O, and memory management on June 11, 1982, and ran its first program.

The bottom line of the RISC I effort is that students, as part of the graduate curriculum, designed and evaluated an architecture, learned Mead-Conway design, built new CAD tools, and tested their design. The end product, a 44,500-transistor integrated circuit, has one minor design error; it worked on the first good silicon and runs programs faster than commercial microprocessors.

More details can be found in an article in the September/October 1982 issue of VLSI Design entitled "Running RISCs."

microprocessors and minicomputers. This is due largely to a scheme of register organization we call overlapped register windows.

#### Support for high-level languages

Clearly, new architectures should be designed with the needs of high-level language programming in mind. It should not matter, however, whether a high-level language system is implemented mostly by hardware or mostly by software, provided the system hides any lower levels from the programmer. 7 Given this framework, the role of the architect is to build a cost-effective system by deciding what pieces of the system should be in hardware and what pieces in software.

The selection of languages for consideration in RISC I was influenced by our environment; we chose "C" because of its large user community and, hence, considerable local expertise. Given the limited number of transistors that can be integrated into a single-chip computer, most of the pieces of a RISC high-level language system are in software, with hardware support for only the most time-consuming events.

To determine what constructs are used most frequently and, if possible, what constructs use the most time in average programs, we first looked at the frequency of classes of variables in high-level language programs. Data collected for Pascal and C are shown in Table 1.

The most important observation was that integer constants appeared almost as frequently as arrays or structures. What is not shown is that more than 80 percent of the scalars were local variables and more than 90 percent of the arrays or structures were global variables.

We also looked at the relative dynamic frequencies of high-level language statements for the same eight programs; average occurrences over one percent are shown in Table 2. This information does not tell what statements use the most time in the execution of typical programs. To answer that question, we have to look at the code produced by typical versions of each of these statements. A "typical" version of each statement was supplied by Wulf as part of his study into judging the quality of compilers.8 We used C compilers for the VAX, PDP-11, and 68000 to determine the average number of instructions and mem-

Table 1. Dynamic percentage of operands in Pascal and C.

|                  | P1 | P2 | Р3 | P4 | C1 | C2 | C3 | C4 | AVERAGE |

|------------------|----|----|----|----|----|----|----|----|---------|

| INTEGER CONSTANT | 14 | 18 | 11 | 20 | 25 | 11 | 29 | 28 | 20±7    |

| SCALAR           | 63 | 68 | 46 | 54 | 37 | 45 | 66 | 62 | 55 ± 11 |

| ARRAY/STRUCTURE  | 23 | 14 | 43 | 25 | 36 | 43 | 5  | 10 | 25 ± 14 |

#### PROGRAM EXPLANATION

- COMP a Pascal P-code style compiler

- P2 MACRO - the macro expansion phase of the SCALD I design system

- P3 PRINT - a prettyprinter for Pascal

- P4 DIFF - a program that finds the differences between two files

- PCC the portable C compiler for the VAX

- C2 CIFPLOT - a program that plots VLSI mask layouts on a dot plotter

- C3 NROFF - a text formatting program

- SORT the Unix sorting program

the

CI.

:hip

rucated the

gain oned

trucction ssing

sup-: per-

data, pport ns in

n our in a oorer aints. other

**UTER**

September 1982

Table 2. Relative frequency of Pascal and C statements.

| STATEMENTS* |      | P1 | P2 | P3 | P4 | AVERAGE    |   | C1  | C2 | C3 | C4 | AVERAGE     |

|-------------|------|----|----|----|----|------------|---|-----|----|----|----|-------------|

| ASSIGN      | <br> | 39 | 52 | 35 | 53 | 45 ± 8     |   | 22  | 50 | 25 | 56 | 38 ± 15     |

| IF          |      | 35 | 30 | 36 | 16 | $29 \pm 8$ |   | 59  | 31 | 61 | 22 | $43 \pm 17$ |

| CALL        |      | 15 | 14 | 16 | 15 | 15 ± 1     |   | · 6 | 17 | 9  | 16 | 12±5        |

| WITH        |      | 2  | 0  | 5  | 13 | $5 \pm 5$  | એ | 2   | 2  | 3  | 5  | 3 ± 1       |

| LOOP        |      | 5  | 5  | 5  | 4  | $5\pm0$    |   | 9   | 0  | 1  | 1  | $3 \pm 4$   |

| CASE        |      | 4  | 0  | 1  | 0  | ∘ 1±1      |   | 2   | -  | -  | 0  | <1±1        |

<sup>\*</sup>Because statements can be nested, we count each occurrence of a statement. Loop statements are counted once per execution rather than once per loop iteration. For example, if two IF statements and three assignment statements appear in a loop that iterates 5 times, we would count 26 statements with 15 assignments, 10 IF statements, and one loop. The WITH statement qualifies a record name.

ory references per statement. By multiplying the frequency of occurrence of each statement with the corresponding number of machine instructions and memory references, we obtain Table 3, which is ordered by memory references.

The data in Table 3 suggest that the procedure call/return is the most time-consuming operation in typical high-level language programs. These results corroborate studies by Lunde<sup>9</sup> and Wichmann.<sup>10</sup> The statistics on operands found in Table 1 emphasize the importance of local variables and constants. RISC I supports HLLs by enhancing performance of the most time-consuming features of typical HLL programs, as opposed to making the architecture "close" to a particular HLL; thus, RISC I attempts to handle local variables, constants, and procedure calls efficiently while leaving less frequent operations to instruction sequences or subroutines.

#### Basic architecture of RISC I

The RISC I architecture has 31 instructions, most of which do simple ALU and shift operations on registers. As shown in Table 4, they have been grouped into four

Table 3.

Weighted relative frequency of HLL statements (ordered by memory references).

| STATEMENTS* | HLL<br>(OCCURRENCE) |             |            | SHTED<br>E INSTR.) | WEIGHTED<br>(MEM. REF.) |            |  |

|-------------|---------------------|-------------|------------|--------------------|-------------------------|------------|--|

| HLL         | P                   | C           | P          | C                  | ·P                      | Ć          |  |

| CALL/RETURN | 15±1                | 12±5        | 31 ± 3     | 33 ± 14            | 44 ± 4                  | 45 ± 19    |  |

| LOOPS       | $5 \pm 0$           | $3 \pm 1$   | $42 \pm 3$ | $32 \pm 6$         | $33 \pm 2$              | $26 \pm 5$ |  |

| ASSIGN      | $45 \pm 5$          | $38 \pm 15$ | $13 \pm 2$ | $13 \pm 5$         | 14 ± 2                  | $15 \pm 6$ |  |

| lF ·        | $29 \pm 8$          | $43 \pm 17$ | 11±3       | $21 \pm 8$         | $7 \pm 2$               | $13 \pm 5$ |  |

| WITH        | $5 \pm 5$           |             | 1±0        | _                  | 1±0                     | _          |  |

| CASE        | 1±1                 | <1±1        | 1±1        | 1±1                | 1 ± 1                   | 1±1        |  |

| GOTO        |                     | 3±1         | _          | $0 \pm 0$          | _                       | 0 ± 0      |  |

<sup>\*</sup>For the CALL statement we counted passing parameters, saving/restoring general registers, and saving/restoring the program counter. The IF and CASE statements include instructions to evaluate expressions and to jump. For LOOP statements we count all the machine instructions executed during each iteration.

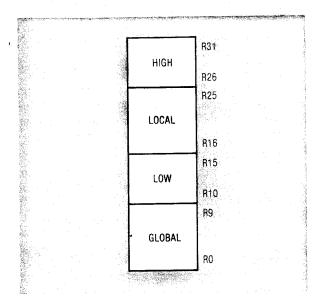

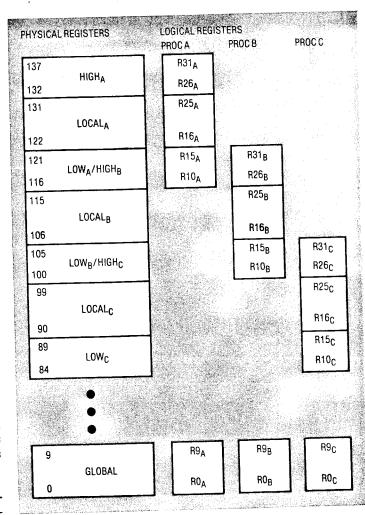

categories: arithmetic-logical, memory access, branch, and miscellaneous. Instructions, data, addresses, and registers are 32 bits. The execution time of a RISC I cycle is given by the time it takes to read and add two registers, and then store the result back into a register. Register 0, which always contains zero, allows us to synthesize a variety of operations and addressing modes.

Load and store instructions move data between registers and memory. Rather than lengthen the general cycle to permit a complete memory access, these instructions use two CPU cycles. There are eight variations of memory access instructions to accommodate sign-extended or zero-extended 8-bit, 16-bit, and 32-bit data. Although there appears to be only the index-plus-displacement addressing mode in data transfer instructions, absolute and register-indirect addressing can be synthesized using register 0 (see Table 5).

Branch instructions include call, return, conditional, and unconditional jump. The conditional instructions are the standard set used originally in the PDP-11 and found in most 16-bit microprocessors today. Most of the innovative features of RISC I are found in call, return, and jump; they will be discussed later.

Figure 1 shows the 32-bit format used by register-toregister instructions and memory access instructions. For register-to-register instructions, DEST selects one of the 32 registers as the destination of the result of the operation performed on the registers specified by SOURCE1 and SOURCE2. If IMM = 0, the low-order five bits of SOURCE2 specify another register; if IMM=1, SOURCE2 expresses a sign-extended 13-bit constant. As mentioned above, the frequency of integer constants in HLL programs suggests architectural support, so immediate operands are available in every instruction. SCC determines whether or not the condition codes are set. Memory access instructions use SOURCE1 to specify the index register and SOURCE2 to specify the offset. One other format combines the last three fields to form a 19-bit PC-relative address and is used primarily by the branch instructions.

The examples in Table 6 show that many of the important VAX instructions can be synthesized from simple RISC I addressing modes and opcodes. Comparative measurements of benchmarks will demonstrate the effectiveness of the chosen instruction set.

ADD ADD( SUB SUB) SUB)

SUB:

XOR SLL SRL SRA

LDS: LDB: LDB: STL

LDL

LDSI

STS STB JMP

JMP Cali

CALI

RET CALI

RETI LDH GTLI

GETI PUTI

Re level time gran

ADDF REGI:

IMM!

ABS( REG

Sept

Table 4. Assembly language definition for RISC I.

RL PROTENTION ROBERTA Rs = Source Regions 52 = Source 2

| INSTRUCTION | OPERANDS    | COMMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 52- 700                                        |

|-------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| ADD         | Rs,S2,Rd    | Rd Rs + S2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                |

| ADDC        | Rs,S2,Rd    | Rd — Rs + S2 + carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | integer add                                    |

| SUB         | Rs,S2,Rd    | Rd Rs S2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | add with carry                                 |

| SUBC        | Rs,S2,Rd    | Rd — Rs — S2 — carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | integer subtract                               |

| SUBR        | Rs,S2,Rd    | Rd S2 Rs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | subtract with carry                            |

| SUBCR       | Rs,S2,Rd    | Rd — S2 — Rs — carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | integer subtract                               |

| AND         | Rs,S2,Rd    | Rd — Rs & S2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | subtract with carry                            |

| OR          | Rs,S2,Rd    | Rd Rs   S2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | logical AND                                    |

| XOR         | Rs,S2,Rd    | Rd — Rs xor S2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | logical OR                                     |

| SLL         | Rs,S2,Rd    | Rd — Rs shifted by S2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | logical EXCLUSIVE OR                           |

| SRL         | Rs,S2,Rd    | Rd — Rs shifted by S2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | shift left                                     |

| SRA         | Rs,S2,Rd    | Rd — Rs shifted by S2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | shift right logical                            |

| LDL         | (Rx)S2,Rd   | The second secon | shift right arithmetic                         |

| LDSU        | (Rx)S2,Rd   | $Rd \leftarrow M[Rx + S2]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | load long                                      |

| LDSS        | (Rx)S2,Rd   | Rd — M[Rx + S2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | load short unsigned                            |

| LDBU        | (Rx)S2,Rd   | Rd — M[Rx + S2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | load short signed                              |

| LDBS        | (Rx)S2,Rd   | Rd — M[Rx + S2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | load byte unsigned                             |

| STL         | Rm,(Rx)S2   | Rd — M[Rx + S2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | load byte signed                               |

| STS         | Rm,(Rx)S2   | M[Rx + S2] — Rm<br>M[Rx + S2] — Rm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | store long                                     |

| STB         | Rm,(Rx)S2   | M[Rx + S2] — Rm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | store short                                    |

| JMP         |             | IMI INA ∓ 32 J ← RIII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | store byte                                     |

| JMPR        | COND,S2(Rx) | pc Rx + S2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | conditional jump                               |

| CALL        | COND,Y      | pc — pc + Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | conditional relative                           |

| JALL .      | Rd,S2(Rx)   | Rd — pc, next<br>pc — Rx + S2, CWP — CWP — 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | call                                           |

| CALLR       | Rd,Y        | Rd—pc, next                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | and change window                              |

|             |             | pc pc + Y, CWP CWP 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | call relative<br>and change window             |

| RET         | Rm,S2       | pc-Rm+S2, $CWP-CWP+1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | return and change window                       |

| CALLINT     | Rd          | Rd-last pc; next CWP-CWP-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | disable interrupts                             |