### Signal Integrity

Friday June 25 2011 Vikram Jandhyala vj@uw.edu

Professor, UWEE Founder, Physware, Inc.

## What is signal integrity?

- The challenges and problems that arise in highspeed products due to propagation path effects

- Especially in interconnects

- On-chip

- Chip-to-Chip

- Package

- Board

- Backplane

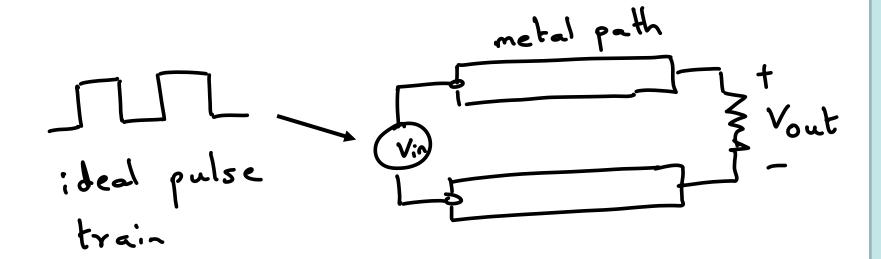

## Transmission Line Example

What do you expect to see at V<sub>out</sub>?

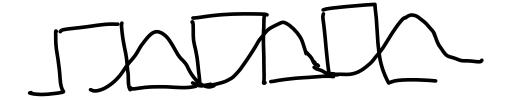

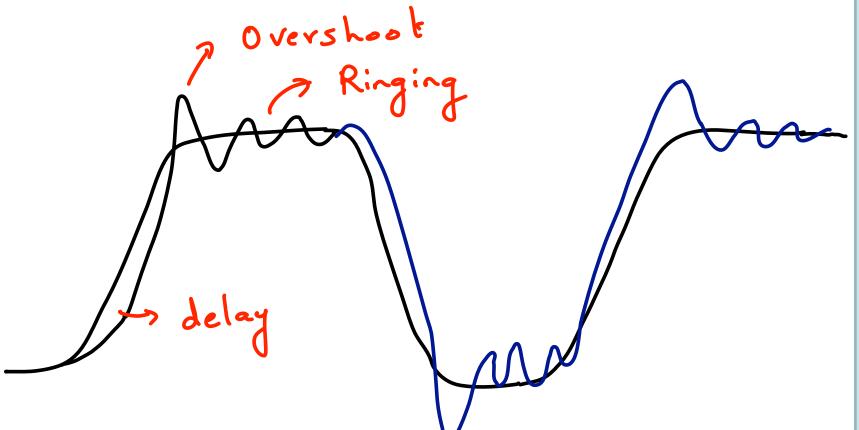

## Delay

"Time of Flight": Related to velocity of light and distance.

#### Loss

(Typically) Higher frequency components are "attenuated"

- Loss caused by

- Metal

- Material (Dielectric)

- Radiation

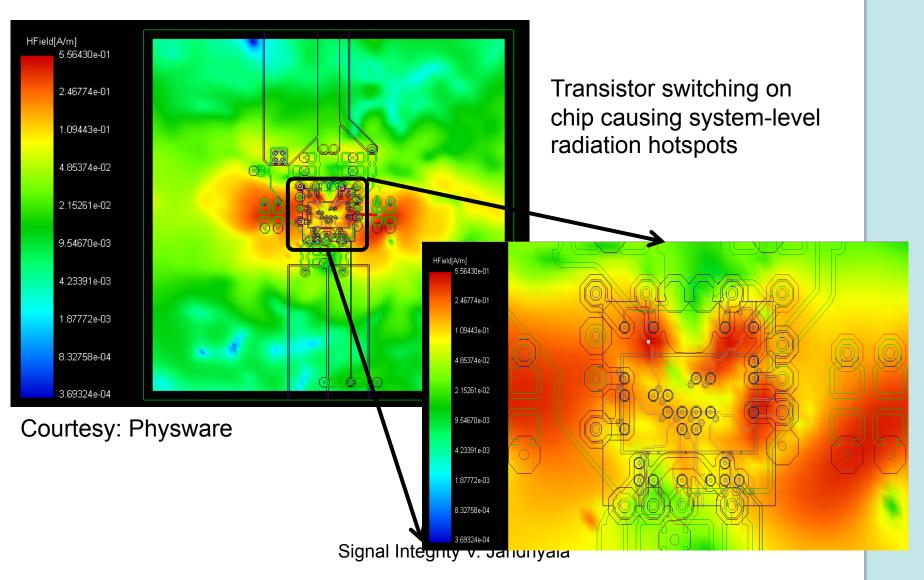

#### **EMI** Radiation

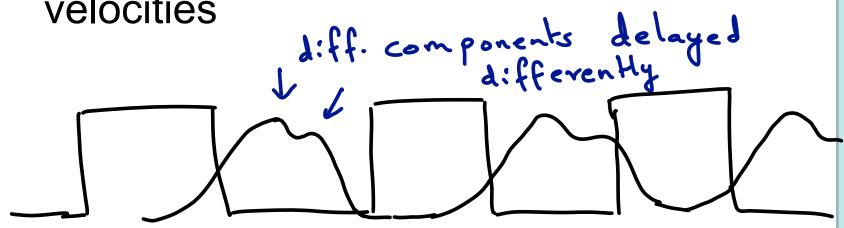

## Dispersion

Different frequencies travel at different velocities

#### Mismatch

- Driver impedance

- Line impedance

- Receiver impedance (input)

Any mismatch causes additional effects

#### Mismatch

Normally seen at 100 MHz or higher clock rates

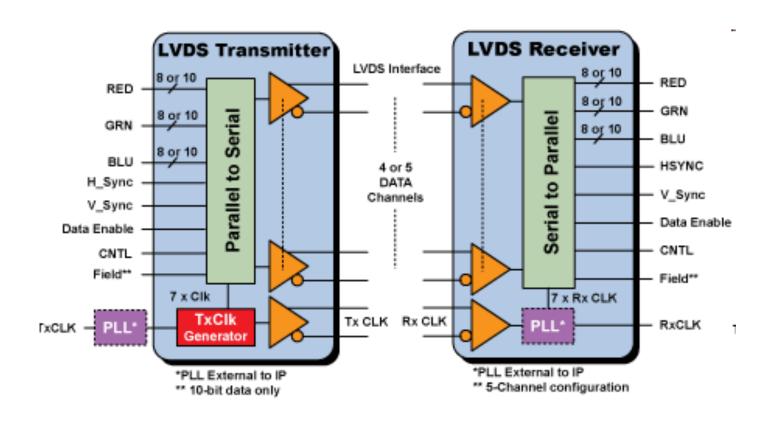

#### Serialization-Deserialization

Signal Integrity V. Jandhyala

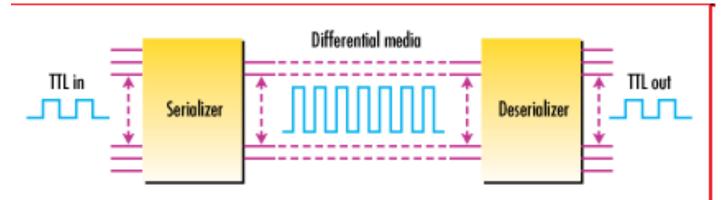

## Serdes: Differential signaling

▲ Serdes technology is based on a serializer/deserializer pair where typical inputs, TTL signals (0 to 3.3-V swing) enter the serializer 'horizontally' and are then 'vertically' aligned so that in one clock period one set of parallel bits, or just one word, is transmitted. The internal frequency of the serializer must be faster than the incoming TTL data.

Source: Fairchild

## Applications of high-speed links

- Processor to memory

- Peripherals and hard drives

- USB

- HDMI and Video

- Flash

- Ethernet backplane

- Infiniband-server backplane

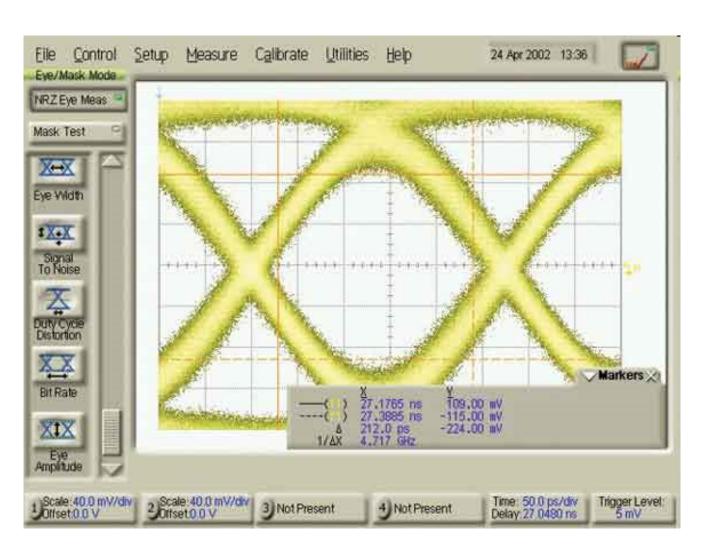

# Differential signals and eye diagrams

## Eye diagrams

- Eye is produced by multiple passes of differential (equal and opposite signals)

- Jitter: timing randomness and amplitude randomness arising due to

- Asymmetries in a differential system

- Thermal and noise effects

- Crosstalk and inter-symbol interference

- LINK to an eye diagram animation on YouTube

## From an SI angle, why use Serdes?

- Why would you switch from signal-ended, lowspeed, multiple parallel lines to a differential, high-speed, serial line. Any issues to expect?

- Benefits: Less crosstalk, less noise, potentially less real estate

- Challenges: Higher-speed signals imply highfrequency SI effects: dispersion, radiation

- Some of these may be mitigated due to differential design

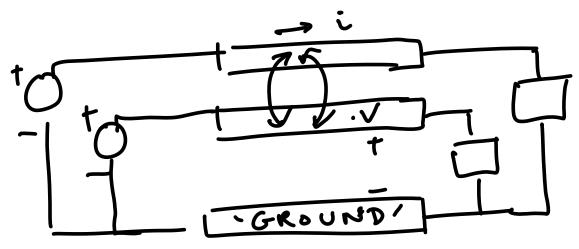

#### Crosstalk

Inductive

and Capacitive

pindactace (H)

$$V = L di ; i = C dv$$

$$dt$$

$$V: dt$$

Signal Integrity V. Jandhyala

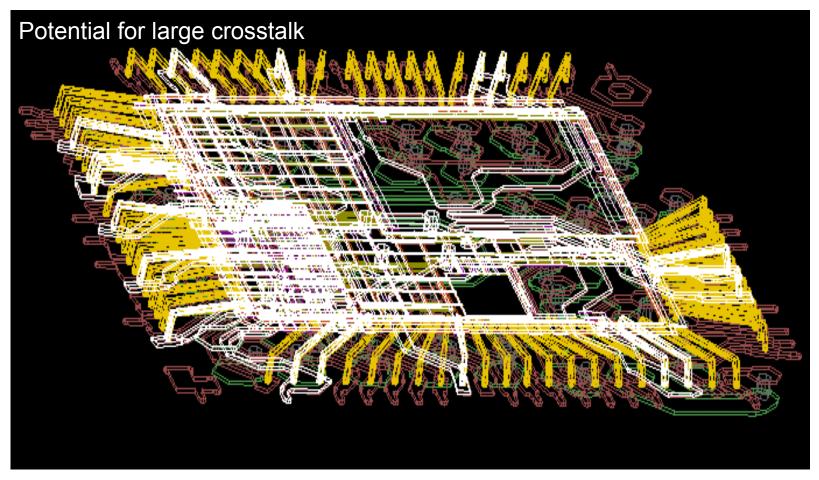

## Signal paths

Courtesy: Physware

Signal Integrity V. Jandhyala

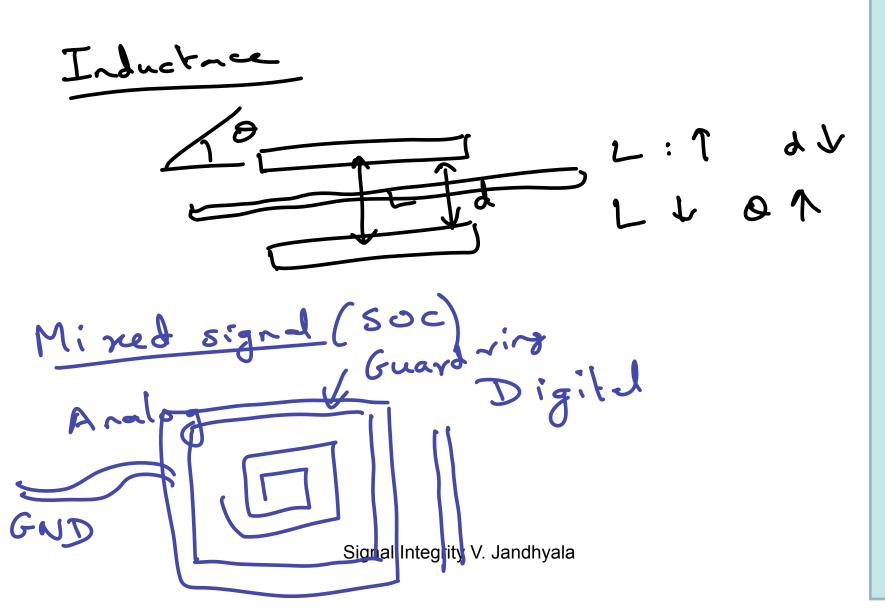

#### Models

#### Models

resistor Enample: Substrate coupling (no delay, (500) mismateh) create resistive mush' of the full chip

Reflected S-parameters IncidetWave , Transmitted Port 2 Port1 1 Transmitted ; 1511: Reflected |S<sub>12</sub>[: [Incident] | Incident | Transmitted power 2 |S12| Reflected power & [Sn] Signal Integrity V. Jandhyala

1 Sn (2+ ) Sn /= 1 I deally: at all frequencies at all frequencies be cause reality, wave/electromagneha effects:

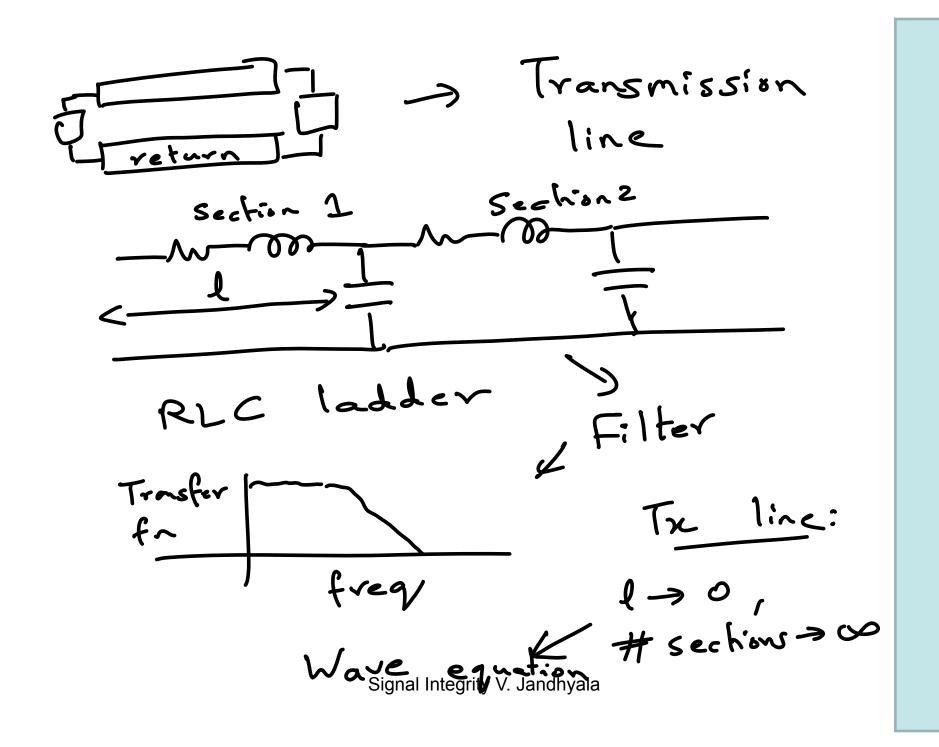

## Computing S-parameters

- From lumped-circuit models

- -Z to S

- Least accurate and easiest

- From transmission line models

- 1D Wave equations

- Intermediate complexity and accuracy

- From mesh-based solution to Maxwell's equations

- 3D Wave equations

- Most complex and high accuracy

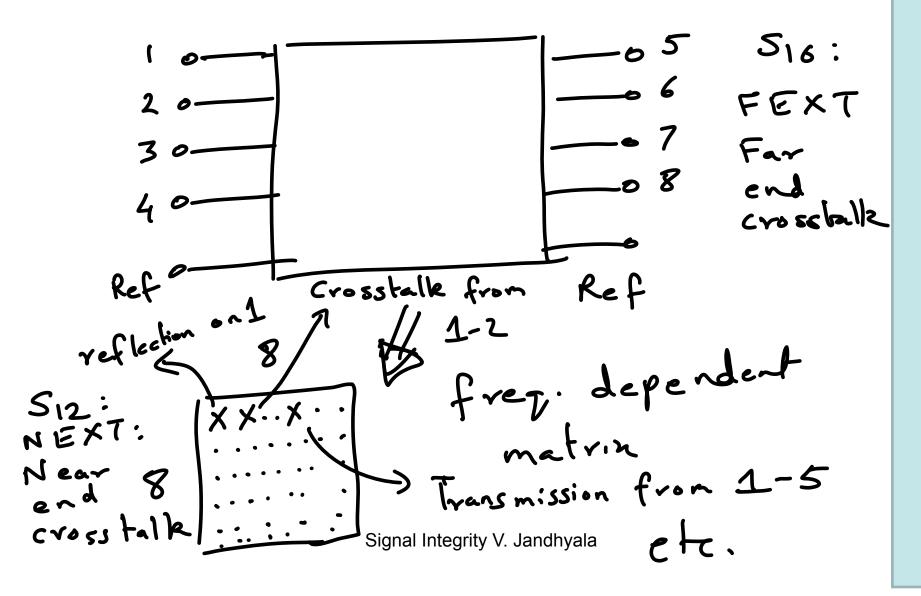

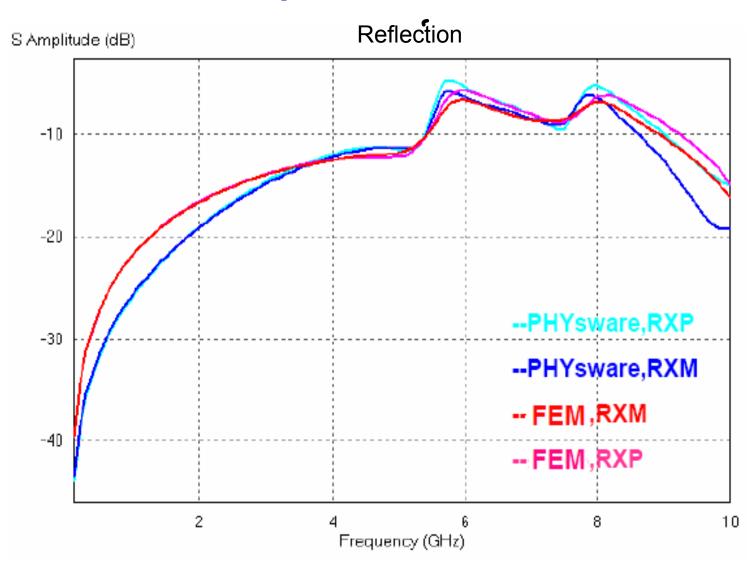

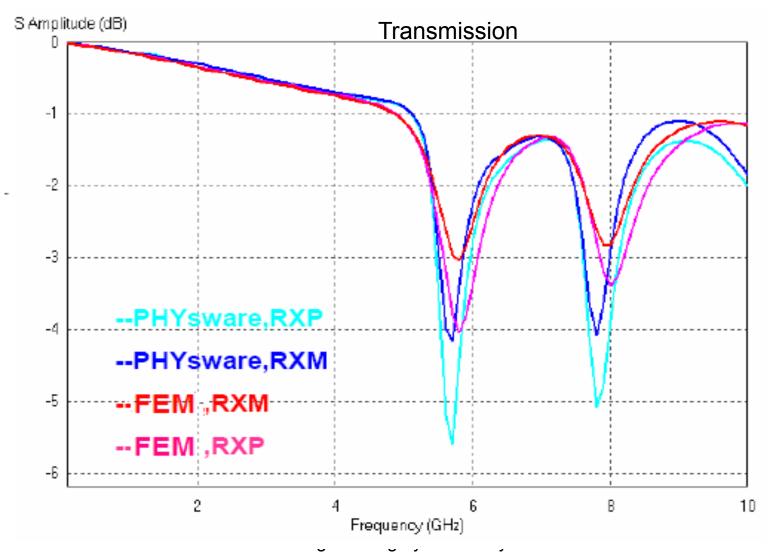

## S-parameter matrix

## S-parameters

## S-parameters

## Memory

Courtesy: Physware

Signal Integrity V. Jandhyala

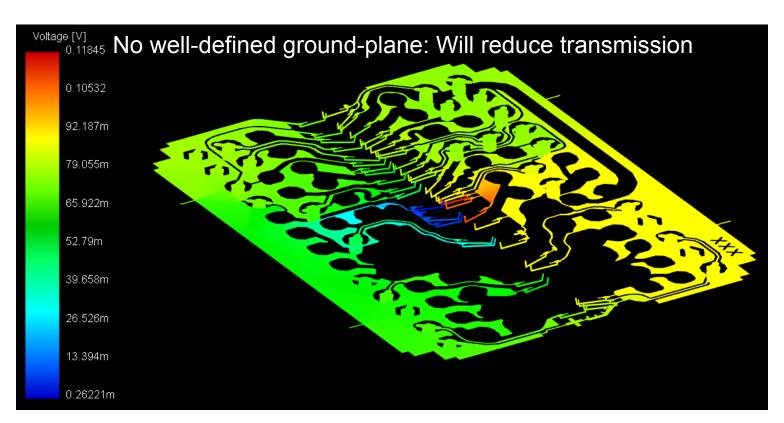

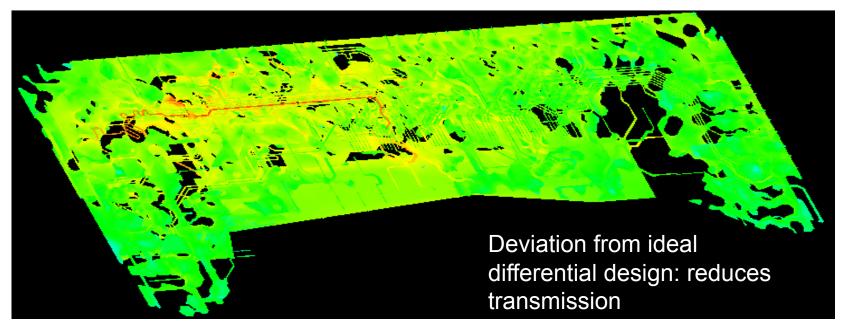

## Return current spreading

Courtesy: Physware

Signal Integrity V. Jandhyala

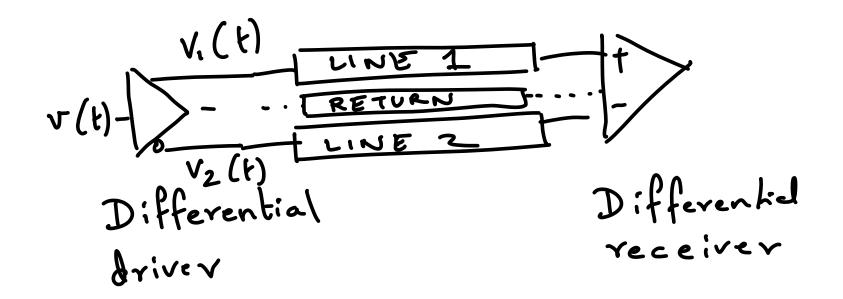

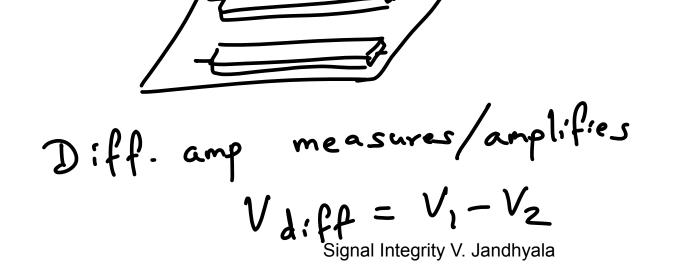

## Differential signaling

```

idea:

Basic

Send 2 signals on two

- a bit sequence

- its complement

Work with the difference of

the two signals at the

Signal Integrity V. Jandhyala

```

Asymmetries in the channel also creete a common mode' signal: V, t Vz A good differential amplifier/ receiver rejects/the Common mode, reconstructing only the signd CMRR: Common Mode Signal Integrity V. Jandhyala

Benefits of diff. signaling: 1. Lower Ldi noise from driver injection Ldi dt nearly cancels

2. Higher gain/amplification with low noissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaeintegriposeissaei

Benefits 3. Lower voltage signaling (LVDS) due la jain Lower radiation/EMI due to cancellation. There are some negatives...

## Negatives

#### Sources

- EE 571 Notes Vikram Jandhyala

- Bogatin: signal integrity, Prentice Hall

- Young: Digital signal integrity, Prentice Hall

- www.physware.com

- http://www.altera.com/products/ip/dsp/images/ lvds-tx-rx-ip-blockdiagram.gif

- http://i.cmpnet.com/eet/news/03/january/ SS1254 FAIRCHILD.gif

- http://www.latticesemi.com/images/img12682.jpg

- http://www.youtube.com/watch?v=my7Cl84le5g