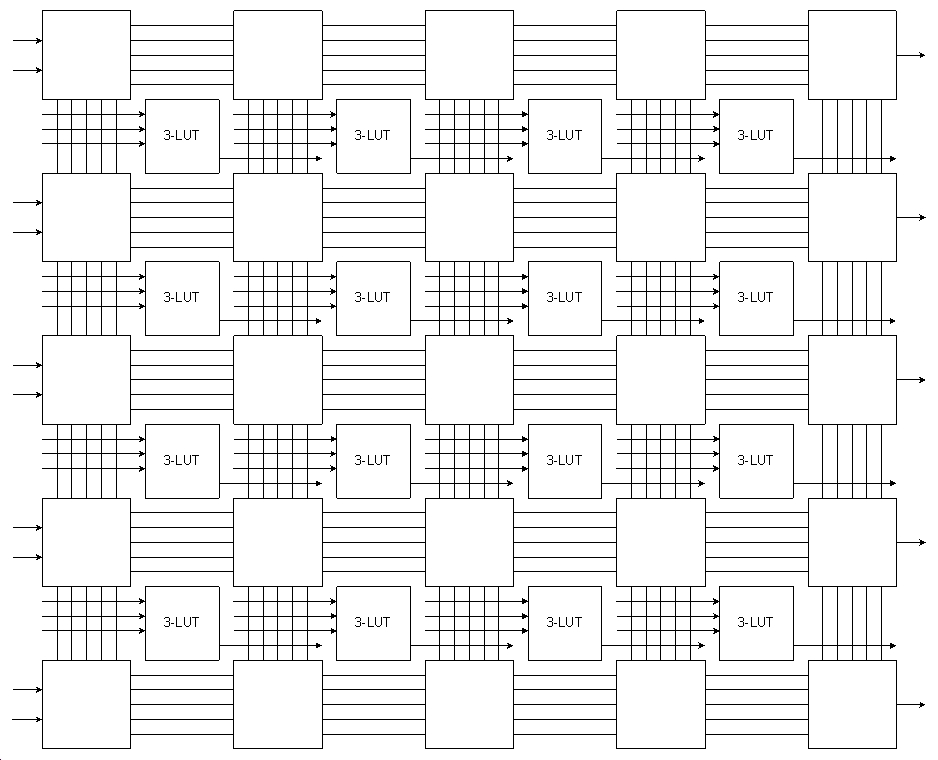

Below is a simple FPGA architecture that uses 3-input LUTs.

Implement a 4-bit comparator, which compares two 4-bit unsigned numbers and produces a greater-than output, using this array.

Solve this problem using the following steps, showing all your work.

(Hint: you don’t need close to all the LUTs.)

a) Factor the comparator function into a multi-level logic circuit, each node of which is a 3 (max) input function.

Name each of these functions using a letter that represents the output and give the function each computes.

b) Place each of the functions from part a in the FPGA array by writing the name in the appropriate 3-LUT.

c) Route the circuit together using the interconnection network.

Use an X to show the connection of each input and output of the 3-LUTs used.

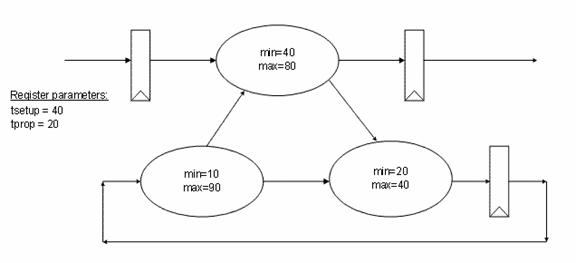

Each of the switch boxes at the intersection of the row and column channels can connect each wire on one side to a wire on each of the other sides.

These connections can be made in either direction.

For each connection that you use in a switch box, draw an arrow to show the connection.

Circuit inputs arrive at the left and outputs leave at the right.(Here is the diagram you can print:

fpga-worksheet.pdf)