CSE467 Homework 5

Distributed: February 11, 2005

Due: Start of Class, February 25, 2005

Part 1 – Testing your Lab 7 Audio Interface with the Oscilloscope

You should connect up the oscilloscope to capture the signals MCLK, BICK and LRCK. Turn off the power while you are connecting the probes so you don’t short signals out. You should be careful how you connect the scope probes to these signals. Also, don’t forget to connect the probe ground signals.

Using the oscilloscope, you should measure the following values (which can be negative):

a) The frequency of each signal. MCLK:____________ BICK:____________ LRCK:___________

b) The offset from the rising edge of MCLK to the rising edge of BICK:________________________

c) The offset from the rising edge of MCLK to the falling edge of BICK:________________________

d) The offset from the falling edge of BICK to the rising edge of LRCK:________________________

d) The offset from the falling edge of BICK to the falling edge of LRCK:________________________

e) The offset from the changing edge of SDTI1 to the active edge of BICK:______________________ (look in the data sheet for the active edge of BICK)

Now connect the scope to the audio signal itself using the special audio jack that bares the signals. Display this signal on the scope and measure the frequencies of the first 3 notes of the scale:

Note 1 ___________________ Note 2 ____________________ Note 3___________________

Part 2 – Signed and Unsigned Arithmetic in Verilog

Verilog 2001 added signed numbers to Verilog. Here’s a little exercise to show you why this is important.

- First run this code in Active-HDL. In a sentence or two, explain each of the four console outputs.

- Next, look at these two multipliers (1,2) and this test fixture. One outputs the correct answer because it uses signed numbers. The other, using pre-Verilog 2001 syntax, won’t work correctly if we want to do signed arithmetic.

- Implement a signed multiplier without using Verilog 2001 signed arithmetic. Your multiplier must have the same interface as the provided multipliers.

- Turn in your analysis, code, and a waveform showing that the outputs of the signed multiplier and your multiplier agree.

Part 3 – Design Problem

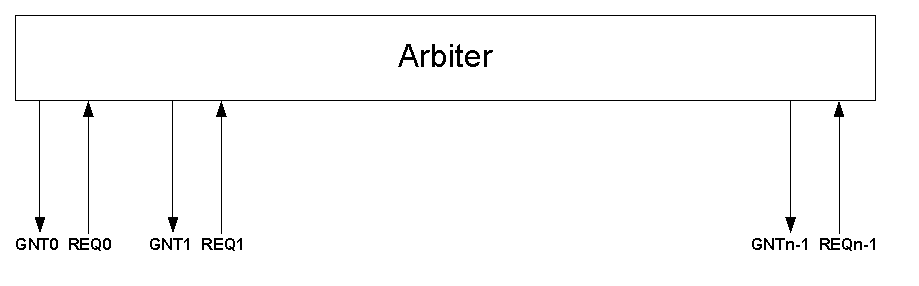

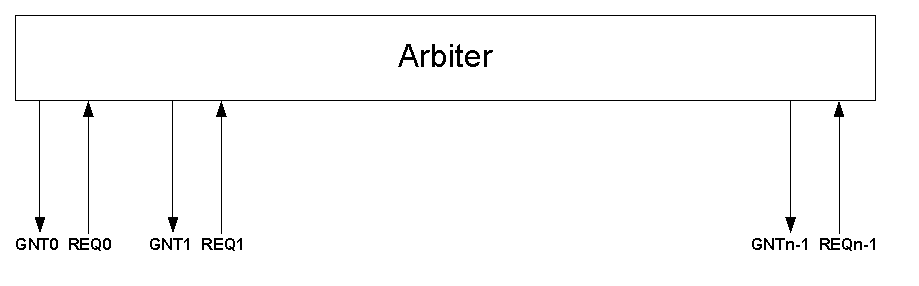

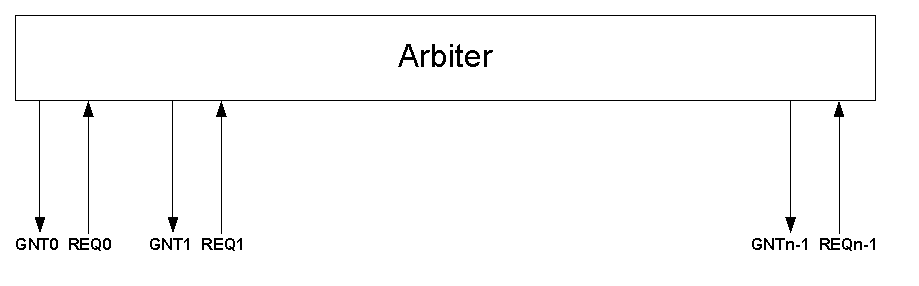

An arbiter receives a request signal (REQi) from N modules, numbered 0 to N-1, each requesting exclusive access to a resource such as a bus or memory. The arbiter sends each of the N modules a corresponding grant (GNTi) signal indicating whether the request was granted. The arbiter must choose exactly one of the modules that asserts a request, and assert the corresponding grant signal. The decision is made by giving the lowest numbered modules the highest priority. Sketch the design of this arbiter circuit so that it has O(logN) delay.

Comments to: cgiefer@cs