# MSP430 Interrupts

### What is an Interrupt?

- Reaction to something in I/O (human, comm link)

- Usually asynchronous to processor activities

- "interrupt handler" or "interrupt service routine" (ISR) invoked to take care of condition causing interrupt

- Change value of internal variable (count)

- Read a data value (sensor, receive)

- Write a data value (actuator, send)

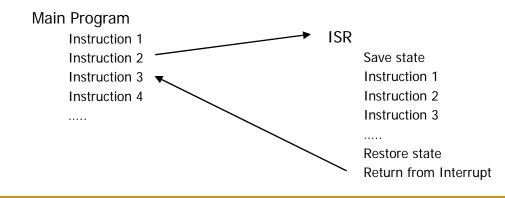

### Interrupts

- Interrupts *preempt* normal code execution

- Interrupt code runs in the *foreground*

- Normal (e.g. main()) code runs in the background

- Interrupts can be enabled and disabled

- Globally

- Individually on a per-peripheral basis

- Non-Maskable Interrupt (NMI)

- The occurrence of each interrupt is unpredictable

- When an interrupt occurs

- Where an interrupt occurs

- Interrupts are associated with a variety of on-chip and off-chip peripherals.

- □ Timers, Watchdog, D/A, Accelerometer

- NMI, change-on-pin (Switch)

### Interrupts

### Interrupts commonly used for

- Urgent tasks w/higher priority than main code

- Infrequent tasks to save polling overhead

- Waking the CPU from sleep

- Call to an operating system (software interrupt).

- Event-driven programming

- The flow of the program is determined by events—i.e., sensor outputs or user actions (mouse clicks, key presses) or messages from other programs or threads.

- The application has a main loop with event detection and event handlers.

# Interrupt Flags

- Each interrupt has a flag that is raised (set) when the interrupt occurs.

- Each interrupt flag has a corresponding enable bit – setting this bit allows a hardware module to request an interrupt.

- Most interrupts are *maskable*, which means they can only interrupt if

- 1) enabled and

- 2) the general interrupt enable (GIE) bit is set in the status register (SR).

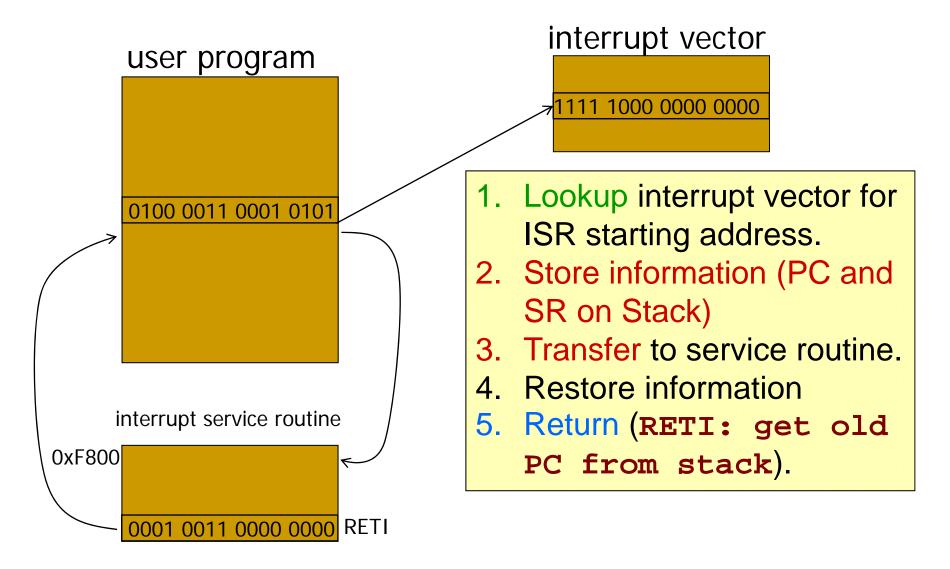

### Interrupt Vectors

- The CPU must know where to fetch the next instruction following an interrupt.

- The address of an ISR is defined in an *interrupt* vector.

- The MSP430 uses vectored interrupts where each ISR has its own vector stored in a vector table located at the end of program memory.

- Note: The vector table is at a fixed location (defined by the processor data sheet), but the ISRs can be located anywhere in memory.

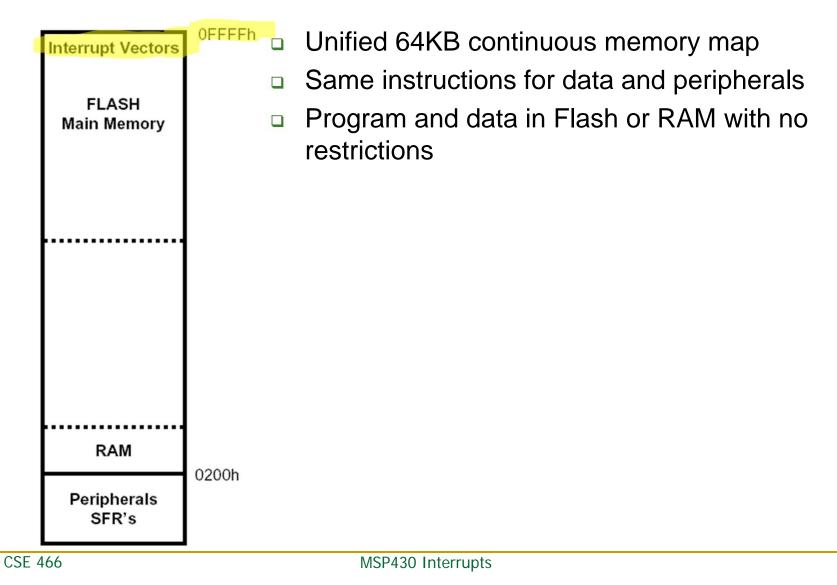

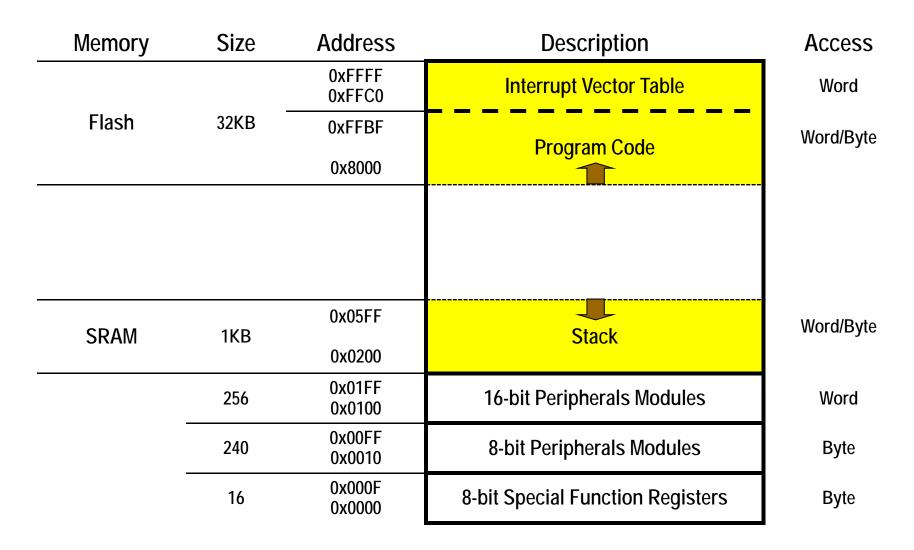

### MSP430 Memory

## Serving Interrupt Request

### MSP430x2xx Interrupt Vectors

Higher address → higher priority

| INTERRUPT SOURCE                                                                                       | INTERRUPT FLAG                                              | SYSTEM<br>INTERRUPT                                  | WORD ADDRESS     | PRIORITY<br>31, highest |

|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------|------------------|-------------------------|

| Power-up<br>External reset<br>Watchdog Timer+<br>Flash key violation<br>PC out-of-range <sup>(1)</sup> | PORIFG<br>RSTIFG<br>WDTIFG<br>KEYV<br>See <sup>(2)</sup>    | Reset                                                | OFFFEh           |                         |

| NMI<br>Oscillator fault<br>Flash memory access violation                                               | NMIIFG<br>OFIFG<br>ACCVIFG <sup>(2)(3)</sup>                | (non)-maskable,<br>(non)-maskable,<br>(non)-maskable | OFFFCh           | 30                      |

|                                                                                                        |                                                             |                                                      | OFFFAh           | 29                      |

|                                                                                                        |                                                             |                                                      | 0FFF8h           | 28                      |

| Comparator_A+ (MSP430F20x1)                                                                            | CAIFG <sup>(4)</sup>                                        | maskable                                             | 0FFF6h           | 27                      |

| Watchdog Timer+                                                                                        | WDTIFG                                                      | maskable                                             | 0FFF4h           | 26                      |

| Timer_A2                                                                                               | TACCR0 CCIFG <sup>(4)</sup>                                 | maskable                                             | 0FFF2h           | 25                      |

| Timer_A2                                                                                               | TACCR1 CCIFG.TAIFG <sup>(2)(4)</sup>                        | maskable                                             | OFFF0h           | 24                      |

|                                                                                                        |                                                             |                                                      | OFFEEh           | 23                      |

|                                                                                                        |                                                             |                                                      | OFFECh           | 22                      |

| ADC10 (MSP430F20x2)                                                                                    | ADC10IFG <sup>(4)</sup>                                     | maskable                                             | OFFEAh           | 21                      |

| SD16_A (MSP430F20x3)                                                                                   | SD16CCTL0 SD16OVIFG,<br>SD16CCTL0 SD16IFG <sup>(2)(4)</sup> | maskable                                             |                  |                         |

| USI<br>(MSP430F20x2, MSP430F20x3)                                                                      | USIIFG, USISTTIFG <sup>(2)(4)</sup>                         | maskable                                             | 0FFE8h           | 20                      |

| I/O Port P2 (two flags)                                                                                | P2IFG.6 to P2IFG.7 <sup>(2)(4)</sup>                        | maskable                                             | 0FFE6h           | 19                      |

| I/O Port P1 (eight flags)                                                                              | P1IFG.0 to P1IFG.7 <sup>(2)(4)</sup>                        | maskable                                             | 0FFE4h           | 18                      |

|                                                                                                        |                                                             |                                                      | 0FFE2h           | 17                      |

|                                                                                                        |                                                             |                                                      | OFFE0h           | 16                      |

| See (5)                                                                                                |                                                             |                                                      | OFFDEh to OFFC0h | 15 to 0, lowest         |

#### Table 7. Interrupt Sources

A reset is generated if the CPU tries to fetch instructions from within the module register memory address range (0h to 01FFh) or from within unused address ranges.

(2) Multiple source flags

(3) (non)-maskable: the individual interrupt-enable bit can disable an interrupt event, but the general interrupt enable cannot.

(4) Interrupt flags are located in the module.

(5) The interrupt vectors at addresses 0FFDEh to 0FFC0h are not used in this device and can be used for regular program code if necessary.

### MSP430F2274 Address Space

### Processing an Interrupt...

- 1) Current instruction completed

- 2) MCLK started if CPU was off

- 3) Processor pushes program counter on stack

- 4) Processor pushes status register on stack

- 5) Interrupt w/highest priority is selected

- 6) Interrupt request flag cleared if single sourced

- 7) Status register is cleared

- Disables further maskable interrupts (GIE cleared)

- Terminates low-power mode

- 8) Processor fetches interrupt vector and stores it in the program counter

- 9) User ISR must do the rest!

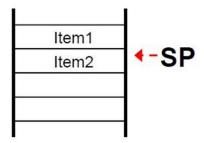

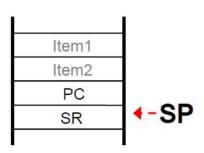

# Interrupt Stack

#### Prior to Interrupt Service Routine (=ISR)

#### ISR hardware - automatically

- Program Counter (= PC) pushed

- Status Register (= SR) pushed

- Interrupt vector moved to PC

- GIE, CPUOFF, OSCOFF and SCG1 cleared

- IFG flag cleared on single source flags

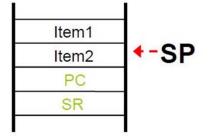

#### reti - automatically

- SR popped original

- PC popped

### Interrupt Service Routines

- Look superficially like a subroutine.

- However, unlike subroutines

- □ ISR's can execute at unpredictable times.

- Must carry out action and thoroughly clean up.

- Must be concerned with shared variables.

- Must return using *reti* rather than *ret*.

- ISR must handle interrupt in such a way that the interrupted code can be resumed without error

- Copies of all registers used in the ISR must be saved (preferably on the stack)

### Interrupt Service Routines

### Well-written ISRs:

- Should be short and fast

- Should affect the rest of the system as little as possible

- Require a balance between doing very little thereby leaving the background code with lots of processing – and doing a lot and leaving the background code with nothing to do

- Applications that use interrupts should:

- Disable interrupts as *little as possible*

- Respond to interrupts as quickly as possible

### Interrupt Service Routines

- Interrupt-related runtime problems can be exceptionally hard to debug

- Common interrupt-related errors include:

- □ Failing to *protect global variables*

- □ Forgetting to actually *include the ISR* no linker error!

- Not testing or validating thoroughly

- Stack overflow

- Running out of CPU horsepower

- Interrupting critical code

- Trying to outsmart the compiler

# Returning from ISR

- MSP430 requires 6 clock cycles before the ISR begins executing

- The time between the interrupt request and the start of the ISR is called *latency (plus time to complete the current instruction, 6 cycles, the worst case)*

- An ISR always finishes with the return from interrupt instruction (*reti*) requiring 5 cycles

- □ The SR is popped from the stack

- Re-enables maskable interrupts

- Restores previous low-power mode of operation

- The PC is popped from the stack

- Note: if waking up the processor with an ISR, the new power mode must be set in the stack saved SR

### Return From Interrupt

#### Single operand instructions:

| Mnemonic     |     | Operation                          | Description                    |

|--------------|-----|------------------------------------|--------------------------------|

| PUSH(.Bor.W) | src | SP-2→SP, src→@SP                   | Push byte/word source on stack |

| CALL         | dst | SP-2→SP, PC+2→@SP<br>dst→PC        | Subroutine call to destination |

| RETI         |     | TOS→SR, SP+2→SP<br>TOS→PC, SP+2→SP | Return from interrupt          |

#### Emulated instructions:

| Mnemonic        | Operation                       | Emulation                 | Description                             |

|-----------------|---------------------------------|---------------------------|-----------------------------------------|

| RET             | @SP→PC<br>SP+2→SP               | MOV @SP+,PC               | Return from subroutine                  |

| POP(.Bor.W) dst | @SP→temp<br>SP+2→SP<br>temp→dst | MOV(.B or .W)<br>@SP+,dst | Pop byte/word from stack to destination |

### Summary

- By coding efficiently you can run multiple peripherals at high speeds on the MSP430

- Polling is to be avoided use interrupts to deal with each peripheral only when attention is required

- Allocate processes to peripherals based on existing (fixed) interrupt priorities - certain peripherals can tolerate substantial latency

- Use GIE when it's shown to be most efficient and the application can tolerate it – otherwise, control individual IE bits to minimize system interrupt latency.

- An interrupt-based approach eases the handling of asynchronous events

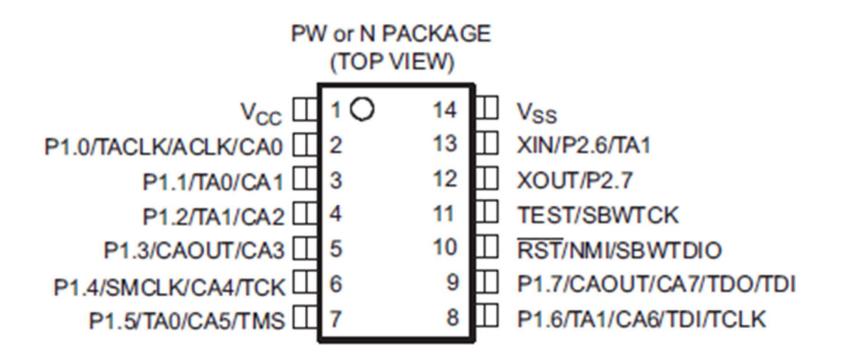

### P1 and P2 interrupts

Only transitions (low to hi or hi to low) cause interrupts

- P1IFG & P2IFG (Port 1 & 2 Interrupt FlaG registers)

- Bit 0: no interrupt pending

- Bit 1: interrupt pending

- P1IES & P2IES (Port 1 & 2 Interrupt Edge Select reg)

- Bit 0: PxIFG is set on low to high transition

- Bit 1: PxIFG is set on high to low transition

- P1IE & P2IE (Port 1 & 2 Interrupt Enable reg)

- Bit 0: interrupt disabled

- Bit 1: interrupt enabled

### Example P1 interrupt msp430x20x3\_P1\_02.c

```

#include <msp430x20x3.h>

void main(void)

WDTCTL = WDTPW + WDTHOLD; // Stop watchdog timer

// Set P1.0 to output direction

P1DIR = 0 \times 01;

Plie = 0 \times 10;

// P1.4 interrupt enabled

P1IES = 0 \times 10;

// P1.4 Hi/lo edge

P1IFG &= \sim 0 \times 10;

// P1.4 IFG cleared

_BIS_SR(LPM4_bits + GIE); // Enter LPM4 w/interrupt

}

// Port 1 interrupt service routine

#pragma vector=PORT1_VECTOR

interrupt void Port 1(void)

P1OUT ^{=} 0 \times 01;

// P1.0 = toggle

P1IFG &= \sim 0 \times 10;

// P1.4 IFG cleared

}

```

### Ex: Timer interrupt: msp430x20x3\_ta\_03.c

```

#include <msp430x20x3.h>

void main(void)

// Stop WDT

WDTCTL = WDTPW + WDTHOLD;

P1DIR = 0x01;

// P1.0 output

TACTL = TASSEL_2 + MC_2 + TAIE;

// SMCLK, contmode, interrupt

_BIS_SR(LPM0_bits + GIE);

// Enter LPM0 w/ interrupt

// Timer_A3 Interrupt Vector (TAIV) handler

#pragma vector=TIMERA1_VECTOR

_interrupt void Timer_A(void)

switch( TAIV )

2: break;

// CCR1 not used

case

// CCR2 not used

4: break;

case

case 10: P1OUT ^= 0x01;

// overflow

break;

```

# Example

we stepped through the following code in class with the debugger

#### Msp430x20x3\_ta\_06.c (modified, part 1) Demo: Samples 8

```

#include <msp430x20x3.h>

void main(void)

{

WDTCTL = WDTPW + WDTHOLD;// Stop WDT

P1DIR |= 0x01; // P1.0 output

CCTL1 = CCIE; // CCR1 interrupt enabled

CCR1 = 0xA000;

TACTL = TASSEL_2 + MC_2; // SMCLK, Contmode

_BIS_SR(LPM0_bits + GIE);// Enter LPM0 w/ int.

}

```

Servicing a timer interrupt; toggling pin in ISR

# Msp430x20x3\_ta\_06.c (modified, part 2)

Demo: Samples 8

// Timer\_A3 Interrupt Vector (TAIV) handler

```

#pragma vector=TIMERA1_VECTOR

```

```

interrupt void Timer A(void)

switch( TAIV )

// CCR1

case 2:

P10UT ^= 0x01; // Toggle P1.0

CCR1 += 0xA000; // Add Offset to CCR1 == 0xA000

break;

4: break; // CCR2 not used

case

case 10: break; // overflow not used

```

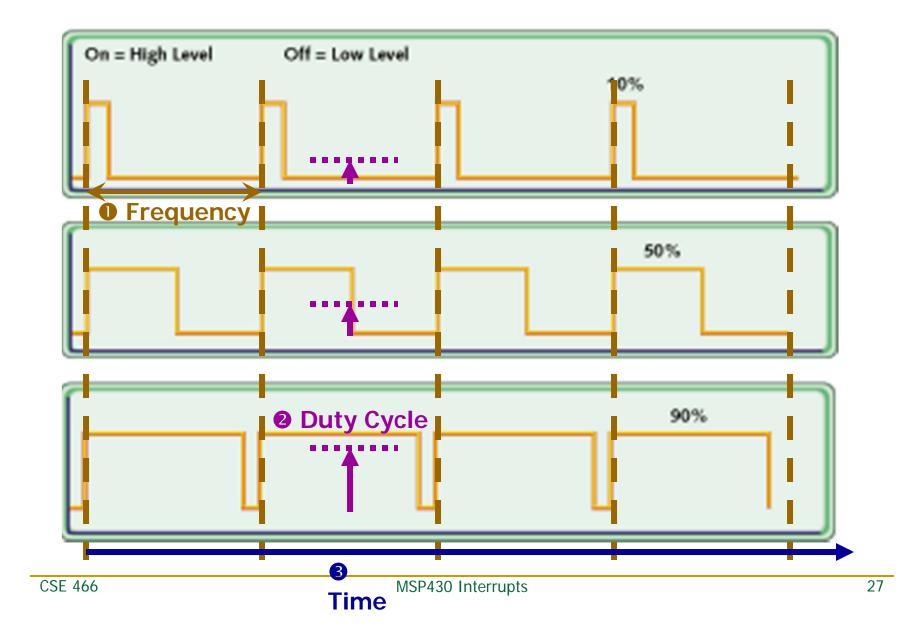

### Pulse Width Modulation (PWM)

- Pulse width modulation (PWM) is used to control analog circuits with a processor's digital outputs

- PWM is a technique of digitally encoding analog signal levels

- The duty cycle of a square wave is modulated to encode a specific analog signal level

- The PWM signal is still digital because, at any given instant of time, the full DC supply is either fully on or fully off

- The voltage or current source is supplied to the analog load by means of a repeating series of on and off pulses

- Given a sufficient bandwidth, any analog value can be encoded with PWM.

### **PWM Machines**

### PWM – Frequency/Duty Cycle

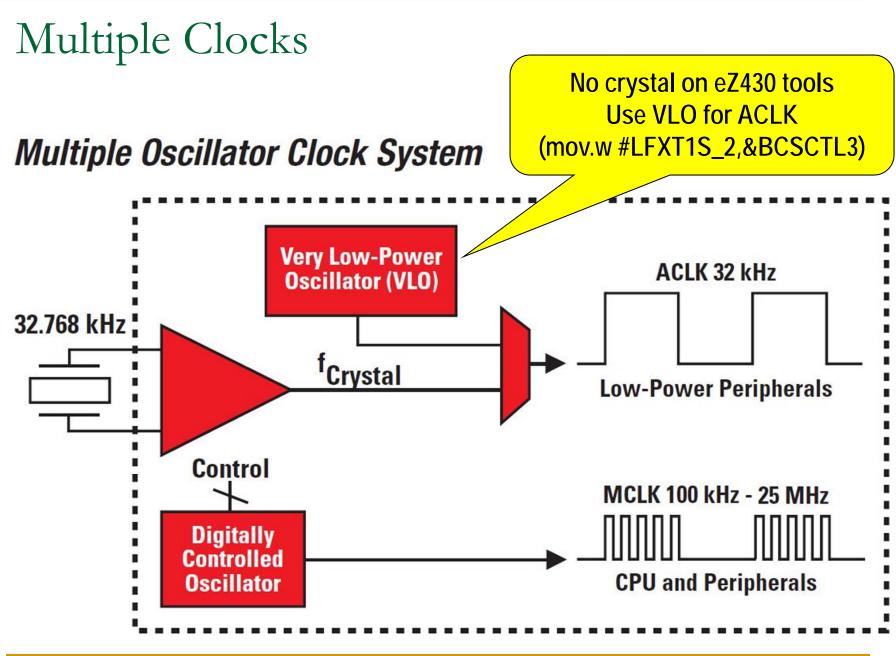

### Processor Clock Speeds

Often, the most important factor for reducing power consumption is slowing the clock down

- □ Faster clock = Higher performance, more power

- Slower clock = Lower performance, less power

#### Using assembly code:

; MSP430 Clock - Set DCO to 8 MHz: mov.b #CALBC1\_8MHZ,&BCSCTL1 ; Set range mov.b #CALDCO\_8MHZ,&DCOCTL ; Set DCO step + modulation

#### Using C code:

// MSP430 Clock - Set DCO to 8 MHz: BCSCTL1 = CALBC1\_8MHZ; // Set range 8MHz DCOCTL = CALDCO\_8MHZ; // Set DCO step + modulation

### Processor Clock Speeds

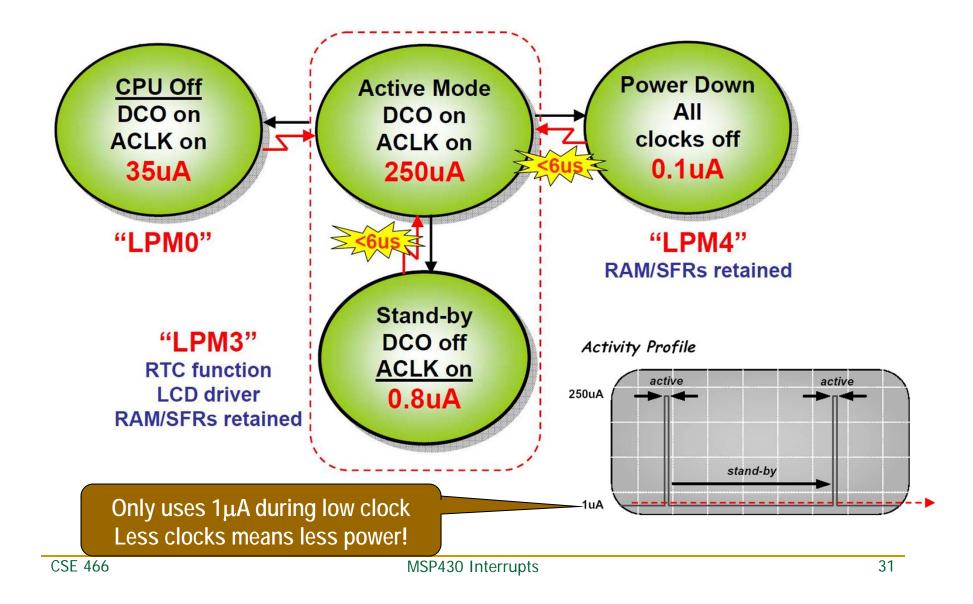

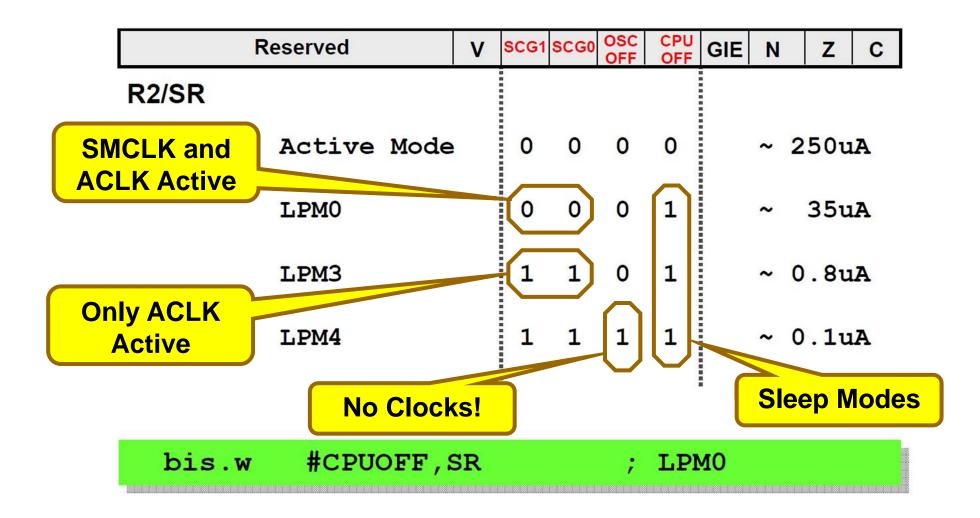

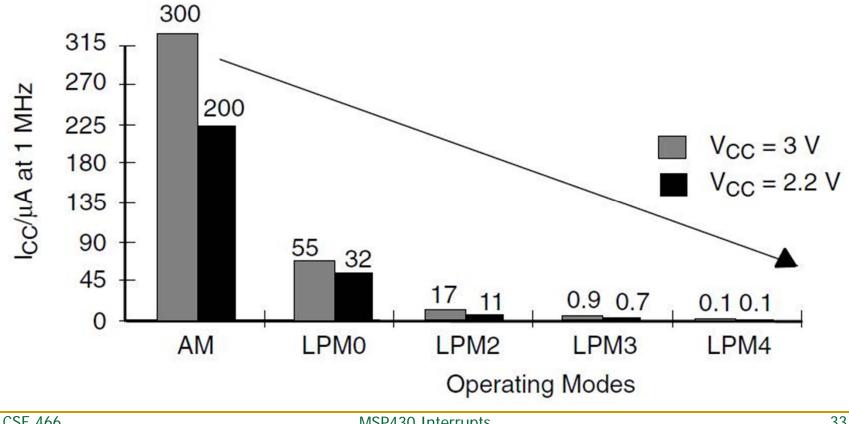

- Another method to reduce power consumption is to turn off some (or all) of the system clocks

- Active Mode (AM): CPU, all clocks, and enabled modules are active (≈300 µA)

- LPM0: CPU and MCLK are disabled, SMCLK and ACLK remain active (≈85 µA)

- LPM3: CPU, MCLK, SMCLK, and DCO are disabled; only ACLK remains active (≈1 µA)

- LPM4: CPU and all clocks disabled, RAM is retained (≈0.1 µA)

- A device is said to be <u>sleeping</u> when in low-power mode; <u>waking</u> refers to returning to active mode

### MSP430 Clock Modes

### Clocks Off Power Savings

Lower Power Savings

Finally, powering your system with lower voltages means lower power consumption as well

### Principles of Low-Power Apps

- Maximize the time in LPM3 mode

- Use interrupts to wake the processor

- Switch on peripherals only when needed

- Use low-power integrated peripherals

Timer\_A and Timer\_B for PWM

- Calculated branches instead of flag polling

- Fast table look-ups instead of calculations

- Avoid frequent subroutine and function calls

- Longer software routines should use single-cycle CPU registers

### Setting Low-Power Modes

- Setting low-power mode puts the microcontroller "to sleep" – so usually, interrupts would need to be enabled as well.

- Enter LPM3 and enable interrupts using assembly code:

- ; enable interrupts / enter low-power mode 3

bis.b #LPM3+GIE,SR ; LPM3 w/interrupts

- Enter LPM3 and enable interrupts using C code:

- // enable interrupts / enter low-power mode 3

\_\_\_\_bis\_SR\_register(LPM3\_\_bits + GIE);

### Timers

- System timing is fundamental for real-time applications

- The MSP430F2274 has 2 timers, namely Timer\_A and Timer\_B

- The timers may be triggered by internal or external clocks

- Timer\_A and Timer\_B also include multiple independent capture/compare blocks that are used for applications such as timed events and Pulse Width Modulation (PWM)

## Timers

- The main applications of timers are to:

- generate events of fixed time-period

- allow periodic wakeup from sleep of the device

- count transitional signal edges

- replace delay loops allowing the CPU to sleep between operations, consuming less power

- maintain synchronization clocks

# TxCTL Control Register

| 15              | 14                            | 13 | 12  | 11                                     | 10      | 9      | 8                                                                                                       | 7        | 6                                                                                        | 5               | 4 | 3     | 2    | 1     | 0  |

|-----------------|-------------------------------|----|-----|----------------------------------------|---------|--------|---------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------|-----------------|---|-------|------|-------|----|

|                 | (Used by Timer_B) TxSSELx     |    |     |                                        |         |        | IC                                                                                                      | Dx       | Μ                                                                                        | Сх              | - | TxCLR | TxIE | TxIFG |    |

| Bit Description |                               |    |     |                                        |         |        |                                                                                                         |          |                                                                                          |                 |   |       |      |       |    |

| 9-8             | TxSSELx Timer_x clock source: |    |     |                                        |         |        | $0 0 \Rightarrow TxCLK$<br>$0 1 \Rightarrow ACLK$<br>$1 0 \Rightarrow SMCLK$<br>$1 1 \Rightarrow INCLK$ |          |                                                                                          |                 |   |       |      |       |    |

| 7-6             | IDx                           |    | Clo | Clock signal divider:                  |         |        |                                                                                                         |          | $0 \Rightarrow / 1$<br>$1 \Rightarrow / 2$<br>$0 \Rightarrow / 4$<br>$1 \Rightarrow / 8$ | <u>2</u><br> -  |   |       |      |       |    |

| 5-4             | MC                            | x  | Clo | Clock timer operating mode:            |         |        |                                                                                                         | 0<br>1   |                                                                                          | p mod<br>ontinu |   |       |      |       |    |

| 2               | TxC                           | LR | Tin | Timer_x clear when TxCLR = 1           |         |        |                                                                                                         |          |                                                                                          |                 |   |       |      |       |    |

| 1               | TxI                           | Ξ  | Tin | Timer_x interrupt enable when TxIE = 1 |         |        |                                                                                                         |          |                                                                                          |                 |   |       |      |       |    |

| 0               | TxI                           | -G | Tin | ner_x i                                | interru | pt pen | ding w                                                                                                  | hen T    | xIFG =                                                                                   | 1               |   |       |      |       |    |

| CSE 46          | 66                            |    |     |                                        |         | N/IS   | SP430 In                                                                                                | torrunts |                                                                                          |                 |   |       |      |       | 38 |

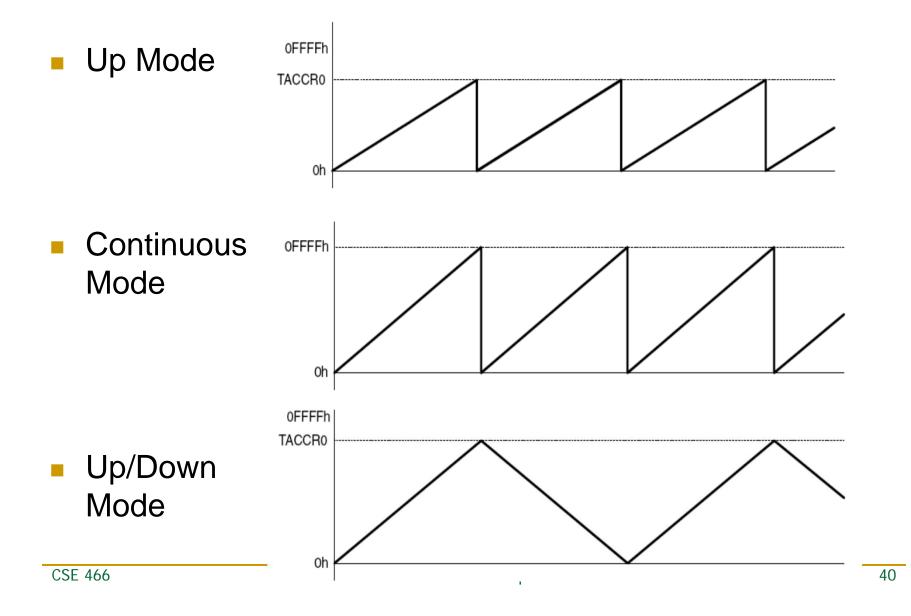

### 4 Modes of Operation

- Timer reset by writing a 0 to TxR

- Clock timer operating modes:

| MCx | Mode       | Description                                                                                        |

|-----|------------|----------------------------------------------------------------------------------------------------|

| 0 0 | Stop       | The timer is halted.                                                                               |

| 01  | Up         | The timer repeatedly counts from 0x0000 to the value in the TxCCR0 register.                       |

| 10  | Continuous | The timer repeatedly counts from 0x0000 to 0xFFFF.                                                 |

| 11  | Up/down    | The timer repeatedly counts from 0x0000 to the value in the TxCCR0 register and back down to zero. |

### Timer Modes

| 12.3.1 T | ACTL, Time                                                                                                                                      | r_A Control R                                                                                                  | egister                |                    |                    |                   |            |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------|--------------------|--------------------|-------------------|------------|--|--|

| 15       | 14                                                                                                                                              | 13                                                                                                             | 12                     | 11                 | 10                 | 9                 | 8          |  |  |

|          |                                                                                                                                                 | U                                                                                                              | nused                  |                    |                    | TAS               | SELx       |  |  |

| rw-(0)   | rw-(0)                                                                                                                                          | rw-(0)                                                                                                         | rw-(0)                 | rw-(0)             | rw-(0)             | rw-(0)            | rw-(0)     |  |  |

| 7        | 6                                                                                                                                               | 5                                                                                                              | 4                      | 3                  | 2                  | 1                 | 0          |  |  |

|          | IDx                                                                                                                                             |                                                                                                                | MCx                    | Unused             | TACLR              | TAIE              | TAIFG      |  |  |

| rw-(0)   | rw-(0)                                                                                                                                          | rw-(0)                                                                                                         | rw-(0)                 | rw-(0)             | rw-(0)             | rw-(0)            | rw-(0)     |  |  |

| Unused   | Bits 15-10                                                                                                                                      | Unused                                                                                                         |                        |                    |                    |                   |            |  |  |

| TASSELX  | Bits 9-8                                                                                                                                        | Timer_A clock sou                                                                                              | rce select             |                    |                    |                   |            |  |  |

|          |                                                                                                                                                 | 00 TACLK                                                                                                       |                        |                    |                    |                   |            |  |  |

|          |                                                                                                                                                 | 01 ACLK                                                                                                        |                        |                    |                    |                   |            |  |  |

|          |                                                                                                                                                 | 10 SMCLK                                                                                                       |                        |                    |                    |                   |            |  |  |

|          |                                                                                                                                                 | 11 INCLK (INCLK is device-specific and is often assigned to the inverted TBCLK) (s device-specific data sheet) |                        |                    |                    |                   |            |  |  |

| IDx      | Bits 7-6                                                                                                                                        | Input divider. These bits select the divider for the input clock.                                              |                        |                    |                    |                   |            |  |  |

|          |                                                                                                                                                 | 00 /1                                                                                                          |                        |                    |                    |                   |            |  |  |

|          |                                                                                                                                                 | 01 /2                                                                                                          |                        |                    |                    |                   |            |  |  |

|          |                                                                                                                                                 | 10 /4                                                                                                          |                        |                    |                    |                   |            |  |  |

|          |                                                                                                                                                 | 11 /8                                                                                                          |                        |                    |                    |                   |            |  |  |

| MCx      | Bits 5-4                                                                                                                                        |                                                                                                                | ng MCx = 00h whe       | -                  | n use conserves p  | ower.             |            |  |  |

|          |                                                                                                                                                 |                                                                                                                | e: the timer is halted |                    |                    |                   |            |  |  |

|          |                                                                                                                                                 |                                                                                                                | the timer counts up    |                    | 1.1                |                   |            |  |  |

|          |                                                                                                                                                 |                                                                                                                | s mode: the timer c    |                    |                    |                   |            |  |  |

|          | 014.0                                                                                                                                           |                                                                                                                | node: the timer cou    | nts up to TACCRI   | J then down to UUL | Jun.              |            |  |  |

| Unused   | Bit 3                                                                                                                                           | Unused                                                                                                         | tine this bit means 7  | AD the sleat divi  | dee and the sound  | disasting The TA  |            |  |  |

| TACLR    | Bit 2 Timer_A clear. Setting this bit resets TAR, the clock divider, and the count direction<br>automatically reset and is always read as zero. |                                                                                                                |                        |                    |                    | direction. The TA | CLR DIT IS |  |  |

| TAIE     | Bit 1                                                                                                                                           | Timer_A interrupt e                                                                                            | enable. This bit ena   | bles the TAIFG int | terrupt request.   |                   |            |  |  |

|          |                                                                                                                                                 | 0 Interrupt d                                                                                                  | isabled                |                    |                    |                   |            |  |  |

|          |                                                                                                                                                 | 1 Interrupt e                                                                                                  | nabled                 |                    |                    |                   |            |  |  |

| TAIFG    | Bit 0                                                                                                                                           | Timer_A interrupt f                                                                                            | -                      |                    |                    |                   |            |  |  |

|          |                                                                                                                                                 | 0 No interru                                                                                                   |                        |                    |                    |                   |            |  |  |

|          |                                                                                                                                                 | 1 Interrupt p                                                                                                  | ending                 |                    |                    |                   |            |  |  |

### TAR & TACCRx

### 12.3.2 TAR, Timer\_A Register

| 15                                                                         | 14     | 13     | 12     | 11     | 10     | 9      | 8      |  |  |

|----------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|--|--|

|                                                                            | TARx   |        |        |        |        |        |        |  |  |

| rw-(0)                                                                     | rw-(0) | rw-(0) | rw-(0) | rw-(0) | rw-(0) | rw-(0) | rw-(0) |  |  |

| 7                                                                          | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |  |

| TARx                                                                       |        |        |        |        |        |        |        |  |  |

| rw-(0)                                                                     | rw-(0) | rw-(0) | rw-(0) | rw-(0) | rw-(0) | rw-(0) | rw-(0) |  |  |

| TARx Bits 15-0 Timer_A register. The TAR register is the count of Timer_A. |        |        |        |        |        |        |        |  |  |

### 12.3.3 TACCRx, Timer\_A Capture/Compare Register x

| 15                                                                                                         | 14        | 13                                | 12                | 11                | 10               | 9                 | 8       |  |  |  |

|------------------------------------------------------------------------------------------------------------|-----------|-----------------------------------|-------------------|-------------------|------------------|-------------------|---------|--|--|--|

|                                                                                                            | TACCRx    |                                   |                   |                   |                  |                   |         |  |  |  |

| rw-(0)                                                                                                     | rw-(0)    | rw-(0)                            | rw-(0)            | rw-(0)            | rw-(0)           | rw-(0)            | rw-(0)  |  |  |  |

| 7                                                                                                          | 6         | 5                                 | 4                 | 3                 | 2                | 1                 | 0       |  |  |  |

|                                                                                                            | TACCRx    |                                   |                   |                   |                  |                   |         |  |  |  |

| rw-(0)                                                                                                     | rw-(0)    | rw-(0)                            | rw-(0)            | rw-(0)            | rw-(0)           | rw-(0)            | rw-(0)  |  |  |  |

| TACCRx                                                                                                     | Bits 15-0 | Timer_A capture/con               | npare register.   |                   |                  |                   |         |  |  |  |

| Compare mode: TACCRx holds the data for the comparison to the timer value in the Timer_A Register,<br>TAR. |           |                                   |                   |                   |                  |                   |         |  |  |  |

|                                                                                                            |           | Capture mode: The T<br>performed. | Timer_A Register, | TAR, is copied in | to the TACCRx re | gister when a cap | ture is |  |  |  |

## TACCTLx

#### 12.3.4 TACCTLx, Capture/Compare Control Register

| 15      | 14             | 13                                                                                                                                   | 12                          | 11                   | 10                   | 9                   | 8             |  |  |

|---------|----------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------|----------------------|---------------------|---------------|--|--|

|         | CMX            |                                                                                                                                      | CCISX                       | SCS                  | SCCI                 | Unused              | CAP           |  |  |

| rw-(0)  | rw-(0)         | rw-(0)                                                                                                                               | rw-(0)                      | rw-(0)               | r                    | r0                  | rw-(0)        |  |  |

| 7       | 6              | 5                                                                                                                                    | 4                           | 3                    | 2                    | 1                   | 0             |  |  |

|         | OUTMOD         | x                                                                                                                                    | CCIE                        | CCI                  | OUT                  | COV                 | CCIFG         |  |  |

| rw-(0)  | rw-(0)         | rw-(0)                                                                                                                               | rw-(0)                      | r                    | rw-(0)               | rw-(0)              | rw-(0)        |  |  |

| CMX     | Bit 15-14      | Capture mode                                                                                                                         |                             |                      |                      |                     |               |  |  |

|         |                | 00 No captur                                                                                                                         | e                           |                      |                      |                     |               |  |  |

|         |                | 01 Capture of                                                                                                                        | n rising edge               |                      |                      |                     |               |  |  |

|         |                |                                                                                                                                      | n falling edge              |                      |                      |                     |               |  |  |

|         |                |                                                                                                                                      | n both rising and fa        |                      |                      |                     |               |  |  |

| CCISX   | Bit 13-12      |                                                                                                                                      | input select. These         | bits select the TAC  | CRx Input signal.    | See the device-sp   | ecific data   |  |  |

|         |                | 00 CCIxA                                                                                                                             | signal connections.         |                      |                      |                     |               |  |  |

|         |                | 01 CCIXB                                                                                                                             |                             |                      |                      |                     |               |  |  |

|         |                | 10 GND                                                                                                                               |                             |                      |                      |                     |               |  |  |

|         |                | 11 Vcc                                                                                                                               |                             |                      |                      |                     |               |  |  |

| SCS     | Bit 11         |                                                                                                                                      | re course This bit I        | is used to synchron  | ize the canture in   | out signal with the | timer clock   |  |  |

| 303     | 04.11          | Synchronize capture source. This bit is used to synchronize the capture input signal with the timer clock.<br>0 Asynchronous capture |                             |                      |                      |                     |               |  |  |

|         |                | -                                                                                                                                    | ous capture                 |                      |                      |                     |               |  |  |

| SCCI    | Bit 10         | -,                                                                                                                                   | ture/compare input.         | The selected CCI     | Input signal is late | hed with the EQU:   | signal and c  |  |  |

|         |                | be read via this bi                                                                                                                  |                             |                      | ,,                   |                     |               |  |  |

| Unused  | Bit 9          | Unused. Read onl                                                                                                                     | y. Always read as 0         | ).                   |                      |                     |               |  |  |

| CAP     | Bit 8          | Capture mode                                                                                                                         |                             |                      |                      |                     |               |  |  |

|         |                | 0 Compare                                                                                                                            | mode                        |                      |                      |                     |               |  |  |

|         |                | 1 Capture r                                                                                                                          | node                        |                      |                      |                     |               |  |  |

| OUTMODX | Bits 7-5       | Output mode. Mod                                                                                                                     | les 2, 3, 6, and 7 ar       | e not useful for TA  | CCR0, because E      | QUX - EQUD.         |               |  |  |

|         |                | 000 OUT bit value                                                                                                                    |                             |                      |                      |                     |               |  |  |

|         |                | 001 Set                                                                                                                              |                             |                      |                      |                     |               |  |  |

|         |                | 010 Toggle/re                                                                                                                        | set                         |                      |                      |                     |               |  |  |

|         |                | 011 Set/reset                                                                                                                        |                             |                      |                      |                     |               |  |  |

|         |                | 100 Toggle                                                                                                                           |                             |                      |                      |                     |               |  |  |

|         |                | 101 Reset                                                                                                                            |                             |                      |                      |                     |               |  |  |

|         |                | 110 Toggle/se                                                                                                                        |                             |                      |                      |                     |               |  |  |

|         |                | 111 Reset/set                                                                                                                        |                             |                      |                      |                     |               |  |  |

| CCIE    | Bit 4          |                                                                                                                                      | Interrupt enable. Th        | is bit enables the l | nterrupt request of  | the corresponding   | g CCIFG flag. |  |  |

|         |                | 0 Interrupt                                                                                                                          |                             |                      |                      |                     |               |  |  |

|         |                | 1 Interrupt                                                                                                                          |                             |                      | and he like hit      |                     |               |  |  |

| OUT     | Bit 3<br>Bit 2 |                                                                                                                                      | input. The selected         |                      |                      |                     |               |  |  |

| 001     | DIL 2          |                                                                                                                                      | mode 0, this bit dir        | ecuy controis the s  | tate of the output.  |                     |               |  |  |

|         |                |                                                                                                                                      |                             |                      |                      |                     |               |  |  |

| COV     | Bit 1          |                                                                                                                                      |                             | conturo cuorfore o   | coursed COV mus      | t he recet with cel | the second    |  |  |

| cov     | Dit 1          | t 1 Capture overflow. This bit indicates a capture overflow occurred. COV must be reset with soft<br>0 No capture overflow occurred  |                             |                      |                      |                     |               |  |  |

|         |                |                                                                                                                                      |                             |                      |                      |                     |               |  |  |

|         |                | 1 Cashies a                                                                                                                          | A DOMESTIC OF A DOMESTIC OF |                      |                      |                     |               |  |  |

| COIEC   | 870            |                                                                                                                                      | verflow occurred            |                      |                      |                     |               |  |  |

| CCIFG   | Bit 0          | Capture/compare                                                                                                                      |                             |                      |                      |                     |               |  |  |

## OUTMOD

### Table 12-2. Output Modes

| OUTMODx | Mode         | Description                                                                                                                                                                     |

|---------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000     | Output       | The output signal OUTx is defined by the OUTx bit. The OUTx signal updates immediately when OUTx is updated.                                                                    |

| 001     | Set          | The output is set when the timer <i>counts</i> to the TACCRx value. It remains set until a reset of the timer, or until another output mode is selected and affects the output. |

| 010     | Toggle/Reset | The output is toggled when the timer <i>counts</i> to the TACCRx value. It is reset when the timer <i>counts</i> to the TACCR0 value.                                           |

| 011     | Set/Reset    | The output is set when the timer <i>counts</i> to the TACCRx value. It is reset when the timer <i>counts</i> to the TACCR0 value.                                               |

| 100     | Toggle       | The output is toggled when the timer <i>counts</i> to the TACCRx value. The output period is double the timer period.                                                           |

| 101     | Reset        | The output is reset when the timer <i>counts</i> to the TACCRx value. It remains reset until another output mode is selected and affects the output.                            |

| 110     | Toggle/Set   | The output is toggled when the timer <i>counts</i> to the TACCRx value. It is set when the timer <i>counts</i> to the TACCR0 value.                                             |

| 111     | Reset/Set    | The output is reset when the timer <i>counts</i> to the TACCRx value. It is set when the timer<br><i>counts</i> to the TACCR0 value.                                            |

Configuring PWM

PWM can be configured to appear on TA1 pins PxSEL.x that chooses which pin TA1 connects to

## TAIV

### 12.3.5 TAIV, Timer\_A Interrupt Vector Register

| 15               | 14                                       | 13    | 12             | 11                    | 10    | 9     | 8  |

|------------------|------------------------------------------|-------|----------------|-----------------------|-------|-------|----|

| 0                | 0                                        | 0     | 0              | 0                     | 0     | 0     | 0  |

| rO               | r0                                       | r0    | r0             | rO                    | r0    | r0    | rO |

| 7                | 6                                        | 5     | 4              | 3                     | 2     | 1     | 0  |

| 0                | 0                                        | 0     | 0              |                       | TAIVx |       | 0  |

| rO               | r0                                       | r0    | r0             | r-(0)                 | r-(0) | r-(0) | rO |

| TAIVx            | Bits 15-0 Timer_A interrupt vector value |       |                |                       |       |       |    |

| TAIV<br>Contents | Interrupt Source                         |       | Interrupt Flag | Interrupt<br>Priority |       |       |    |

| 00h              | No interrupt pe                          | nding | <b>1</b> -     |                       |       |       |    |

| 00h | No interrupt pending             | -            |         |

|-----|----------------------------------|--------------|---------|

| 02h | Capture/compare 1                | TACCR1 CCIFG | Highest |

| 04h | Capture/compare 2 <sup>(1)</sup> | TACCR2 CCIFG |         |

| 06h | Reserved                         | -            |         |

| 08h | Reserved                         | -            |         |

| 0Ah | Timer overflow                   | TAIFG        |         |

| 0Ch | Reserved                         | -            |         |

| 0Eh | Reserved                         | -            | Lowest  |

(1) Not implemented in MSP430x20xx devices

### Msp430x20x3\_ta\_16.c

### PWM without the processor!

```

#include <msp430x20x3.h>

void main(void)

{

WDTCTL = WDTPW + WDTHOLD;

P1DIR |= 0x0C;

P1SEL |= 0x0C;

CCR0 = 512-1;

CCTL1 = OUTMOD_7;

CCR1 = 384;

TACTL = TASSEL_2 + MC_1;

_BIS_SR(CPUOFF);

```

- // Stop WDT

- // P1.2 and P1.3 output

- // PWM Period

- // CCR1 reset/set

- // CCR1 PWM duty cycle

- // SMCLK, up mode

- // Enter LPM0

## End of lecture

Bonus example

```

// MSP430F20x3 Demo - SD16A, Sample A1+ Continuously, Set P1.0 if > 0.3V #include <msp430x20x3.h>

```

```

void main(void)

{

WDTCTL = WDTPW + WDTHOLD;

P1DIR = 0x01;

SD16CTL = SD16REFON + SD16SSEL 1;

SD16INCTL0 = SD16INCH 1;

SD16CCTL0 = SD16UNI + SD16IE;

SD16AE = SD16AE2:

SD16CCTL0 = SD16SC;

_BIS_SR(LPM0_bits + GIE);

}

#pragma vector = SD16_VECTOR

_interrupt void SD16ISR(void)

{

if (SD16MEMO < 0x7FF)

P1OUT &= -0x01;

else

P1OUT = 0x01;

}

```

```

// Stop watchdog timer

// Set P1.0 to output direction

// 1.2V ref, SMCLK

// A1+/-

// 256OSR, unipolar, interrupt enable

// P1.1 A1+, A1- = VSS

// Set bit to start conversion

```

```

// SD16MEM0 > 0.3V?, clears IFG

```