| ADC Multiplexer Selection<br>Register – ADMUX | Bit 7 6 5 4 3 2 1 0<br>ReadWrite<br>Initial Value 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                               | Table 83. Voltage Reference Selections for ADC REFS1 REFS0 Voltage Reference Selection                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                                               | 0 0 AREF. Internal Viet turned off                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                                               | 0 1 AVCC with external capacitor at AREF pin                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                                               | 1 0 Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                                               | 1 1 Internal 2.56V Voltage Reference with external capacitor at AREF                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

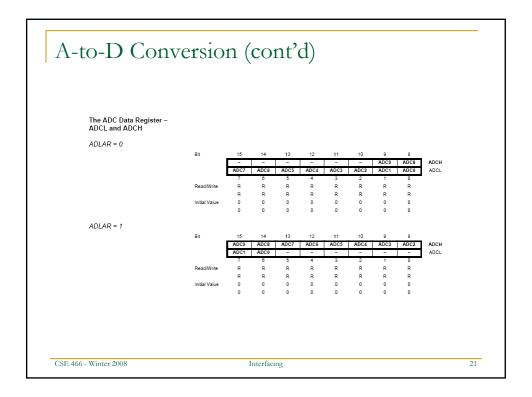

|                                               | <ul> <li>Bit 5 – ADLAR: ADC Left Adjust Result</li> <li>The ADLAR bit affects the presentation of the ADC conversion result in the ADC Data<br/>Register. Write one to ADLAR to left adjust the result. Otherwise, the result is righ<br/>adjusted. Chanarian the ADLAR bit will affect the ADC Data Recister immediately<br/>regardless of any ongoing conversions. For a complete description of this bit, see "The<br/>ADC Data Register – ADCL and ADCH" on page 218.</li> </ul> |  |  |  |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                             |            | ,                                                        |  |  |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------|----------------------------------------------------------|--|--|

| Special FunctionIO Register<br>SFIOR |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                             |            |                                                          |  |  |

| SHOK                                 | Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7 6<br>ADTS2   ADTS1                        | 5<br>ADTS0 | 4 3 2 1 D<br>- ACME   PUD   PSR2   PSR10   SFIOR         |  |  |

|                                      | Read/Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W R/W                                     | R/W        | R R/W R/W R/W R/W                                        |  |  |

|                                      | Initial Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0 0                                         | 0          | 0 0 0 0 0                                                |  |  |

|                                      | • Bit 7:5 – A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Bit 7:5 – ADT\$2:0: ADC Auto Trigger Source |            |                                                          |  |  |

|                                      | trigger an ADC conversion. If ADATE is cleared, the ADTS2.0 settings will have no<br>effect. A conversion will be triggered by the rising edge of the selected Interrupt Flag.<br>Note that switching from a trigger source that is cleared to a trigger source that is set,<br>will generate a positive edge on the trigger signal. If ADEN in ADCSRA is set, this will<br>start a conversion. Switching to Free Running mode (ADTS[2:0]=0) will not cause a trig-<br>ger event, even if the ADC Interrupt Flag is set.<br>Table 86. ADC Auto Trigger Source Selections |                                             |            |                                                          |  |  |

|                                      | ADTS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ADTS1                                       | ADTS0      | Trigger Source                                           |  |  |

|                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                           | 0          | Free Running mode                                        |  |  |

|                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                           | 1          | Analog Comparator                                        |  |  |

|                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                           | 0          | External Interrupt Request 0                             |  |  |

|                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                           | 1          | Timer/Counter0 Compare Match                             |  |  |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                           | 0          | Timer/Counter0 Overflow                                  |  |  |

|                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                             |            |                                                          |  |  |

|                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                           | 1          | Timer/Counter Compare Match B                            |  |  |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                           | 1          | Timer/Counter Compare Match B<br>Timer/Counter1 Overflow |  |  |

|                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -                                           |            |                                                          |  |  |