# Interrupts

- Fundamental concept in computation

- Interrupt execution of a program to "handle" an event

- Don't have to rely on program relinquishing control

- Can code program without worrying about others

- Issues

- What can interrupt and when?

- Where is the code that knows what to do?

- How long does it take to handle interruption?

- Can an interruption be, in turn, interrupted?

- How does the interrupt handling code communicate its results?

- How is data shared between interrupt handlers and programs?

CSE 466 - Winter 2008

Interrupts

- 1

# What is an Interrupt?

- Reaction to something in I/O (human, comm link)

- Usually asynchronous to processor activities

- "interrupt handler" or "interrupt service routine" (ISR) invoked to take care of condition causing interrupt

- Change value of internal variable (count)

- Read a data value (sensor, receive)

- Write a data value (actuator, send)

CSE 466 - Winter 2008

Interrupts

# Interrupts

Code sample that does not interrupt

```

char SPI_SlaveReceive(void)

{

/* Wait for reception complete */

while(!(SPSR & (1<<SPIF)))

;

/* Return data register */

return SPDR;

}</pre>

```

Instead of busy waiting until a byte is received the processor can generate an interrupt when it sets SPIF

```

SIGNAL(SIG_SPI) {

RX_Byte = SPDR

}

```

CSE 466 - Winter 2008

Interrupts

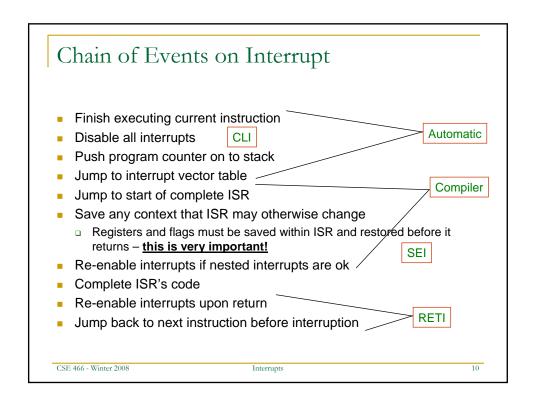

# Saving and Restoring Context

- Processor and compiler dependent

- Where to find ISR code?

- Different interrupts have separate ISRs

- Who does dispatching?

- Direct

- Different address for each interrupt type

- Supported directly by processor architecture

- Indirect

- One top-level ISR

- Switch statement on interrupt type

- A mix of these two extremes?

CSE 466 - Winter 2008

Interrupts

# Saving and Restoring Context

- How much context to save?

- Registers, flags, program counter, etc.

- Save all or part?

- Agreement needed between ISR and program

- Where should it be saved?

- Stack, special memory locations, shadow registers, etc.

- How much room will be needed on the stack?

- Nested interrupts may make stack reach its limit what then?

- Restore context when ISR completes

CSE 466 - Winter 2008

Interrupts

5

# Ignoring Interrupts

- Can interrupts be ignored?

- It depends on the cause of the interrupt

- No, for nuclear power plant temperature warning

- Yes, for keypad on cell phone (human timescale is long)

- When servicing another interrupt

- Ignore others until done

- Can't take too long keep ISRs as short as possible

- Just do a quick count, or read, or write not a long computation

- Interrupt disabling

- Will ignored interrupt "stick"?

- Rising edge sets a flip-flop

- Or will it be gone when you get to it?

- Level changes again and its as if it never happened

- Don't forget to re-enable

CSE 466 - Winter 2008

Interrupts

# Prioritizing Interrupts

- When multiple interrupts happen simultaneously

- Which is serviced first?

- Fixed or flexible priority?

- Priority interrupts

- Higher priority can interrupt

- Lower priority can't

- Maskable interrupts

- "don't bother me with that right now"

- Not all interrupts are maskable, some are non-maskable

CSE 466 - Winter 2008

Interrupts

# Interrupts in the ATmega16

- External interrupts

- □ From I/O pins of microcontroller

- Internal interrupts

- Timers

- Output compare

- Input capture

- Overflow

- Communication units

- Receiving something

- Done sending

- ADC

- Completed conversion

CSE 466 - Winter 2008

Interrupts

### Interrupt Jump Vector Table ; Reset Handler ; IRQO Handler \$004 EXT INT1 ; IRQ1 Handler ; Timer2 Compare Handler jmp jmp TIM2 COMP \$006 Fixed location TIM2\_OVF ; Timer2 Overflow Handler SOOA qmt qmt TIM1\_CAPT ; Timer1 Capture Handler in memory to find TIM1 COMPA ; Timer1 CompareA Handler \$00C jmp TIM1\_COMPB ; Timer1 CompareB Handler first instruction for \$010 TIM1 OVF : Timer1 Overflow Handler \$012 jmp TIMO\_OVF ; Timero Overflow Handler each type of jmp SPI\_STC ; SPI Transfer Complete Handler \$016 jmp USART\_RXC ; USART RX Complete Handler interrupt \$018 jmp USART\_UDRE ; UDR Empty Handler jmp USART\_TXC ; USART TX Complete Handler jmp ADC jmp EE\_RDY Only room for one \$01C ; ADC Conversion Complete Handler ; EEPROM Ready Handler \$01E jmp ANA\_C ANA\_COMP ; Analog Comparator Handler instruction \$022 : Two-wire Serial Interface Handler jmp EXT\_INT2 ; IRQ2 Handler \$024 JMP to location ; TimerO Compare Handler of complete ISR \$028 SPM\_RDY ; Store Program Memory Ready Handler ldi r16,high(RAMEND) ; Main program start ; Set Stack Pointer to top of RAM \$02B out SPH, r16 ldi r16,low(RAMEND) \$02C ; Enable interrupts \$02E sei \$02F <instr> xxx CSE 466 - Winter 2008 Interrupts

# Shared Data Problem

- When you use interrupts you create the opportunity for multiple sections of code to update a variable.

- This might cause a problems in your logic if an interrupt updates a variable between two lines of code that are directly dependent on each other (e.g. if statement)

- One solution is to create critical sections where you disable the interrupts for a short period of time while you complete your logic on the shared variable

```

cli();

.....critical section code goes here.....

sei();

```

CSE 466 - Winter 2008

Interrupts

11

# External Interrupts

General Interrupt Contro Register – GICR

- Special pins: INT0, INT1, INT2

- Can interrupt on edge or level

- Can interrupt even if set to be output pins

- Implements "software interrupts" by setting output

MCU Control Register – MCUCR The MCU Control Register contains control bits for interrupt sense control and general MCU functions.

| Bit           | 7   | 6   | 5   | 4   | 3     | 2     | 1     | 0     |       |

|---------------|-----|-----|-----|-----|-------|-------|-------|-------|-------|

|               | SM2 | SE  | SM1 | SM0 | ISC11 | ISC10 | ISC01 | ISC00 | MCUCR |

| Read/Write    | R/W | R/W | RW  | R/W | R/W   | R/W   | R/W   | R/W   | •     |

| Initial Value | 0   | 0   | 0   | 0   | 0     | 0     | 0     | 0     |       |

| ISC11 | ISC10 | Description                                                |

|-------|-------|------------------------------------------------------------|

| 0     | 0     | The low level of INT1 generates an interrupt request.      |

| 0     | 1     | Any logical change on INT1 generates an interrupt request. |

| 1     | 0     | The falling edge of INT1 generates an interrupt request.   |

| 1     | 1     | The rising edge of INT1 generates an interrupt request.    |

CSE 466 - Winter 2008

Interrupts

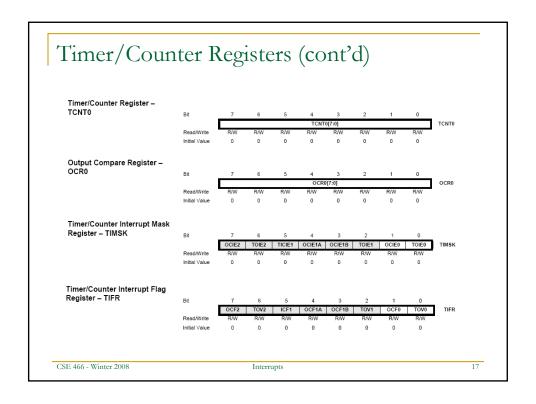

# Closer Look at a Timer/Counter Timer0/Counter0 Clear timer on compare match (auto reload) Prescaler (divide clock by up to 1024) Overflow and compare match interrupts Registers Configuration Count value Output compare value Interrupts CSE 466 - Winter 2008 Interrupts Interrupts

# Timer/Counter Registers

Timer/Counter Control Register TCCR0

### Bit 7 – FOC0: Force Output Compare

The FOCO bit is only active when the WGM00 bit specifies a non-PWM mode. However, for ensuring compatibility with future devices, this bit must be set to zero when TCCR0 is written when operating in PWM mode. When writing a logical one to the FOCO bit, an immediate compare match is forced on the Waveform Generation unit. The CCO output is changed according to its CoM01.0 bits setting, Note that the FOCO bit is implemented as a strobe. Therefore it is the value present in the COM01.0 bits that determines the effect of the forced compare.

A FOC0 strobe will not generate any interrupt, nor will it clear the timer in CTC mode using OCR0 as TOP.

The FOC0 bit is always read as zero.

### Bit 6, 3 – WGM01:0: Waveform Generation Mode

These bits control the counting sequence of the counter, the source for the maximum (TOP) counter value, and what type of Waveform Generation to be used. Modes of operation supported by the Timer/Counter unit are: Normal mode, Cleor Timer on Compare Match (CTC) mode, and two types of Pulse Width Modulation (PWM) modes. See Table 38 and "Modes of Operation" on page 74.

Table 38. Waveform Generation Mode Bit Description

| N | fode | WGM01<br>(CTC0) | WGM00<br>(PWM0) | Timer/Counter Mode<br>of Operation | тор  | Update of<br>OCR0 | TOV0 Flag<br>Set-on |

|---|------|-----------------|-----------------|------------------------------------|------|-------------------|---------------------|

|   | 0    | 0               | 0               | Normal                             | 0xFF | Immediate         | MAX                 |

|   | 1    | 0               | - 1             | PWM, Phase Correct                 | 0xFF | TOP               | воттом              |

| Г | 2    | 1               | 0               | CTC                                | OCR0 | Immediate         | MAX                 |

| Г | 3    | 1               | - 1             | Fast PWM                           | 0xFF | TOP               | MAX                 |

The CTC0 and PWM0 bit definition names are now obsolete. Use the WGM01:0 definitions. However, the functionality and location of these bits are compatible with previous versions of the timer.

CSE 466 - Winter 2008

Interrupts

# Timer/Counter Registers (cont'd)

## Timer/Counter Control Register TCCR0

### Bit 5:4 - COM01:0: Compare Match Output Mode

These bits control the Output Compare pin (OC0) behavior. If one or both of the COM01:0 bits are set, the OC0 output overrides the normal port functionality of the I/O pin it is connected to. However, note that the Data Direction Register (DDR) bit corresponding to the OC0 pin must be set in order to enable the output driver.

When OC0 is connected to the pin, the function of the COM01:0 bits depends on the WGM01:0 bit setting. Table 39 shows the COM01:0 bit functionality when the WGM01:0 bits are set to a normal or CTC mode (non-PWM).

Table 39. Compare Output Mode, non-PWM Mode

| COM01 | COM00 | Description                              |

|-------|-------|------------------------------------------|

| 0     | 0     | Normal port operation, OC0 disconnected. |

| 0     | 1     | Toggle OC0 on compare match              |

| 1     | 0     | Clear OC0 on compare match               |

| 1     | 1     | Set OC0 on compare match                 |

CSE 466 - Winter 2008

Interrupts

15

# Timer/Counter Registers (cont'd)

# Timer/Counter Control Register

### TCCR0

Bit 2:0 – CS02:0: Clock Select

The three Clock Select bits select the clock source to be used by the Timer/Counter. **Table 42.** Clock Select Bit Description

| CS02 | CS01 | CS00 | Description                                             |

|------|------|------|---------------------------------------------------------|

| 0    | 0    | 0    | No clock source (Timer/Counter stopped).                |

| 0    | 0    | 1    | clk <sub>I/O</sub> /(No prescaling)                     |

| 0    | 1    | 0    | clk <sub>I/O</sub> /8 (From prescaler)                  |

| 0    | 1    | 1    | clk <sub>I/O</sub> /64 (From prescaler)                 |

| 1    | 0    | 0    | clk <sub>I/O</sub> /256 (From prescaler)                |

| 1    | 0    | 1    | Clk <sub>I/O</sub> /1024 (From prescaler)               |

| 1    | 1    | 0    | External clock source on T0 pin. Clock on falling edge. |

| 1    | 1    | 1    | External clock source on T0 pin. Clock on rising edge.  |

If external pin modes are used for the Timer/Counter0, transitions on the T0 pin will clock the counter even if the pin is configured as an output. This feature allows software control of the counting.

CSE 466 - Winter 2008

Interrupts

# Setting Register Values

- Defined names for each register and bit

- Set timer to clear on match

- Set prescaler to 1024

Set count value to compare against

$$OCR0 = 150;$$

Set timer to interrupt when it reaches count

$$TIMSK = (1 << OCIE0);$$

CSE 466 - Winter 2008

Interrupts

# Writing an Interrupt Handler in C

- Set and clear interrupt enable

- sei();

- cli();

- Interrupt handler

- Setting I/O registers

- □ TCCR0 = (1<<WGM01) | (1<<CS02) | (1<<CS00);

- Enabling specific interrupts

- □ TIMSK = (1<<OCIE0);

CSE 466 - Winter 2008

Interrupts

19

# Writing an Interrupt Handler in C (cont'd)

- Ensure main program sets up all registers

- Enable interrupts as needed

- Enable global interrupts (SEI)

- Write handler routine for each enabled interrupt

- What if an interrupt occurs and a handler isn't defined?

- Make sure routine does not disrupt others

- Data sharing problem

- Save any state that might be changed (done by compiler)

- Re-enable interrupts upon return

- Done by compiler with RETI

CSE 466 - Winter 2008

Interrupts

# Power modes

- Processor can go to "sleep" and save power

- Different modes put different sets of modules to sleep

- Which one to use depends on which modules are needed to wake up processor

- □ Timers, external interrupts, ADC, serial communication lines, etc.

- set\_sleep\_mode (mode);

- sleep\_mode ();

CSE 466 - Winter 2008

Interrupts

21

# Power modes (cont'd)

MCU Control Register – MCUCR The MCU Control Register contains control bits for power management.

• Bits 7, 5, 4 - SM2..0: Sleep Mode Select Bits 2, 1, and 0

These bits select between the six available sleep modes as shown in Table 13.

Table 13. Sleep Mode Select

| SM2 | SM1 | SM0 | Sleep Mode                      |

|-----|-----|-----|---------------------------------|

| 0   | 0   | 0   | Idle                            |

| 0   | 0   | 1   | ADC Noise Reduction             |

| 0   | 1   | 0   | Power-down                      |

| 0   | 1   | 1   | Power-save                      |

| 1   | 0   | 0   | Reserved                        |

| 1   | 0   | 1   | Reserved                        |

| 1   | 1   | 0   | Standby <sup>(1)</sup>          |

| 1   | 1   | 1   | Extended Standby <sup>(1)</sup> |

Note: 1. Standby mode and Extended Standby mode are only available with external crystals or resonators.

Bit 6 – SE: Sleep Enable

The SE bit must be written to logic one to make the MCU enter the sleep mode when the SLEEP instruction is executed. To avoid the MCU entering the sleep mode unless it is the programmers purpose, it is recommended to write the Sleep Enable (SE) bit to one just before the execution of the SLEEP instruction and to clear it immediately after waking up.

CSE 466 - Winter 2008

Interrupts

# Power modes (cont'd)

Wake up sources and active clocks

| Sleep<br>Mode                           | Active Clock domains |                      |                   |                    |                    | Oscillators                  |                       |                      | Wake-up Sources         |                  |                          |     |              |

|-----------------------------------------|----------------------|----------------------|-------------------|--------------------|--------------------|------------------------------|-----------------------|----------------------|-------------------------|------------------|--------------------------|-----|--------------|

|                                         | clk <sub>cpu</sub>   | clk <sub>flash</sub> | clk <sub>io</sub> | clk <sub>adc</sub> | clk <sub>ASY</sub> | Main Clock<br>Source Enabled | Timer Osc.<br>Enabled | INT2<br>INT1<br>INT0 | TWI<br>Address<br>Match | Timer<br>2       | SPM /<br>EEPROM<br>Ready | ADC | Other<br>I/O |

| ldle                                    |                      |                      | Х                 | Х                  | Х                  | Х                            | X <sup>(2)</sup>      | Х                    | Х                       | Х                | Х                        | Х   | Х            |

| ADC<br>Noise<br>Redu-<br>ction          |                      |                      |                   | х                  | x                  | х                            | X <sup>(2)</sup>      | X <sup>(3)</sup>     | Х                       | х                | х                        | x   |              |

| Power<br>Down                           |                      |                      |                   |                    |                    |                              |                       | X <sup>(3)</sup>     | х                       |                  |                          |     |              |

| Power<br>Save                           |                      |                      |                   |                    | X <sup>(2)</sup>   |                              | X <sup>(2)</sup>      | X <sup>(3)</sup>     | х                       | X <sup>(2)</sup> |                          |     |              |

| Standby <sup>(1)</sup>                  |                      |                      |                   |                    |                    | X                            |                       | X <sup>(3)</sup>     | Х                       |                  |                          |     |              |

| Exten-<br>ded<br>Standby <sup>(1)</sup> |                      |                      |                   |                    | X <sup>(2)</sup>   | х                            | X <sup>(2)</sup>      | X <sup>(3)</sup>     | х                       | X <sup>(2)</sup> |                          |     |              |

Notes: 1. External Crystal or resonator selected as clock source.

2. If AS2 bit in ASSR is set.

3. Only INT2 or level interrupt INT1 and INT0.

CSE 466 - Winter 2008

Interrupts