### Computational hardware

- Digital logic (CSE370)

- Gates and flip-flops: glue logic, simple FSMs, registers

- □ Two-level PLDs: FSMs, muxes, decoders

- Programmable logic devices (CSE370, CSE467)

- □ Field-programmable gate arrays: FSMs, basic data-paths

- Mapping algorithms to hardware

- Microprocessors (CSE378)

- General-purpose computer

- Instructions can implement complex control structures

- Supports computations/manipulations of data in memory

CSE 466 Microcontrollers

### Microprocessors

- Arbitrary computations

- Arbitrary control structures

- Arbitrary data structures

- Specify function at high-level and use compilers and debuggers

- Microprocessors can lower hardware costs

- If function requires too much logic when implemented with gates/FFs

- Operations are too complex, better broken down as instructions

- Lots of data manipulation (memory)

- □ If function does not require higher performance of customized logic

- Ever-increasing performance of processors puts more and more applications in this category

- Minimize the amount of external logic

### Microprocessor basics

- Composed of three parts

- Data-path: data manipulation and storage

- Control: determines sequence of actions executed in data-path and interactions to be had with environment

- $\hfill \square$  Interface: signals seen by the environment of the processor

- Instruction execution engine: fetch/execute cycle

- Flow of control determined by modifications to program counter

- Instruction classes:

- Data: move, arithmetic and logical operations

- Control: branch, loop, subroutine call

- Interface: load, store from external memory

CSE 466

icrocontrolle

### Microprocessor basics (cont'd)

- Can implement arbitrary state machine with auxiliary data-path

- Control instructions implement state diagram

- Registers and ALUs act as data storage and manipulation

- Interaction with the environment through memory interface

How are individual signal wires sensed and controlled?

CSE 466 Microcontroller

### Microprocessor organization

- Controller

- Inputs: from ALU (conditions), instruction read from memory

- Outputs: select inputs for registers, ALU operations, read/write to memory

- Data-path

- Register file to hold data

- Arithmetic logic unit to manipulate data

- Program counter (to implement relative jumps and increments)

- Interface

- Data to/from memory (address and data registers in data path)

- Read/write signals to memory (from control)

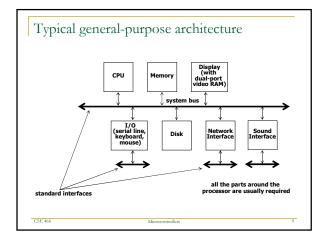

### General-purpose processor

- Programmed by user

- New applications are developed routinely

- General-purpose

- Must handle a wide ranging variety of applications

- Interacts with environment through memory

- All devices communicate through memory data

- $\hfill \square$  DMA operations between disk and I/O devices

- □ Dual-ported memory (e.g., display screen)

- □ Generally, oblivious to passage of time

Y . . B

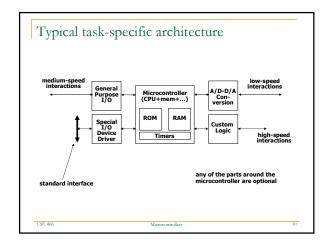

### Embedded processor

- Typically programmed once by manufacturer of system

- Rarely does the user load new software

- Executes a single program (or a limited suite) with few parameters

- Task-specific

- Can be optimized for a specific application

- Interacts with environment in many ways

- Direct sensing and control of signal wires

- Communication protocols to environment and other devices

- Real-time interactions and constraints

- Power-saving modes of operation to conserve battery power

CSE 466 Microcontro

### Why embedded processors?

- High overhead in building a general-purpose system

- Storing/loading programs

- Operating system manages running of programs and access to data

- □ Shared system resources (e.g., system bus, large memory)

- Many parts

- Communication through shared memory/bus

- Each I/O device often requires its own separate hardware unit

- Optimization opportunities

- As much hardware as necessary for application

- Cheaper, portable, lower-power systems

- As much software as necessary for application

- Doesn't require a complete OS, get a lot done with a smaller processor

- Can integrate processor, memory, and I/O devices on to a single chip

### How does this change things?

- Sense and control of environment

- □ Processor must be able to "read" and "write" individual wires

- Controls I/O interfaces directly

- Measurement of time

- Many applications require precise spacing of events in time

- Reaction times to external stimuli may be constrained

- Communication

- Protocols must be implemented by processor

- □ Integrate I/O device or emulate in software

- Capability of using external device when necessary

T. W.

### Interactions with the environment

- Basic processor only has address and data busses to memory

- Inputs are read from memory

- Outputs are written to memory

- Thus, for a processor to sense/control signal wires in the environment they must be made to appear as memory bits

- How do we make wires look like memory?

CCF 4/4

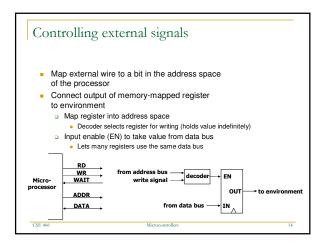

# Sensing external signals - Map external wire to a bit in the address space of the processor - External register or latch buffers values coming from environment - Map register into address space - Decoder selects register for reading - Output enable (OE) to get value on to data bus - Lets many registers use the same data bus - RD - WAIT - WAIT - Processor - Processor - ADDR - DATA - DATA - Microcontrollers - IN - From address bus - read signal - OUT - IN - From environment - IN - From environment

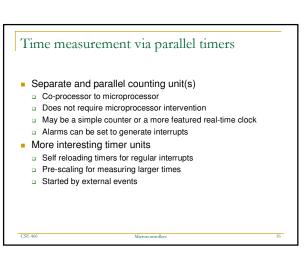

### Time and instruction execution Keep track of detailed timing of each instruction's execution Highly dependent on code Hard to use compilers Not enough control over code generation Interactions with caches/instruction-buffers Loops to implement delays Keep track of time in counters Keeps processor busy counting and not doing other useful things Timer Take differences between measurements at different points in code Keeps running even if processor is idle to save power An independent "co-processor" to main processor

# Input/output events Input capture Record time when input event occured Can be used in later handling of event Output compare Set output event to happen at a point in the future Reactive outputs e.g., set output to happen a pre-defined time after some input Processor can go on to do other things in the meantime

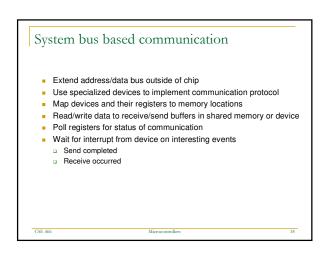

### Support for communication protocols

- Built-in device drivers

- For common communication protocols

- e.g., RS232, IrDA, USB, Bluetooth, etc.

- Serial-line protocols most common as they require fewer pins

- Serial-line controller

- Special registers in memory space for interaction

- May use timer unit(s) to generate timing events

- For spacing of bits on signal wire

- For sampling rate

- Increase level of integration

- No external devices

- May further eliminate need for shared memory or system bus

CCE 466

Microcontrollers

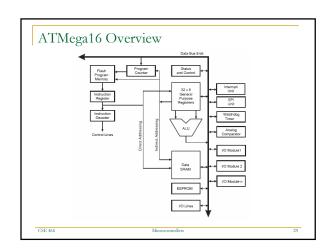

### Microcontrollers

- Embedded processor with much more integrated on same chip

- □ Processor core + co-processors + memory

- ROM for program memory, RAM for data memory, special registers to interface to outside world

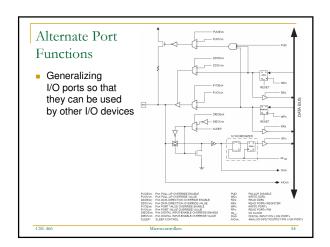

- Parallel I/O ports to sense and control wires

- □ Timer units to measure time in various ways

- Communication subsystems to permit direct links to other devices

Microcontrollers

### Microcontrollers (cont'd)

- Other features not usually found in general-purpose CPUs

- Expanded interrupt handling capabilities

- Multiple interrupts with priority and selective enable/disable

- Automatic saving of context before handling interrupt

- Interrupt vectoring to quickly jump to handlers

- More instructions for bit manipulations

- Support operations on bits (signal wires) rather than just words

- Integrated memory and support functions for cheaper system cost

- Built-in EEPROM, Flash, and/or RAM

- DRAM controller to handle refresh

- Page-mode support for faster block transfers

CSE 466

Microcontroller

### Block diagram of processor (Harvard) Register transfer view of Harvard architecture Separate busses for instruction memory and data memory Separate busses for instruction memory and data memory Data Memory Load Life path Life

### Block diagram of processor (Princeton) Register transfer view of Princeton architecture Single unified bus for instructions, data, and I/O REG. AC. John Data Memory II-6 but words bata Memory II-6 but words

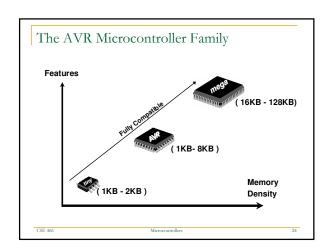

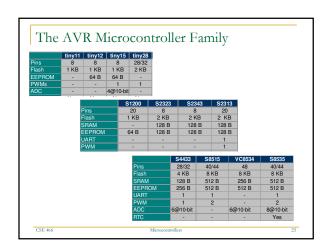

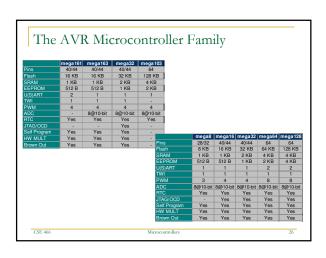

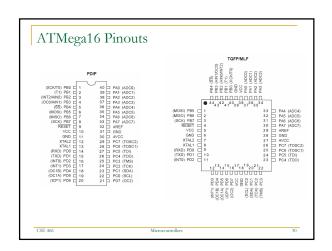

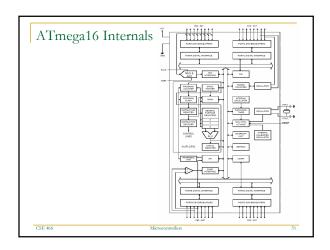

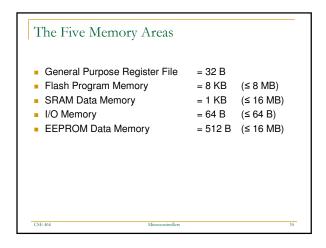

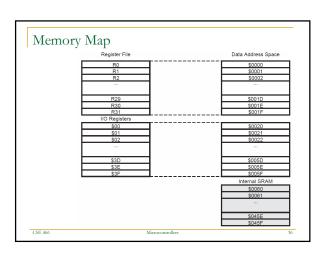

Microcontroller we will be using

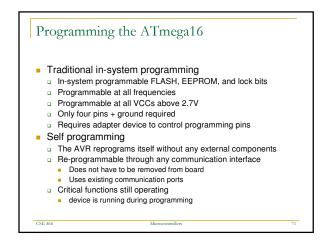

• Atmel AVR Microcontroller (ATmega16) – 16 MIPS at 16 MHz

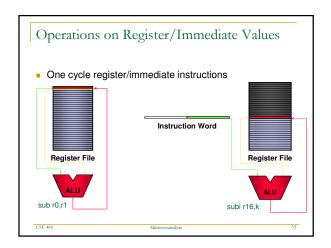

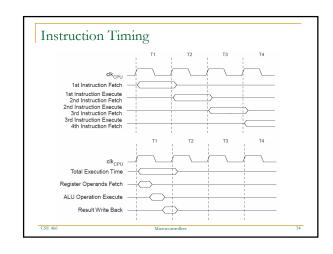

• 8-bit microcontroller (8-bit data, 16-bit instructions) – RISC Architecture

• 131 instructions (mostly single-cycle – on-chip 2-cycle multiplier)

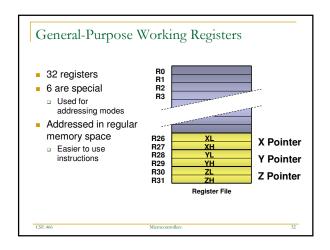

• 32 general-propose registers

• Internal and external interrupts

Memory

• instruction (16KB Flash memory – read-while-write)

• book ROM (5/2 Byte EEPROM)

• book ROM (5/2 Byte EEPROM)

• Timers (countiers)

• 2 8-bit and 1 1-bit timericounters with compare modes and prescalers

• Real-line clock (32.768 kHz) with separate oscillator

• Programmable vatchodg timer

• Serial communication interfaces

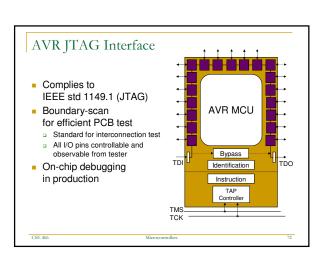

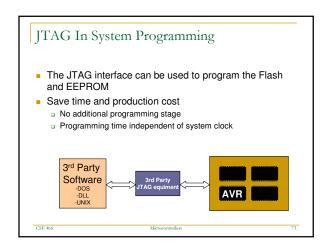

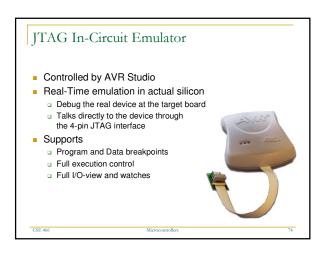

• JTAG boundary-scan interface for programming/debugging

• Programmable USART (universal synchronous/asynchronous receiver transmitter)

• Two-wire serial interface (are municated firen tronomunication protocols)

• SPI serial port (serial peripheral interface)

• Pertipheral feature.

• Four charmets with support for grube-width modulation

• Four charmets with support for grube-width modulation

• Up to 32 general-purpose (IC) prise (with interrupt support)

• Six power saving modes

Why did we pick the ATmega16

Modern microcontroller

Easy to use C compiler

Better performance/power than competitors

Microchip PIC

Motorola 88HC11

Intel 80C51

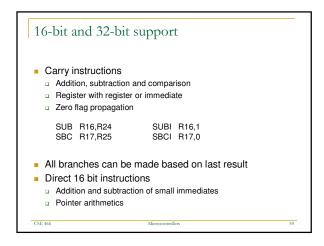

Excellent support for 16-bit arithmetic operations

A lot of registers that eliminate moves to and from SRAM

Single cycle execution of most instructions

Used in the UC Berkeley sensor mote (2<sup>nd</sup> half of qtr)

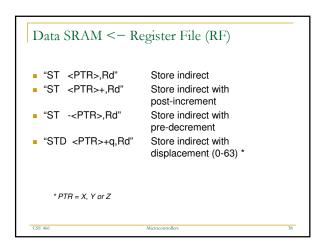

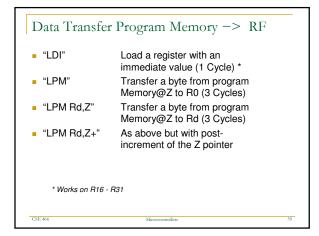

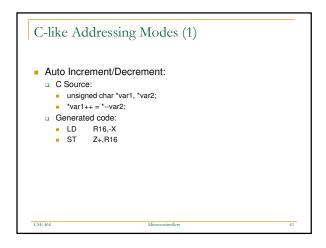

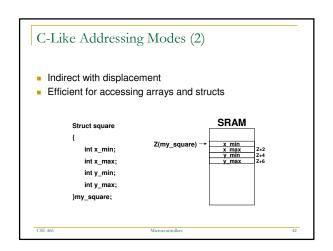

# Data SRAM -> Register File (RF) "LD Rd,<PTR>" Load indirect "LD Rd,<PTR>+" Load indirect with post-increment "LD Rd,-<PTR>" Load indirect with pre-decrement "LDD Rd,<PTR>+q" Load indirect with pre-decrement "LDD Rd,<PTR>+q" Load indirect with displacement (0-63)\*

```

A Small C Function

/* Return the maximum value of a table of 16 integers */

int max(int *array)

{

char a;

int maximum=-32768;

for (a=0;a<16;a++)

if (array[a]>maximum)

maximum=array[a];

return (maximum);

}

GSE 466 Microcontrollers 45

```

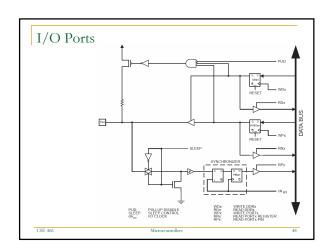

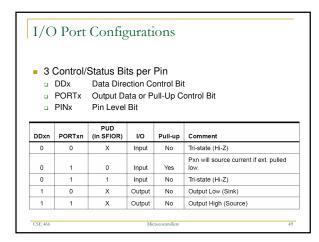

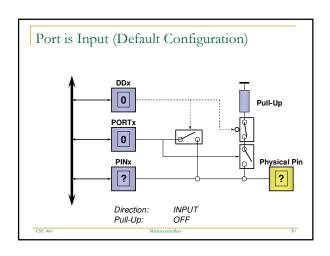

```

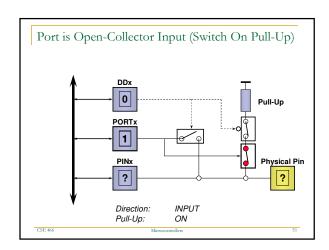

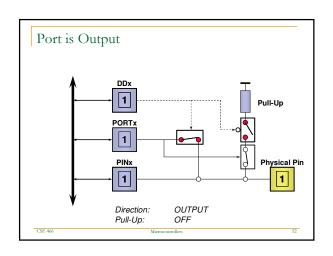

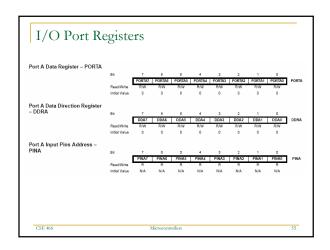

I/O Ports General Features

Push-pull drivers

High current drive (sinks up to 40 mA)

Pin-wise controlled pull-up resistors

Pin-wise controlled data direction

Fully synchronized inputs

Three control/status bits per bit/pin

```

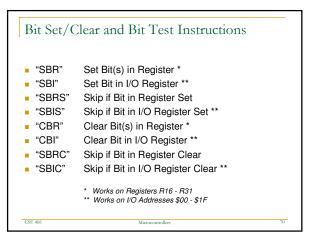

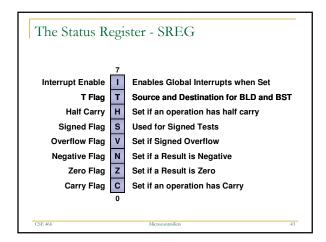

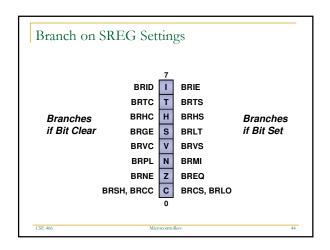

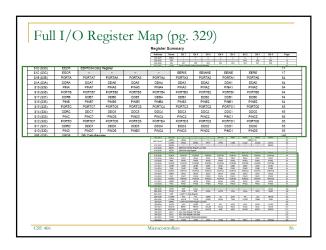

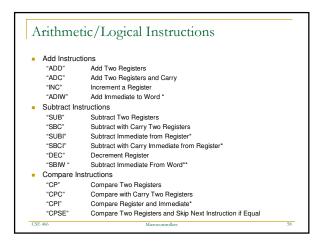

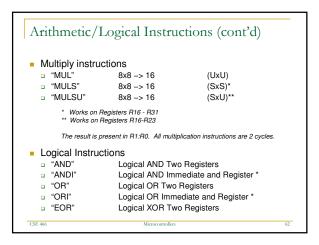

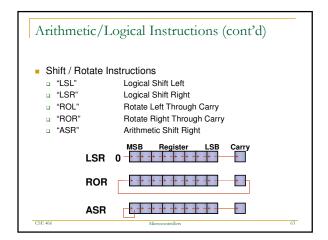

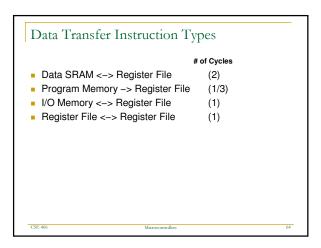

### Instruction Classes (pg. 331) Arithmetic/Logic Instructions Data Transfer Instructions Program Control Instructions Bit Set/Test Instructions

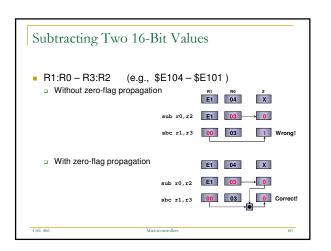

### Comparing Two 32-Bit Values Example: Compare R3:R2:R1:R0 and R7:R6:R5:R4 cp r0,r4 cpc r1,r5 cpc r2,r6 cpc r3,r7 After last instruction, status register indicates equal, higher, lower, greater (signed), or less than (signed)

# Data Transfer RF <-> SRAM Stack "PUSH" PUSH a register on the stack Decrements stack pointer by 1 Decremented by 2 when a return address is pushed on the stack "POP" POP a register from the stack Increments stack pointer by 1 Incremented by 2 when a return address is popped off on return Stack grows from higher to lower memory locations

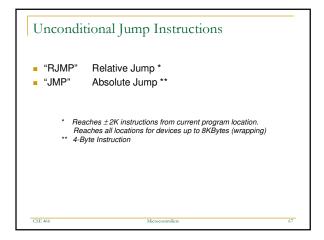

# Subroutine Call and Return "RCALL" Relative Subroutine Call \* "CALL" Absolute Subroutine Call \*\* "RET" Return from Subroutine "RETI" Return from Interrupt Routine "Reaches ±2K instructions from current program location. Reaches all locations for devices up to 8KBytes (wrapping) "4-Byte Instruction