### 4/18

## Admin

- Test script will be provided over the weekend.

- Sign up for demo slots on the 'signup' link on the calendar.

## Consistency vs Coherence

- Coherence is micro-scale

- Defines the behavior of a single data value.

- All actors should have the same view of state.

- Consistency is macro-scale

- Defines visible concurrency between data.

- Contract for how shared resources behave.

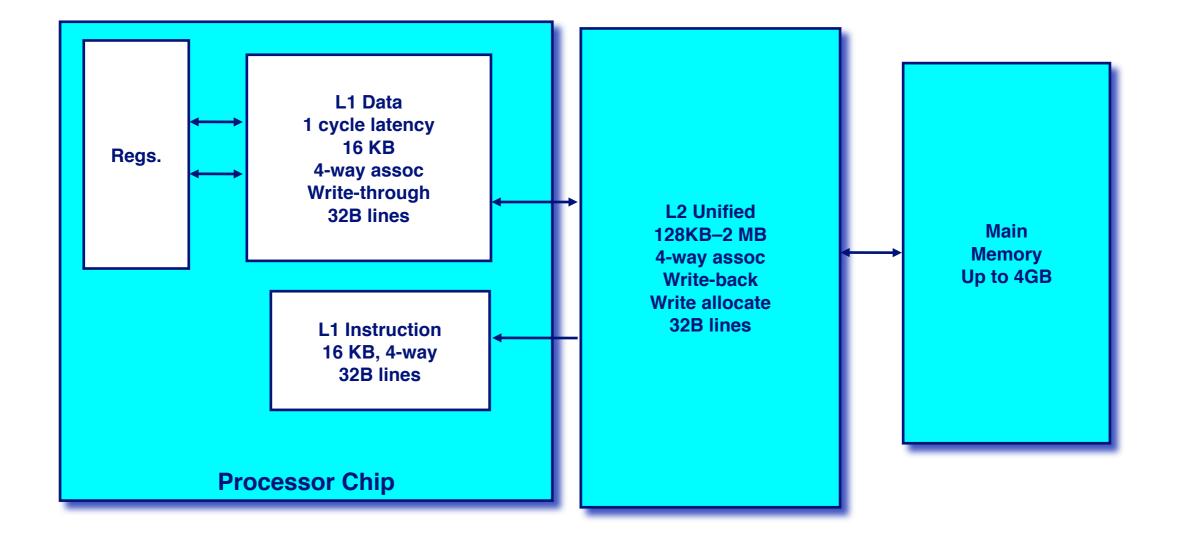

### x86 Cache

#### Coherence Strategies (For write-back caches)

- Invalidation / Directory

- Snooping

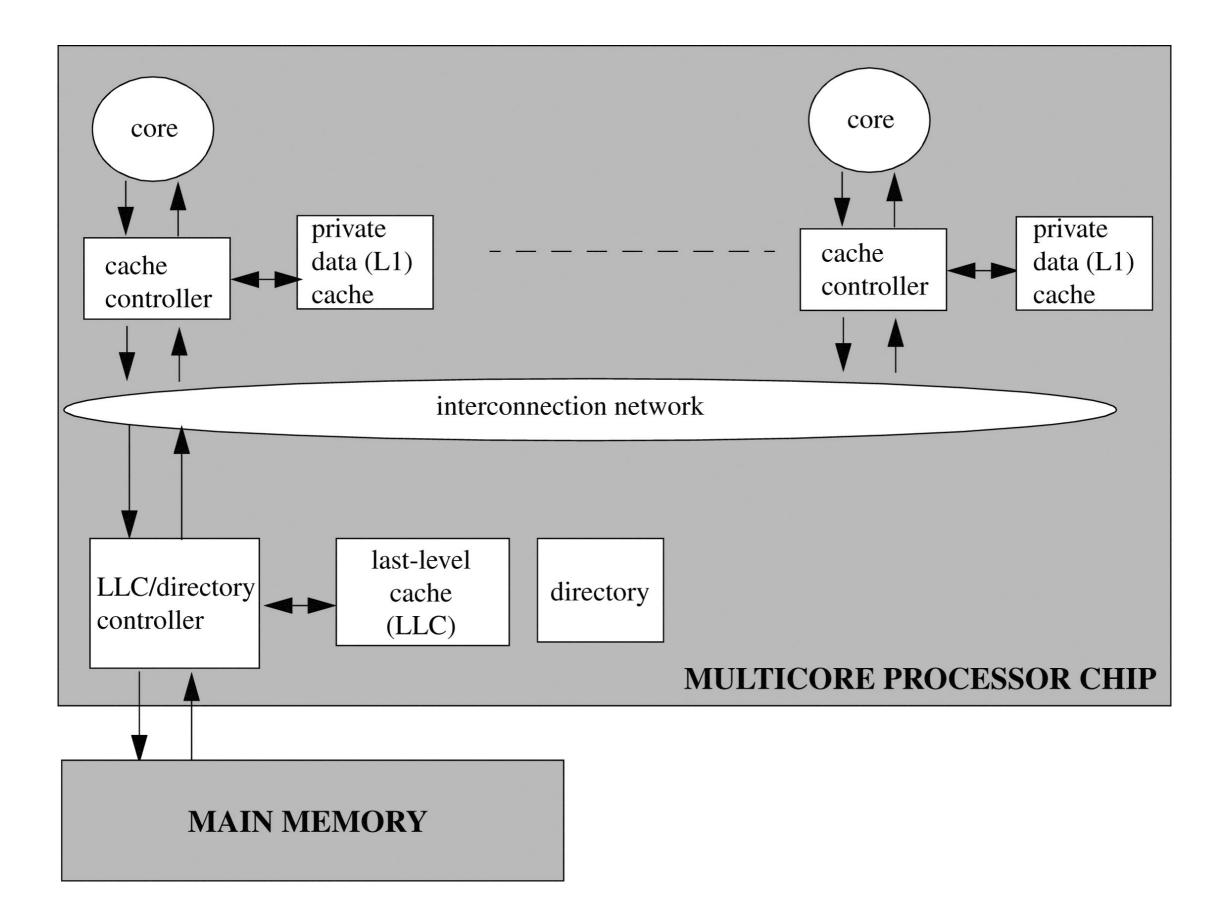

# Directory Coherence

- Centralized manager for cache states.

- Manager/Directory sends invalidations on behalf of client.

- SGI Origin (mid 90s) had a directory with 1024 cores, Intel i7's use 'Home Snoop', a directory protocol.

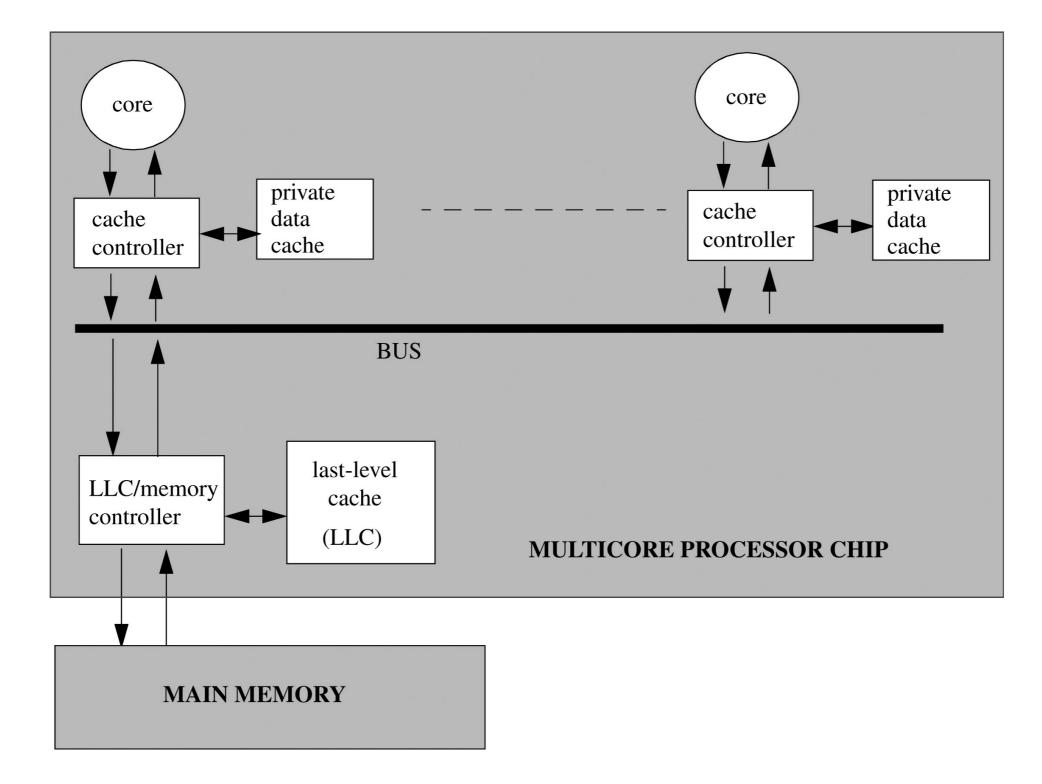

# Snooping Coherence

- When one cache is the 'owner' in a writeback scenario, other caches can read by snooping from the owner.

- Also allows with minimal effort an 'exclusive-read' state, where data is not invalidated, but

- Implemented with a hardware bus by Sun Starfire (1991), IBM POWER5 (2005)

| Cycle | Core I           | Core 2          | Memory      | Request Bus | Data Bus      |

|-------|------------------|-----------------|-------------|-------------|---------------|

|       | Load Miss, req S |                 |             |             |               |

| 2     |                  |                 |             | CI req S    |               |

| 3     |                  | Store Miss      | CI response |             |               |

| 4     |                  |                 |             |             | data from mem |

| 5     | Perform Load     | req M           |             |             |               |

| 6     |                  |                 |             | C2 req M    |               |

| 7     |                  |                 | C2 response |             |               |

| 8     |                  |                 |             |             | data from mem |

| 9     |                  | Perform store   |             |             |               |

| 10    | Load miss, req S |                 |             |             |               |

|       |                  |                 |             | CI req S    |               |

| 12    |                  | CI&mem response |             |             |               |

| 13    |                  |                 |             |             | data from C2  |

| 14    | Perform load     |                 | store data  |             |               |

|       |                  |                 |             |             |               |

## Dangers

- Violate single-writer-multiple-reader

- Deadlock

## Consistency

- Eventual Consistency

- Total Store Order

- Sequential Consistency

- Linearizable

#### Consistency Sequential: (r1,r2)=(0,1)x = 0, y = 0 or (1,0) or(1,1)

| Core I | Core 2 |  |

|--------|--------|--|

| x =    | y =    |  |

| rl = y | r2 = x |  |

TSO: (rI,r2)=(0,0) or (1,0) or (0,1) or (1,1)