1118123 Alternative Spring Break

Today: which page to evict? Mechanism of Page Eviction

- - -> allocate space in swap, write evicted page to swap -> track page => swap loc

- -> zero out old content before mapping it to a new page

multiple pages => frame tracked by frame metadata xk: core map entry

Question in class: why write page to swap instead of using disk directly (map page to swap)

- -> architecture:

- code and data needs to be in memory to be accessed by the CPU disk is block addressable, much much slower in access latency

There's a non traditional persistent device: non volatile memory (byte addressable, slower access than DRAM, but can be accessed as memory directly), offers an interesting design space

## Eviction Policies: What page/frame to evict? -> FIFO -> pick the page that's brought in first (longest time in memory) -> a queue of frames in order of allocation -> doesn't care about access patterns Page accessed in this order: A, B, C, D, A, B, E, A, B, C, D, E FIFO 3 frames Belady's Anomaly More (9 PFS) frames may cause FIFU 4 frames more page Frame 1 A A A A A A E E Frame 2 - B B B B B A faults with FIFO

policy

Frame 4

- -> Least Recently Used

- -> evict page that's least recently used

- -> good when access exhibits locality

- -> worst case: N frames N+1 pages accessed in order

- -> How to implement this?

- -> SW: queue, when a page is used, bring it to the back, head of queue is the LRU page

- -> HW: implement HW queue, or add timestamp update to PTE

needs to be done on every access (TLB miss& TLB hits)

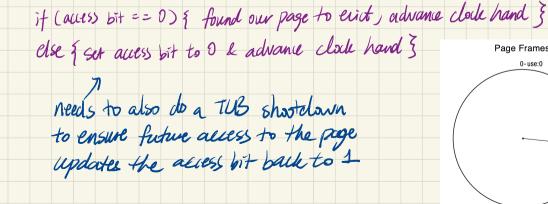

- -> Clock Algorithm

- -> approximates LRU

- -> uses access bit (PTE) to estimate if the page is used recently

- -> algorithm starts at clock hand (stateful, advances each time the algo runs)

· · · 8-use:0 7-use:1

pattern noto autuat, but doesn't core

about whether

A takes access

the page has been wisten to

> set upon TLB miss Chaneto