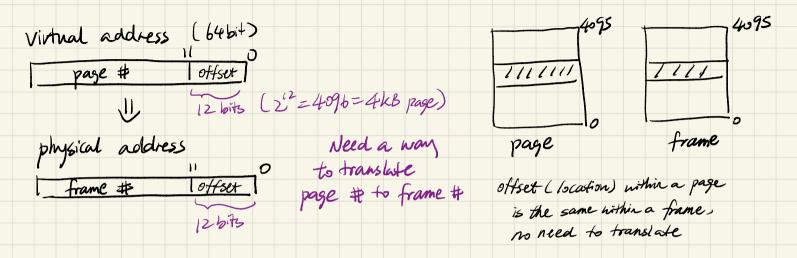

1112 Paging Physical Memory Allocation -> multiple processes need to share the physical memory -> last class : base & bound > virtual memory for each process (own view, independent from where it is in physical memory) -> address translation is simple: if (vaddr< bound ) ? vaddr+ bound; } Limitations -> memory fragmentation (variably sized processes) A -> inefficient use of physical memory ( processes don't need all memory at once) B -> hard to implement menony sharing A pagine : divide vitual memory into pages, physical memory as frames, and map a page to a frame C physical 112211 thang Turner Shang man memory 111m VAS13 VAS A PM

Address Translation For Paging

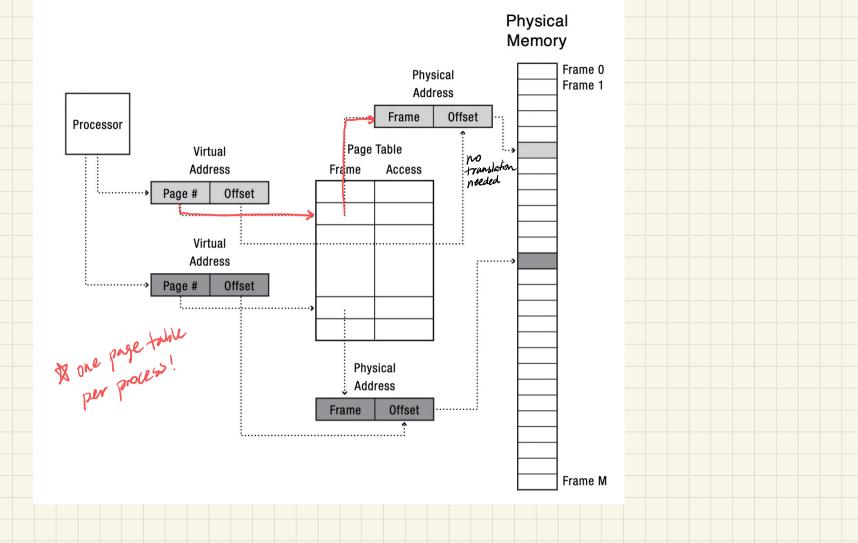

What data structure can be use as the translation (look up) table? > simple approach : a single array with an entry for each page

| page # page # | How many entries do we need ? |

|---------------|-------------------------------|

| frame fram    |                               |

|               | 252 / 264/212) entries!       |

| page table    | 2 (2/2/2/                     |

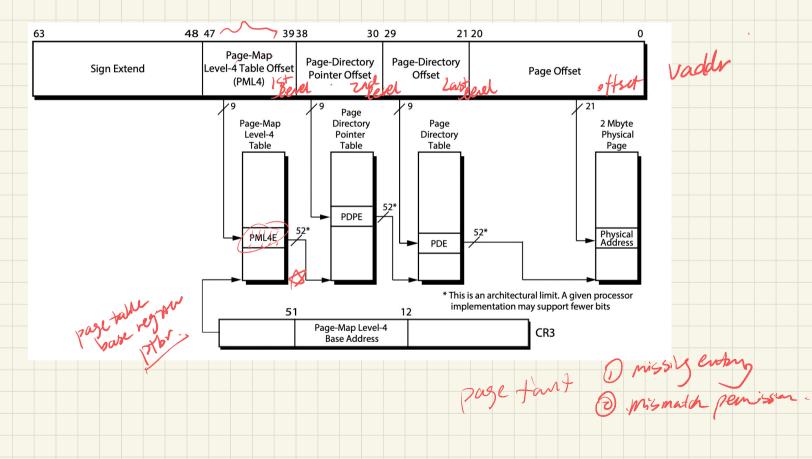

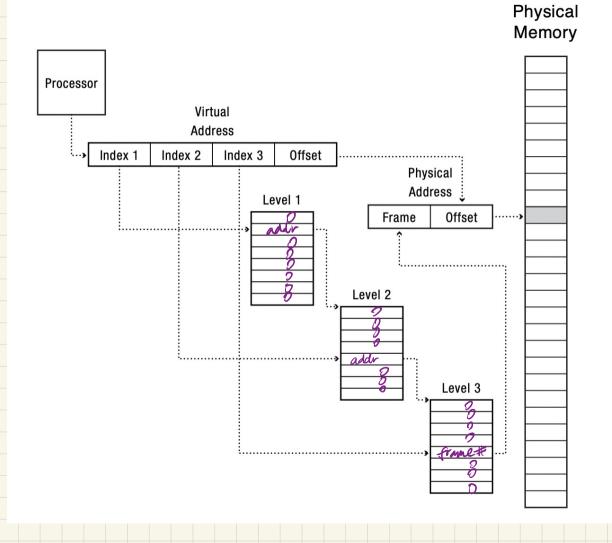

A single page table is too large in size, especially since most programs don't use that much memory? To save space, we can introduce layer Multilevel page table page # loffset | vaddr idx1 idx2 idx3 offset same vadder, ne just group bits differently > la of 2<sup>rd</sup> four lac of 3<sup>rd</sup> lovel ⇒ 111111 3rd/last lovel 2nd level page table top level page table pagetable allocate the page tables as we go . if ne only access ? page, we only need I top level, PM I and level and I last level page table ( each is much smaller than a PT u/ 2 entries)

Is muttilevel page table always smaller than single level? -> What if ne use all of the install memory? -> need to allocate the first level page table, all of 2nd level page table, and all of 3nd blevel page table. ( last level page tables store the actual page > frame translation, a total of 2<sup>52</sup> entries ) E 1st level page table 3 E 3rd bevel PM and level

Now we mostly solved the space problem, next is the cost of page table look up. O Lache : Translation Lookaside Butter (TLB) -> caches the result of translation Physical Memory Virtual Address Page# Offset Translation Lookaside Buffer (TLB) Virtual Page Page Frame Access Physical »(=) Address Matching Entry Frame Offset entr. ...) .....,₽age Table Lookun

(2) Make hardware walk the page table for you -> hw needs to understand the page table format.