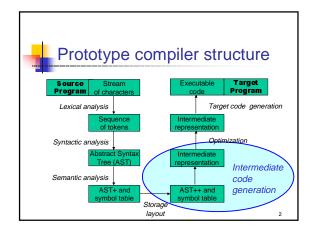

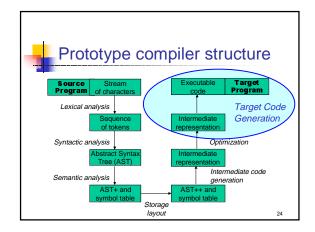

# Intermediate code generation

- Purpose: translate ASTs into linear sequence of simple statements called intermediate code

- Can optimize intermediate code in place

- A later pass translates intermediate code into target code

- Intermediate code is machine-independent

- Don't worry about details of the target machine (e.g., number of registers, kinds of instruction formats)

- Intermediate code generator and optimizer are portable across target machines

- Intermediate code is simple and explicit

- Decomposes code generation problem into simpler pieces

- Constructs implicit in the AST become explicit in the

3

## PL/0

Our PL/0 compiler merges intermediate and target code generation for simplicity of coding

4

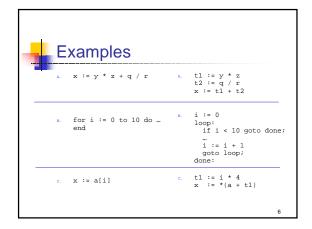

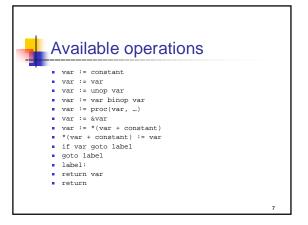

## Three-address code:

a simple intermediate language

- Each statement has at most one operation in its right-hand side

- Introduce extra temporary variables if needed

- Control structures are broken down into (conditional) branch statements

- Pointer and address calculations are made explicit

5

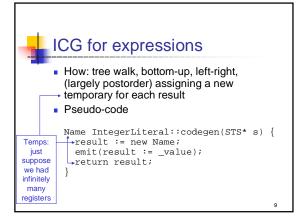

# ICG (Intermediate code generation) from ASTs

- Once again (like type checking), we'll do a tree traversal

- Cases

- expressions

- assignment statements

- control statements

- declarations are already done

8

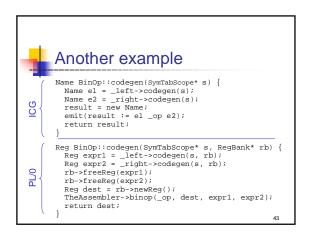

# Another pseudo-example

```

Name BinOp::codegen(SymTabScope* s) {

Name e1 = _left->codegen(s);

Name e2 = _right->codegen(s);

result = new Name;

emit(result := e1 _op e2);

return result;

}

```

...

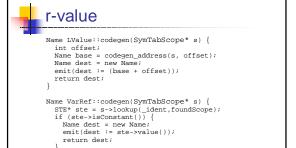

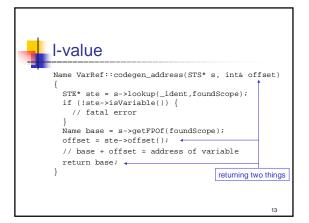

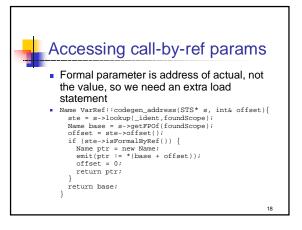

# ICG for variable references

- Two cases

- if we want I-value, compute address

- if we want r-value, load value at that address

11

return Lvalue::codegen(s);

12

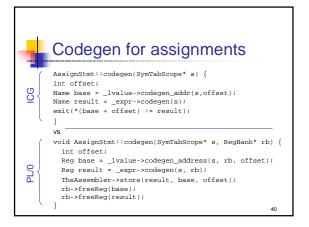

LCG for assignments

AssignStmt::codegen(SymTabScope\* s) {

int offset;

Name base = \_lvalue->codegen\_addr(s,offset);

Name result = \_expr->codegen(s);

emit(\*(base + offset) := result);

}

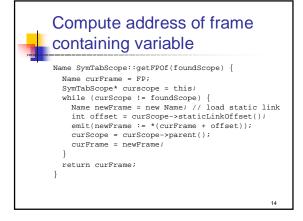

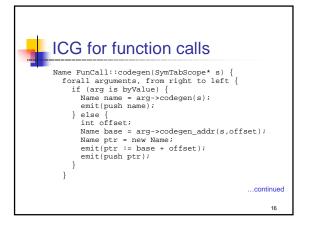

ICG for function calls, con't

s->lookup(\_ident,foundScope);

Name link = s->getFPOf(foundScope);

emit(push link); // callee's static link

emit(call \_ident)

Name result = new Name;

emit(result := RETO);

return result;

}

```

ICG for array accesses

• AST:

array_expr[index_expr]

• Code generated:

a_base := <addr of array_expr>

i := <value of index_expr>

elem_offset := i * <size of element type>

elem_addr := a_base + elem_offset

• 2D Arrays? Not really:

var MyArray array[10] of array[5] of int;

| MyArray [i] [j];

MyArray [i]

```

```

void IfStmt::codegen(SymTabScope* s) {

Name t = _test->codegen(s);

Label else_lab = new Label;

emit(if t = 0 goto else_lab);

_then_stmts->codegen(s);

Label done_lab = new Label;

emit(goto done_lab);

emit(else_lab:);

_else_stmts->codegen(s);

emit(done_lab);

}

```

ICG for while statement

# **Target Code Generation**

- Input: intermediate representations (IR)

- Ex: three-address code

- Output: target language program

- Absolute binary code

- Relocatable binary code

- Assembly code

- C

05

# Task of code generator

- Bridge the gap between intermediate code and target code

- Intermediate code: machine independent

- Target code: machine dependent

- Two jobs

- Instruction selection: for each IR instruction (or sequence), select target language instruction (or sequence)

- Register allocation: for each IR variable, select target language register/stack location

26

#### Instruction selection

- Given one or more IR instructions, pick the "best" sequence of target machine instructions with the same semantics

- "best" = fastest, shortest

- Correctness is a big issue, especially if the code generator (codegen) is complex

27

# Difficulty depends on instruction set

- RISC: easy

- Usually only one way to do something

- Closely resembles IR instructions

- CISC: hard

- Lots of alternative instructions with similar semantics

- Lots of tradeoffs among speed, size

- Simple RISC-like translation may be inefficient

- C: easy, as long as C is appropriate for desired semantics

- Can leave optimizations to the C compiler

..

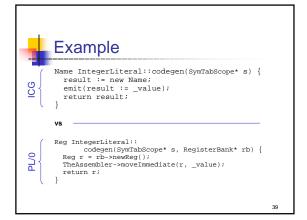

#### Example

- IR code

- t3 := t1 + t2

- Target code for MIPS

- add \$3,\$1,\$2

- Target code for SPARC

- add %1,%2,%3

- Target code for 68k

- mov.l d1,d3 add.l d2,d3

Note that a single IR instruction may expand to several target instructions

20

#### Example

- IR code

- t1 := t1 + 1

- Target code for MIPS

- add \$1,\$1,1

- Target code for SPARC

- add %1,1,%1

- Target code for 68k

- add.l #1,d1 **Or**inc.l d1

- Can have choices

- This is a pain, since choices imply you must make decisions

30

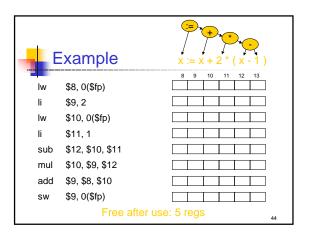

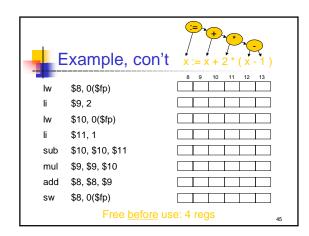

## Example

- IR code (push x onto stack)

sp := sp 4

\*sp := t1

- Target code for MIPS

- sub \$sp,\$sp,4

sw \$1,0(\$sp)

- Target code for SPARC

- sub %sp,4,%sp st %1,[%sp+0]

- Target code for 68k

- mov.l d1,-(sp)

- Note that several IR instructions may combine to a single target instruction

- This is hard!

24

#### Instruction selection in PL/0

- Very simple instruction selection

- As part of generating code for an AST node

- Merged with intermediate code generation, because it's so simple

- Interface to target machine: assembler class

- Function for each kind of target instruction

- Hides details of assembly format, etc.

- Two assembler classes (MIPS and x86), but you only need to extend MIPS

32

#### Resource constraints

- Intermediate language uses unlimited temporary variables

- This makes intermediate code generation easy

- Target machine, however, has fixed resources for representing "locals"

- MIPS, SPARC: 31 registers minus SP, FP, RetAddr, Arg1-4, ...

- 68k: 16 registers, divided into data and address registers

- x86: 4(?) general-purpose registers, plus several special-purpose registers

33

## Register allocation

- Using registers is

- Necessary: in load/store RISC machines

- Desirable: since much faster than memory

- So...

- Should try to keep values in registers if possible

- Must reuse registers for many temp variables, so we must free registers when no longer needed

- Must be able to handle out-of-registers condition, so we must spill some variables to stack locations

- Interacts with instructions selection, which is a pain, especially on CISCs

34

## Classes of registers

- What registers can the allocator use?

- Fixed/dedicated registers

- SP, FP, return address, ...

- Claimed by machine architecture, calling convention, or internal convention for special purpose

- Not easily available for storing locals

- Scratch registers

- A couple of registers are kept around for temp values

- E.g., loading a spilled value from memory to operate upon it

- Allocatable registers

- Remaining registers are free for the allocator to allocate (PL/0 on MIPS: \$8-\$25)

#### Which variables go in registers?

- Temporary variables: easy to allocate

- Defined and used exactly once, during expression eval

So the allocator can free the register after use easily

- Usually not too many in use at one time

So less likely to run out of registers

- Local variables: hard, but doable

- Need to determine last use of variable to free register

- Can easily run out of registers, so need to make decisions

- What about load/store to a local through a pointer?What about the debugger?

- Global variables?

- Really hard, but doable as a research project?

36

P

## PL/0's simple allocator design

- Keep set of allocated registers as codegen proceeds

- RegisterBank class

- During codegen, allocate one from the set

- Reg reg = rb->getNew();

- Side-effects register bank to note that reg is taken

- What if no registers are available?

- When done with a register, release it

- Rb->free(reg);

- Side-effects register bank to note that reg is free

#### Connection to ICG

- In the last lecture, the pseudo-code often create a new Name

- Since PL/0 merges intermediate code generation (ICG) with target generation, these new Names are equivalent to allocating registers in PL/0

## Codegen for if statements

```

void IfStmt::codegen(SymTabScope* s,RegBank* rb){

Reg test = _test->codegen(s, rb);

char* elseLabel = TheAssembler->newLabel();

TheAssembler->branchFalse(test, elseLabel);

rb->freeReg(test);

PL%

for (int i=0; i < _then_stmts->length(); i++) {

_then_stmts->fetch(i)->codegen(s, rb);

TheAssembler->insertLabel(elseLabel);

```

PL/0

## Codegen for call statements

```

void CallStmt::codegen(SymTabScope* s, RegBank* rb) {

for (int i = _args->length() - 1; i >= 0; i--) {

Reg areg = _args->fetch(i)->codegen(s, rb);

TheAssembler->push(areg);rb->freeReg(areg);

SymTabScope* enclScope;

SymTabEntry* ste = s->lookup(_ident, enclScope);

TheAssembler->push(staticLink);

rb->freeReg(staticLink);

rb->saveRegs(s);

TheAssembler->call(_ident);

rb->restoreRegs(s);

```