# CSE 378 Fall 2010 Machine Organization & Assembly Language

**Final Exam Solution**

Write your answers on these pages. Additional pages may be attached (with staple) if necessary. Please ensure that your answers are legible. Please show your work. Write your name at the top of each page.

#### **Total points: 100**

## 1. [15 Points] x86 Programming

Write the 64-bit x86 code for the following function, following all standard x64 calling conventions:

```

int my_func(unsigned char *input_array) {

int output = 0;

while (*input_array) {

if (*input_array < 127)

output += *input_array;

++input_array;

}

return output;

}</pre>

```

```

my func:

pushq %rbp

movq %rsp, %rbp

xor %eax, %eax

loop:

cmpb (%rdi), $0

je

exit_loop

cmpb (%rdi), $127

jge increment

xor %ecx, %ecx

movb (%rdi), %ecx

add %ecx, %eax

increment:

inc %rdi

jmp loop

exit_loop:

leave

ret

```

## 2. [15 Points] MIPS Programming

Write the MIPS code for the following function, following all standard MIPS32 calling conventions:

```

int fib(int x) {

if (x <= 1)

return 1;

return fib(x-1) + fib(x-2);

}</pre>

```

```

fib:

addiu $sp, $sp, -12

sw $ra, 8($sp)

addi $v0, $0, 1

sub $a0, $a0, $v0

blez $a0, base_case

sw $a0, 4($sp)

jal fib

sw $v0, 0($sp)

lw $a0, 4($sp)

addi $a0, $a0, -1

jal fib

lw $t0, 0($sp)

add $v0, $v0, $t0

base_case:

lw $ra, 8($sp)

addiu $sp, $sp, 12

jr $ra

```

## 3. [15 points] Datapath

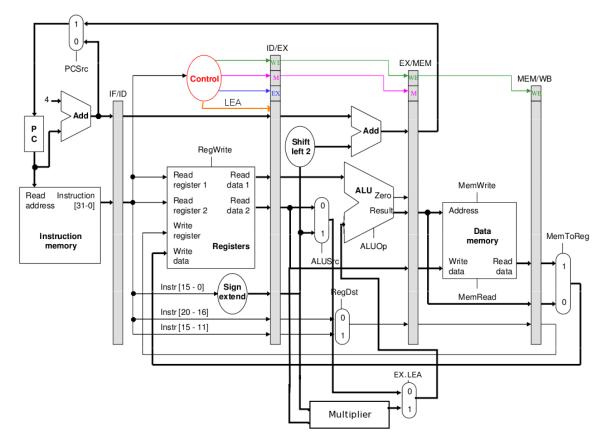

As you may recall, in x86 the load effective address instruction computes and stores an effective memory address in a register. For example, "leal (\$eax, \$edx, 4), \$eax" assigns the value of \$eax + \$edx \* 4to the eax register. Suppose we want to add a similar instruction to the 5-stage pipelined MIPS processor you implemented in lab. The syntax of this new I-format instruction is lea rs, rt, scale and it stores the value of R[rt] \* scale + R[rs] into R[rt].

(a) The diagram below is a simple version of the 5-stage pipelined MIPS processor from class. The controller has a new output wire named LEA, which is high when the controller decodes an lea instruction and low otherwise. Add the necessary logic to support this new instruction to the datapath below.

Answer:

(b) Complete the following table of control signals for the newly-supported lea instruction, specifying the value of each signal as 0, 1, or X (don't care). Add columns for any control signals your added logic requires. Writing a 0 or 1 when an X is more accurate is not correct.

| Opcode | LEA | RegWrite | RegDst | ALUSrc | ALUOp | MemWrite | MemRead | MemToReg | PCSrc |

|--------|-----|----------|--------|--------|-------|----------|---------|----------|-------|

| lea    | 1   |          |        |        |       |          |         |          |       |

|        |     |          |        |        |       |          |         |          |       |

| Opcode | LEA | RegWrite | RegDst | ALUSrc | ALUOp | MemWrite | MemRead | MemToReg | PCSrc |

|--------|-----|----------|--------|--------|-------|----------|---------|----------|-------|

| lea    | 1   | 1        | 0      | Х      | add   | 0        | 0       | 0        | 0     |

## 4. [15 points] Pipelining

Imagine a pipelined processor with the following pipe stages: Fetch1  $\rightarrow$  Fetch2  $\rightarrow$  Decode/Reg  $\rightarrow$  Execute  $\rightarrow$  Memory1  $\rightarrow$  Memory2  $\rightarrow$  Writeback

That is, accessing memory (for both instructions and data) requires two pipeline stages. Because of the increased delay in fetching instructions, this machine has **2 branch delay slots**. Further, there is no partial result forwarding (e.g., there exist no forwarding paths from Mem1  $\rightarrow$  EX).

Fill in the following pipeline stage diagram for this processor when it executes the following code:

#### LOOP:

```

LW $4, 0($5)

BEQ $4, $4, LOOP

ADDI $5, $5, 8

SUBI $5, $5, -4

```

#### Answer:

| Cycle | Fetch1 | Fetch2 | Decode/Reg | Ex   | Mem1 | Mem2 | WB   |

|-------|--------|--------|------------|------|------|------|------|

| 0     | LW     |        |            |      |      |      |      |

| 1     | BEQ    | LW     |            |      |      |      |      |

| 2     | ADDI   | BEQ    | LW         |      |      |      |      |

| 3     | SUBI   | ADDI   | BEQ        | LW   |      |      |      |

| 4     | SUBI   | ADDI   | BEQ        | NOP  | LW   |      |      |

| 5     | SUBI   | ADDI   | BEQ        | NOP  | NOP  | LW   |      |

| 6     | SUBI   | ADDI   | BEQ        | NOP  | NOP  | NOP  | LW   |

| 7     | LW     | SUBI   | ADDI       | BEQ  | NOP  | NOP  | NOP  |

| 8     | BEQ    | LW     | SUBI       | ADDI | BEQ  | NOP  | NOP  |

| 9     | ADDI   | BEQ    | LW         | SUBI | ADDI | BEQ  | NOP  |

| 10    | SUBI   | ADDI   | BEQ        | LW   | SUBI | ADDI | BEQ  |

| 11    | SUBI   | ADDI   | BEQ        | NOP  | LW   | SUBI | ADDI |

| 12    | SUBI   | ADDI   | BEQ        | NOP  | NOP  | LW   | SUBI |

4

## 5. [15 Points] Caching

Suppose your processor has a data cache of the following geometry:

- Total data size of 128 B

- Cache block size of 16 B

- 2-way set associativity with LRU replacement

- Writeback coherence policy

- Allocate-on-write for store misses

Hit returns in 1 cycle Miss penalty 4 cycles

Assuming a miss penalty of 4 cycles and that a cache hit returns in 1 cycle, what would be the hit rate, miss rate, number of writebacks, and average memory access time (in cycles) for the following address stream?

- L 0x0000001 S 0x0000002 L 0x0000010

- L 0x0000011

- L 0x0000001

- L 0x0000200

- L 0x00000300

- L 0x00000400

- S 0x00000201

- L 0x00000401

- L 0x00000301

| Hit Rate     | 4/11  |

|--------------|-------|

| Miss Rate    | 7/11  |

| # Writebacks | 2     |

| AMAT         | 32/11 |

## 6. [10 Points] Caching in the Real World

Imagine you're building an iPhone application for processing images. As part of your application you need to extend the standard math functions described in math.h to compute the average value of a matrix of normalized pixel values. As a smart programmer, you wish to avoid "reinventing the wheel" so you query Google for implementations. Your search returns two promising results, both conveniently implemented as functions in the C programming language.

Result A:

```

double average_matrix_by_row(double* data[], int numRows, int numCols) {

double sum = 0.0;

int r, c;

for(r = 0; r < numRows; r++) {

for(c = 0; c < numCols; c++) {

sum += data[r][c];

}

}

return sum / ((double) numRows * numCols);

}</pre>

```

#### Result B:

```

double average_matrix_by_col(double* data[], int numRows, int numCols) {

double sum = 0.0;

int c, r;

for(c = 0; c < numCols; c++) {

for(r = 0; r < numRows; r++) {

sum += data[r][c];

}

}

return sum / ((double) numRows * numCols);

}</pre>

```

Considering that the iPhone 4's A4 processor has a 32 KB, 4-way set associative cache with 16-word (64 B) blocks, which implementation would you choose for your program? You may assume that all local variables (e.g. sum, r, c) are kept in registers in the compiled version of the code. Justify your choice with quantitative reasons.

**Answer**: Result A takes much better advantage of spatial locality than Result B. Result A leverages the row major representation of two-dimensional arrays and in doing so enjoys a low miss rate on the order of 1 miss per every 8 accesses for a total miss rate of (r \* c) / 8 whereas Result B misses on each access for matricies with 9 or more columns for a worst-case miss rate of 1 and a best-case miss rate no lower than 75%.

6

### 7. [15 Points] True / False

Circle True or False for each of the following questions.

- (a) True / False : Paging is the only way to provide protection between processes on x86 processors

- (b) True / False : In x64 all arguments to functions are passed via the stack

- (c) True / False : MIPS is an accumulator based architecture

- (d) True / False : Programs always run faster on systems that have caches

- (e) True / False : Adding a pipeline stage to a processor can decrease performance

- (f) True / False : Memory mapped I/O devices can use memory that is cached by the main processor

- (g) **True / False** : When the x86 processor receives an external interrupt while in user mode, the processor vectors to the given user mode interrupt handler

- (h) True / False : I enjoyed this class

#### Answer:

- (a) (2 pts) False

- (b) (2 pts) False

- (c) (2 pts) False

- (d) (2 pts) False

- (e) (2 pts) True

- (f) (2 pts) True

- (g) (2 pts) False

- (h) (1 pt) True or False

## 8. [1 Point] Extra Credit

Steven (the TA) shares his initials with the opcode for what MIPS32 instruction?

Answer: Shift Right Logical (srl)

This page intentionally left blank for extra answer space, scratch work, caricatures of the course staff, doodles of your winter break plans or anything else you desire which fits here.

# **MIPS** Reference Data

1

| CORE INSTRUCTION SET           |                                                                                                                                                                                                                                                                                                                                                           |     |                                                                               |      |                       |  |  |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------|------|-----------------------|--|--|

|                                | MNE-                                                                                                                                                                                                                                                                                                                                                      |     |                                                                               |      | OPCODE/               |  |  |

| NAME                           | MON-                                                                                                                                                                                                                                                                                                                                                      |     |                                                                               |      | FUNCT                 |  |  |

| NAME                           | IC                                                                                                                                                                                                                                                                                                                                                        | MAT |                                                                               | (1)  | (Hex)                 |  |  |

| Add                            | add                                                                                                                                                                                                                                                                                                                                                       | R   | R[rd] = R[rs] + R[rt]                                                         | (1)  | 0 / 20 <sub>hex</sub> |  |  |

| Add Immediate                  | addi                                                                                                                                                                                                                                                                                                                                                      | I   |                                                                               | )(2) | 8 <sub>hex</sub>      |  |  |

| Add Imm. Unsigned              | addiu                                                                                                                                                                                                                                                                                                                                                     |     | R[rt] = R[rs] + SignExtImm                                                    | (2)  | 9 <sub>hex</sub>      |  |  |

| Add Unsigned                   | addu                                                                                                                                                                                                                                                                                                                                                      | R   | R[rd] = R[rs] + R[rt]                                                         |      | 0 / 21 <sub>hex</sub> |  |  |

| And                            | and                                                                                                                                                                                                                                                                                                                                                       | R   | R[rd] = R[rs] & R[rt]                                                         |      | 0 / 24 <sub>hex</sub> |  |  |

| And Immediate                  | andi                                                                                                                                                                                                                                                                                                                                                      | I   | R[rt] = R[rs] & ZeroExtImm                                                    | (3)  | chex                  |  |  |

| Branch On Equal                | beq                                                                                                                                                                                                                                                                                                                                                       | I   | if(R[rs]==R[rt])<br>PC=PC+4+BranchAddr*4                                      | (4)  | 4 <sub>hex</sub>      |  |  |

| Branch On Not Equa             | lbne                                                                                                                                                                                                                                                                                                                                                      | I   | if(R[rs]!=R[rt])<br>PC=PC+4+BranchAddr*4                                      | (4)  | $5_{hex}$             |  |  |

| Jump                           | j                                                                                                                                                                                                                                                                                                                                                         | J   | PC=JumpAddr                                                                   | (5)  | 2 <sub>hex</sub>      |  |  |

| Jump And Link                  | jal                                                                                                                                                                                                                                                                                                                                                       | J   | R[31]=PC+4;PC=JumpAddr                                                        | (5)  | 3 <sub>hex</sub>      |  |  |

| Jump Register                  | jr                                                                                                                                                                                                                                                                                                                                                        | R   | PC=R[rs]                                                                      |      | 0 / 08 <sub>hex</sub> |  |  |

| Load Byte Unsigned             | lbu                                                                                                                                                                                                                                                                                                                                                       | I   | R[rt]={24'b0,M[R[rs]<br>+SignExtImm](7:0)}                                    | (2)  | 24 <sub>hex</sub>     |  |  |

| Load Halfword<br>Unsigned      | lhu                                                                                                                                                                                                                                                                                                                                                       | I   | R[rt]={16'b0,M[R[rs]<br>+SignExtImm](15:0)}                                   | (2)  | $25_{hex}$            |  |  |

| Load Upper Imm.                | lui                                                                                                                                                                                                                                                                                                                                                       | I   | $R[rt] = \{imm, 16'b0\}$                                                      |      | fhex                  |  |  |

| Load Word                      | lw                                                                                                                                                                                                                                                                                                                                                        | I   | R[rt] = M[R[rs]+SignExtImm]                                                   | (2)  | $23_{hex}$            |  |  |

| Nor                            | nor                                                                                                                                                                                                                                                                                                                                                       | R   | $R[rd] = \sim (R[rs]   R[rt])$                                                |      | 0 / 27 <sub>hex</sub> |  |  |

| Or                             | or                                                                                                                                                                                                                                                                                                                                                        | R   | R[rd] = R[rs]   R[rt]                                                         |      | 0 / 25 <sub>hex</sub> |  |  |

| Or Immediate                   | ori                                                                                                                                                                                                                                                                                                                                                       | Ι   | R[rt] = R[rs]   ZeroExtImm                                                    | (3)  | d <sub>hex</sub>      |  |  |

| Set Less Than                  | slt                                                                                                                                                                                                                                                                                                                                                       | R   | R[rd] = (R[rs] < R[rt]) ? 1 : 0                                               |      | 0 / 2a <sub>hex</sub> |  |  |

| Set Less Than Imm.             | slti                                                                                                                                                                                                                                                                                                                                                      | Ι   | R[rt] = (R[rs] < SignExtImm)<br>? 1 : 0                                       | (2)  | a <sub>hex</sub>      |  |  |

| Set Less Than Imm.<br>Unsigned | sltiu                                                                                                                                                                                                                                                                                                                                                     | Ι   | R[rt] = (R[rs] < SignExtImm)<br>? 1 : 0 (2                                    | )(6) | b <sub>hex</sub>      |  |  |

| Set Less Than<br>Unsigned      | sltu                                                                                                                                                                                                                                                                                                                                                      | R   | R[rd] = (R[rs] < R[rt]) ? 1 : 0                                               | (6)  | $0 / 2b_{hex}$        |  |  |

| Shift Left Logical             | sll                                                                                                                                                                                                                                                                                                                                                       | R   | $R[rd] = R[rt] \leq shamt$                                                    |      | 0 / 00 <sub>hex</sub> |  |  |

| Shift Right Logical            | srl                                                                                                                                                                                                                                                                                                                                                       | R   | R[rd] = R[rt] >> shamt                                                        |      | 0 / 02 <sub>hex</sub> |  |  |

| Store Byte                     | sb                                                                                                                                                                                                                                                                                                                                                        | I   | M[R[rs]+SignExtImm](7:0) =<br>R[rt](7:0)                                      | (2)  | $28_{hex}$            |  |  |

| Store Halfword                 | sh                                                                                                                                                                                                                                                                                                                                                        | Ι   | M[R[rs]+SignExtImm](15:0) =<br>R[rt](15:0)                                    | (2)  | $29_{hex}$            |  |  |

| Store Word                     | SW                                                                                                                                                                                                                                                                                                                                                        | I   | M[R[rs]+SignExtImm] = R[rt]                                                   | (2)  | 2b <sub>hex</sub>     |  |  |

| Subtract                       | sub                                                                                                                                                                                                                                                                                                                                                       | R   | $\mathbf{R}[\mathbf{rd}] = \mathbf{R}[\mathbf{rs}] - \mathbf{R}[\mathbf{rt}]$ | (1)  | 0 / 22 <sub>hex</sub> |  |  |

| Subtract Unsigned              | subu                                                                                                                                                                                                                                                                                                                                                      | R   | R[rd] = R[rs] - R[rt]                                                         |      | 0 / 23 <sub>hex</sub> |  |  |

|                                | <ul> <li>(1) May cause overflow exception</li> <li>(2) SignExtImm = { 16{immediate[15]}, immediate }</li> <li>(3) ZeroExtImm = { 16{1b'0}, immediate }</li> <li>(4) BranchAddr = { 14{immediate[15]}, immediate, 2'b0 }</li> <li>(5) JumpAddr = { PC[31:28], address, 2'b0 }</li> <li>(6) Operands considered unsigned numbers (vs. 2 s comp.)</li> </ul> |     |                                                                               |      |                       |  |  |

| BASIC INSTRUCT                 |                                                                                                                                                                                                                                                                                                                                                           | RMA | TS                                                                            |      |                       |  |  |

| D onada                        | -                                                                                                                                                                                                                                                                                                                                                         |     | at ad abamt                                                                   |      | funct                 |  |  |

| R | opcode | rs    | rt    | rd      | shamt     | funct |

|---|--------|-------|-------|---------|-----------|-------|

|   | 31 26  | 25 21 | 20 16 | 15 11   | 10 6      | 5 0   |

| I | opcode | rs    | rt    |         | immediate | e     |

|   | 31 26  | 25 21 | 20 16 | 15      |           | 0     |

| J | opcode |       |       | address |           |       |

|   | 31 26  | 25    |       |         |           | 0     |

| ARITHMETIC CO        |                 | TRU     | CTION SET (2)                                                       | OPCODE/   |

|----------------------|-----------------|---------|---------------------------------------------------------------------|-----------|

|                      | MNE-            |         |                                                                     | FMT / FT/ |

|                      | MON-            |         |                                                                     | FUNCT     |

| NAME                 |                 | MAT     |                                                                     | (Hex)     |

| Branch On FP True    | bc1t            | FI      | if(FPcond)PC=PC+4+BranchAddr (4)                                    |           |

| Branch On FP False   |                 | FI      | if(!FPcond)PC=PC+4+BranchAddr(4)                                    |           |

| Divide               | div             | R       | Lo=R[rs]/R[rt]; Hi=R[rs]%R[rt]                                      | 0///1a    |

| Divide Unsigned      | divu            | R       | Lo=R[rs]/R[rt]; Hi=R[rs]%R[rt] (6)                                  |           |

| FP Add Single        | add.s           | FR      | F[fd] = F[fs] + F[ft]                                               | 11/10//0  |

| FP Add<br>Double     | add.d           | FR      | ${F[fd],F[fd+1]} = {F[fs],F[fs+1]} + {F[ft],F[ft+1]}$               | 11/11//0  |

| FP Compare Single    | c.x.s*          | FR      | FPcond = (F[fs] op F[ft])?1:0                                       | 11/10//y  |

| FP Compare<br>Double | c. <i>x</i> .d* | FR      | $FPcond = ({F[fs], F[fs+1]} op {F[ft], F[ft+1]})? 1:0$              | 11/11//y  |

|                      | rle) (          | on is = | =, <,  or  <=) (y  is  32, 3c,  or  3e)                             |           |

| FP Divide Single     |                 |         | F[fd] = F[fs] / F[ft]                                               | 11/10//3  |

| FP Divide            | div.d           | ED      | ${F[fd],F[fd+1]} = {F[fs],F[fs+1]} /$                               | 11/11/ /2 |

| Double               | aiv.a           | ГK      | {F[ft],F[ft+1]}                                                     | 11/11//3  |

| FP Multiply Single   | mul.s           | FR      | F[fd] = F[fs] * F[ft]                                               | 11/10//2  |

| FP Multiply          | mul.d           | FR      | ${F[fd],F[fd+1]} = {F[fs],F[fs+1]} *$                               | 11/11//2  |

| Double               | mar.a           | IK      | {F[ft],F[ft+1]}                                                     | 11/11//2  |

| FP Subtract Single   | sub.s           | FR      | F[fd]=F[fs] - F[ft]                                                 | 11/10//1  |

| FP Subtract          | sub.d           | FR      | ${F[fd],F[fd+1]} = {F[fs],F[fs+1]} -$                               | 11/11//1  |

| Double               |                 |         | {F[ft],F[ft+1]}                                                     |           |

| Load FP Single       | lwc1            | I       | F[rt]=M[R[rs]+SignExtImm] (2)                                       | 31//      |

| Load FP              | ldc1            | I       | F[rt]=M[R[rs]+SignExtImm]; (2)                                      | 35///     |

| Double               |                 |         | F[rt+1]=M[R[rs]+SignExtImm+4]                                       |           |

| Move From Hi         | mfhi            | R       | R[rd] = Hi                                                          | 0 ///10   |

| Move From Lo         | mflo            | R       | R[rd] = Lo                                                          | 0 ///12   |

| Move From Control    |                 | R       | R[rd] = CR[rs]                                                      | 16 /0//0  |

| Multiply             | mult            | R       | ${Hi,Lo} = R[rs] * R[rt]$                                           | 0///18    |

| Multiply Unsigned    |                 | R       | ${Hi,Lo} = R[rs] * R[rt]$ (6)                                       |           |

| Store FP Single      | swc1            | I       | M[R[rs]+SignExtImm] = F[rt] (2)                                     | 39///     |

| Store FP<br>Double   | sdc1            | Ι       | M[R[rs]+SignExtImm] = F[rt]; (2)<br>M[R[rs]+SignExtImm+4] = F[rt+1] | 3d///     |

|                      |                 |         |                                                                     |           |

## FLOATING POINT INSTRUCTION FORMATS

| FR | opcode | fmt   | ft    | fs    | fd        | funct |

|----|--------|-------|-------|-------|-----------|-------|

|    | 31 26  | 25 21 | 20 16 | 15 11 | 10 6      | 5 0   |

| FI | opcode | fmt   | ft    |       | immediate | e     |

|    | 31 26  | 25 21 | 20 16 | 15    |           | 0     |

#### PSEUDO INSTRUCTION SET

| NAME                         | MNEMONIC | OPERATION                                    |

|------------------------------|----------|----------------------------------------------|

| Branch Less Than             | blt      | if(R[rs] <r[rt]) pc="Label&lt;/td"></r[rt])> |

| Branch Greater Than          | bgt      | if(R[rs]>R[rt]) PC = Label                   |

| Branch Less Than or Equal    | ble      | $if(R[rs] \le R[rt]) PC = Label$             |

| Branch Greater Than or Equal | bge      | if(R[rs]>=R[rt]) PC = Label                  |

| Load Immediate               | 1i       | R[rd] = immediate                            |

| Move                         | move     | R[rd] = R[rs]                                |

|                              |          |                                              |

#### REGISTER NAME, NUMBER, USE, CALL CONVENTION

| NAME      | NUMBER | USE                                                      | PRESERVEDACROSS |

|-----------|--------|----------------------------------------------------------|-----------------|

| NAME      | NUMBER | USE                                                      | A CALL?         |

| \$zero    | 0      | The Constant Value 0                                     | N.A.            |

| \$at      | 1      | Assembler Temporary                                      | No              |

| \$v0-\$v1 | 2-3    | Values for Function Results<br>and Expression Evaluation | No              |

| \$a0-\$a3 | 4-7    | Arguments                                                | No              |

| \$t0-\$t7 | 8-15   | Temporaries                                              | No              |

| \$s0-\$s7 | 16-23  | Saved Temporaries                                        | Yes             |

| \$t8-\$t9 | 24-25  | Temporaries                                              | No              |

| \$k0-\$k1 | 26-27  | Reserved for OS Kernel                                   | No              |

| \$gp      | 28     | Global Pointer                                           | Yes             |

| \$sp      | 29     | Stack Pointer                                            | Yes             |

| \$fp      | 30     | Frame Pointer                                            | Yes             |

| \$ra      | 31     | Return Address                                           | No              |

Copyright 2005 by Elsevier, Inc., All rights reserved. From Patterson and Hennessy, Computer Organization and Design, 3rd ed.

| OPCOD  | DES, BASE | E CONVER        | ISION.  | ASCII | SYME      | OLS   |       | 3         |            |

|--------|-----------|-----------------|---------|-------|-----------|-------|-------|-----------|------------|

|        | (1) MIPS  | (2) MIPS        | ,       |       |           | ASCII | h .   | Hexa-     | ASCI       |

| opcode | funct     | funct           | Binary  | Deci- | deci-     | Char- | Deci- | deci-     | Char       |

| 31:26) | (5:0)     | (5:0)           |         | mal   | mal       | acter | mal   | mal       | acter      |

| (1)    | s11       | add.f           | 00 0000 | ) 0   | 0         | NUL   | 64    | 40        |            |

| (1)    | SII       |                 | 00 000  |       |           | SOH   | 65    | 40        | Ă          |

|        |           | sub.f           |         |       | 1         |       |       |           |            |

| j      | srl       | mul <i>f</i>    | 00 0010 |       | 2         | STX   | 66    | 42        | B          |

| jal    | sra       | div.f           | 00 001  |       | 3         | ETX   | 67    | 43        | С          |

| beq    | sllv      | sqrtf           | 00 0100 |       | 4         | EOT   | 68    | 44        | D          |

| bne    |           | abs.f           | 00 010  | 15    | 5         | ENQ   | 69    | 45        | E          |

| blez   | srlv      | mov.f           | 00 0110 | ) 6   | 6         | ACK   | 70    | 46        | F          |

| bgtz   | srav      | neg.f           | 00 011  | 17    | 7         | BEL   | 71    | 47        | G          |

| addi   | jr        | 55              | 00 1000 | ) 8   | 8         | BS    | 72    | 48        | Н          |

| addiu  | jalr      |                 | 00 100  |       | 9         | HT    | 73    | 49        | Ĩ          |

| slti   |           |                 | 00 101  |       | -         | LF    | 74    | 4a        | Ĵ          |

|        | movz      |                 |         |       | a         |       |       |           |            |

| sltiu  | movn      |                 | 00 101  |       | b         | VT    | 75    | <u>4b</u> | K          |

| andi   | syscall   | round.w.f       | 00 1100 |       | с         | FF    | 76    | 4c        | L          |

| ori    | break     | trunc.w.f       | 00 110  |       | d         | CR    | 77    | 4d        | Μ          |

| xori   |           | ceil.w.f        | 00 1110 |       | e         | SO    | 78    | 4e        | N          |

| lui    | sync      | floor.w.f       | 00 111  | 1 15  | f         | SI    | 79    | 4f        | 0          |

|        | mfhi      |                 | 01 0000 |       | 10        | DLE   | 80    | 50        | Р          |

| (2)    | mthi      |                 | 01 000  |       | 11        | DC1   | 81    | 51        | Q          |

| (-)    | mflo      | movz.f          | 01 0010 |       | 12        | DC2   | 82    | 52        | Ř          |

|        | mtlo      |                 | 01 001  |       | 13        | DC3   | 83    | 53        | S          |

|        | mero      | movn.f          |         |       | 13        | DC3   | 84    | - 55      | - <u>T</u> |

|        |           |                 | 01 0100 |       |           |       |       |           |            |

|        |           |                 | 01 010  |       | 15        | NAK   | 85    | 55        | U          |

|        |           |                 | 01 0110 |       | 16        | SYN   | 86    | 56        | V          |

|        |           |                 | 01 011  |       | 17        | ETB   | 87    | 57        | W          |

|        | mult      |                 | 01 1000 | ) 24  | 18        | CAN   | 88    | 58        | Х          |

|        | multu     |                 | 01 100  | 1 25  | 19        | EM    | 89    | 59        | Y          |

|        | div       |                 | 01 1010 | ) 26  | la        | SUB   | 90    | 5a        | Z          |

|        | divu      |                 | 01 101  |       | 1b        | ESC   | 91    | 5b        | ]          |

|        | diva      |                 | 01 1100 |       | 10        | FS    | 92    | 5c        |            |

|        |           |                 | 01 110  |       | 1d        | GS    | 93    | 5d        |            |

|        |           |                 |         |       |           |       | 93    |           | j          |

|        |           |                 | 01 1110 |       | 1e        | RS    |       | 5e        |            |

|        |           |                 | 01 111  |       | 1f        | US    | 95    | 5f        |            |

| lb     | add       | cvt.s.f         | 10 0000 |       | 20        | Space | 96    | 60        | ·          |

| lh     | addu      | cvt.d.f         | 10 000  |       | 21        | !     | 97    | 61        | а          |

| lwl    | sub       |                 | 10 0010 | ) 34  | 22        | "     | 98    | 62        | b          |

| lw     | subu      |                 | 10 001  | 1 35  | 23        | #     | 99    | 63        | с          |

| lbu    | and       | cvt.w.          | 10 0100 | ) 36  | 24        | \$    | 100   | 64        | d          |

| lhu    | or        | y               | 10 010  |       | 25        | %     | 101   | 65        | e          |

| lwr    | xor       |                 | 10 0110 |       | 26        | &     | 101   | 66        | f          |

| TWT    |           |                 |         |       |           | Ģ,    | 102   |           |            |

|        | nor       |                 | 10 011  |       | 27        |       |       | 67        | g          |

| sb     |           |                 | 10 1000 |       | 28        | (     | 104   | 68        | h          |

| sh     |           |                 | 10 100  |       | 29        | )     | 105   | 69        | i          |

| swl    | slt       |                 | 10 1010 |       | 2a        |       | 106   | 6a        | j          |

| SW     | sltu      |                 | 10 101  |       | 2b        | +     | 107   | 6b        | k          |

|        |           |                 | 10 1100 | ) 44  | 2c        | ,     | 108   | 6c        | 1          |

|        |           |                 | 10 110  |       | 2d        | -     | 109   | 6d        | m          |

| swr    |           |                 | 10 1110 |       | 2e        |       | 110   | 6e        | n          |

| cache  |           |                 | 10 111  |       | 2f        | ;     | 111   | 6f        | 0          |

| 11     | tge       | c.f.f           | 11 0000 |       | 30        | 0     | 112   | 70        | -          |

|        |           |                 | 11 000  |       | 31        | 1     | 112   | 71        | p          |

| lwc1   | tgeu      | c.un.f          |         |       |           |       |       |           | q          |

| lwc2   | tlt       | c.eq.f          | 11 0010 |       | 32        | 2     | 114   | 72        | r          |

| pref   | tltu      | c.ueq.f         | 11 001  |       | 33        | 3     | 115   | 73        | S          |

|        | teq       | c.olt <i>f</i>  | 11 0100 |       | 34        | 4     | 116   | 74        | t          |

| ldc1   |           | c.ult.f         | 11 010  |       | 35        | 5     | 117   | 75        | u          |

| ldc2   | tne       | c.ole.f         | 11 0110 | ) 54  | 36        | 6     | 118   | 76        | v          |

|        |           | c.ule.f         | 11 011  |       | 37        | 7     | 119   | 77        | w          |

| sc     |           | c.sf.f          | 11 1000 |       | 38        | 8     | 120   | 78        | x          |

| swc1   |           |                 | 11 100  |       | 39        | 9     | 120   | 79        |            |

|        |           | c.ngle <i>f</i> |         |       | 39<br>3a  |       | 121   |           | у          |

| swc2   |           | c.seqf          | 11 1010 |       |           | :     |       | 7a<br>7h  | Z          |

|        |           | c.ngl.f         | 11 101  |       | <u>3b</u> | ;     | 123   | 7b        | {          |

|        |           | c.lt.f          | 11 1100 |       | 3c        | <     | 124   | 7c        |            |

| sdc1   |           | c.nge.f         | 11 110  |       | 3d        | =     | 125   | 7d        | }          |

|        |           |                 |         | ) 62  | 2         | >     | 126   | 7e        | ~          |

| sdc2   |           | c.le.f          | 11 1110 | J 62  | 3e        | ~     | 120   | /e        |            |

## (1) opcode(31:26) == 0(2) opcode(31:26) == 17). if fmt(25.21)==16... $(10_{har}) f = s$ (single);

| (2) op | $code(31:26) = 17_{ten} (11_{hex}); \text{ if } tmt(25:21) = 16_{ten} (10_{hex})$ | f = s | (single) |

|--------|-----------------------------------------------------------------------------------|-------|----------|

| ift    | $fmt(25:21) = 17_{ten} (11_{hex}) f = d (double)$                                 |       |          |

|        |                                                                                   |       |          |

10-21

Copyright 2005 by Elsevier, Inc., All rights reserved. From Patterson and Hennessy, Computer Organization and Design, 3rd ed.