| Reading Summary<br>Chapter 1: Skim                                      |  |

|-------------------------------------------------------------------------|--|

| ,<br>Chapter 2: 2.1-2.8, 2.10; 2.12-2.14 Skim                           |  |

| Chapter 3: 3.5                                                          |  |

| Chapter 4: 4.1-4.4; 4.5-4.9                                             |  |

| Chapter 5: 5.1-5.8                                                      |  |

| Chapter 6: 6.3, 6.5-6.6                                                 |  |

| [Some material on multicore from Ch. 7; not responsible for any of it.] |  |

|                                                                         |  |

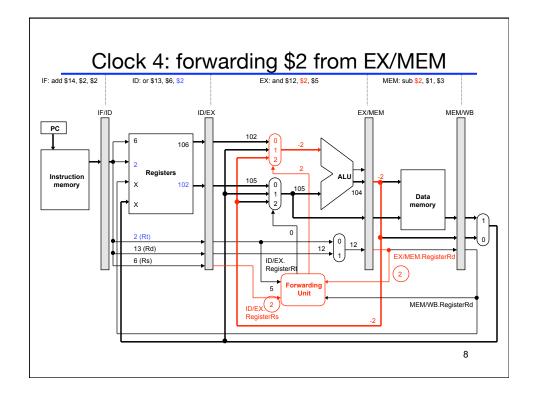

## **Design of Pipelined MIPS**

MIPS design:

- Know all components and their operation

- Know flow of logic -- which components are active when implementing a given operation

- Be able to specify control signals needed to accomplish specific instructions

- ✤Be able to compare with 1-cycle, multi-cycle

- Know the issues in pipelined performance

- Why is write back last for addi?

- Why do we want to move branch decision logic earlier?

3

• Give examples of problems from instructions being started before preceding instructions are complete

<text><text><text><text><text><text>