| Detecting stalls |                                                                                                                                                                                                                                              |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

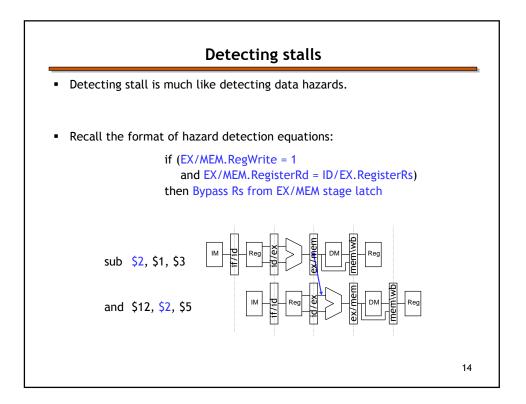

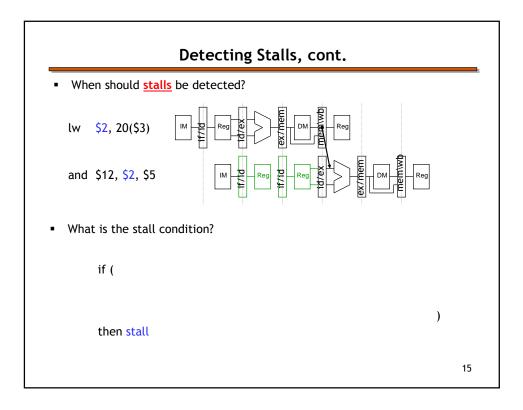

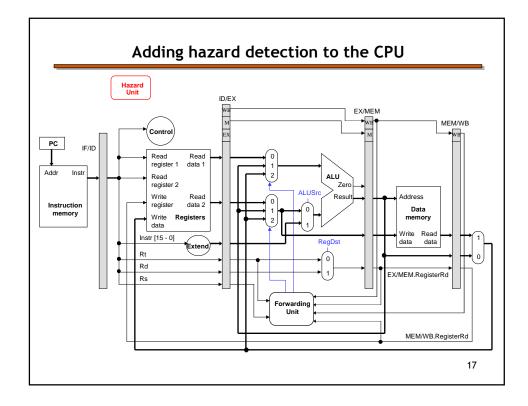

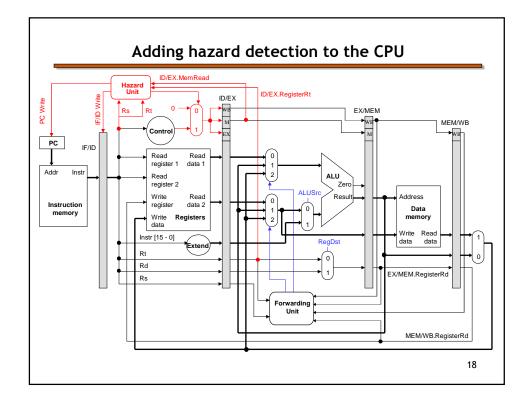

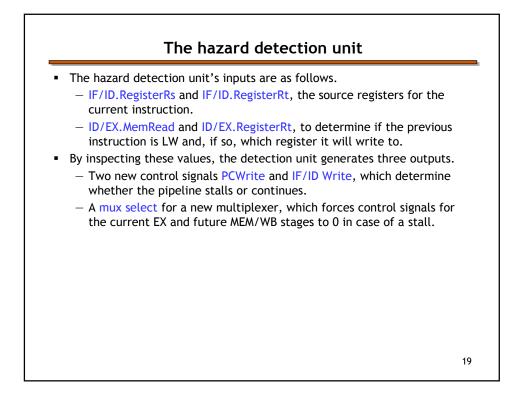

|                  | <ul> <li>We can detect a load hazard between the current instruction in its ID stage and the previous instruction in the EX stage just like we detected data hazards.</li> <li>A hazard occurs if the previous instruction was LW</li> </ul> |  |  |

|                  | ID/EX.MemRead = 1                                                                                                                                                                                                                            |  |  |

|                  | and the LW destination is one of the current source registers.                                                                                                                                                                               |  |  |

|                  | ID/EX.RegisterRt = IF/ID.RegisterRs<br>or<br>ID/EX.RegisterRt = IF/ID.RegisterRt                                                                                                                                                             |  |  |

|                  | <ul> <li>The complete test for stalling is the conjunction of these two conditions.</li> </ul>                                                                                                                                               |  |  |

|                  | <pre>if (ID/EX.MemRead = 1 and<br/>(ID/EX.RegisterRt = IF/ID.RegisterRs or<br/>ID/EX.RegisterRt = IF/ID.RegisterRt))<br/>then stall</pre>                                                                                                    |  |  |

|                  | 16                                                                                                                                                                                                                                           |  |  |

| Timing                                                                          |    |

|---------------------------------------------------------------------------------|----|

| <ul> <li>If no prediction:</li> </ul>                                           |    |

| IF ID EX MEM WB<br>IF IF ID EX MEM WB lost 1 cycle                              |    |

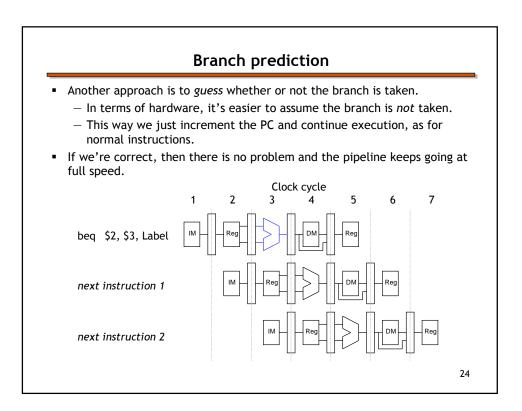

| <ul> <li>If prediction:</li> <li>If Correct</li> <li>IF ID EX MEM WB</li> </ul> |    |

| IF ID EX MEM WB no cycle lost                                                   |    |

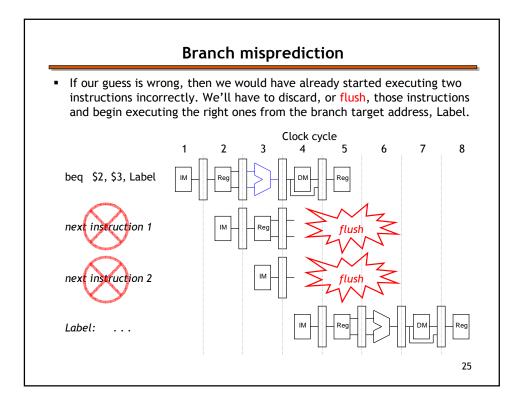

| <ul> <li>If Misprediction:</li> <li>IF ID EX MEM WB</li> </ul>                  |    |

| IFO IF1 ID EX MEM WB 1 cycle lost                                               |    |

|                                                                                 |    |

|                                                                                 | 30 |

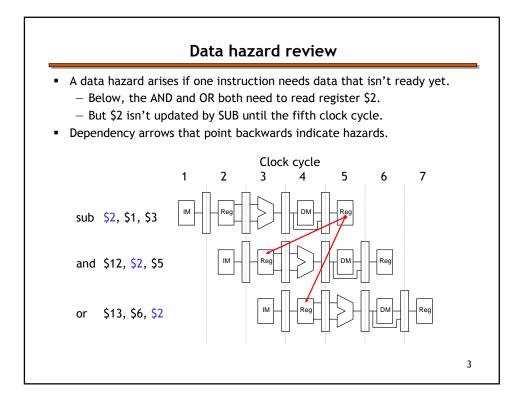

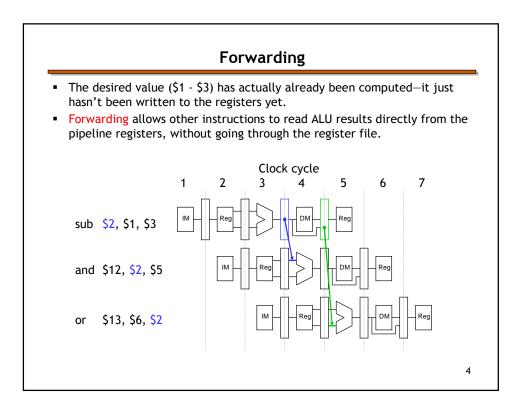

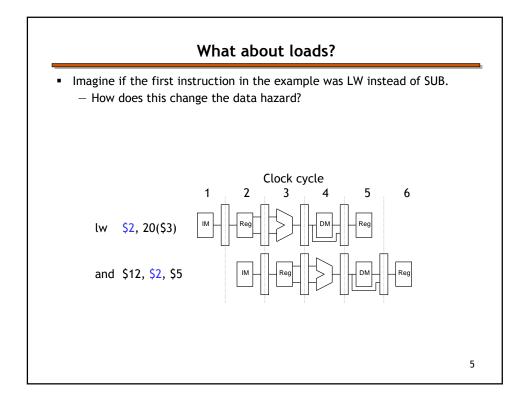

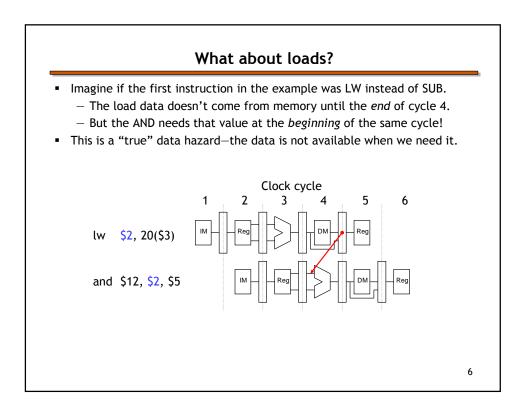

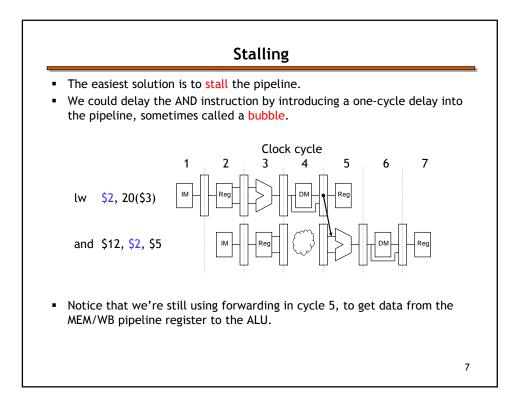

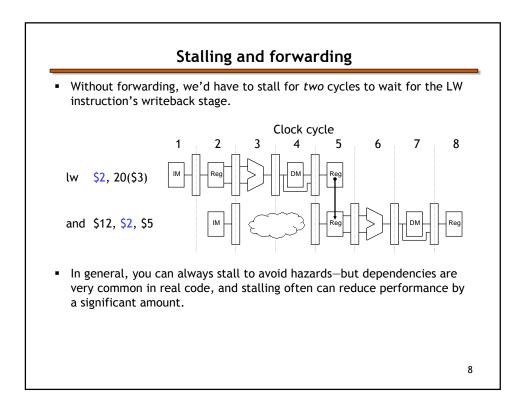

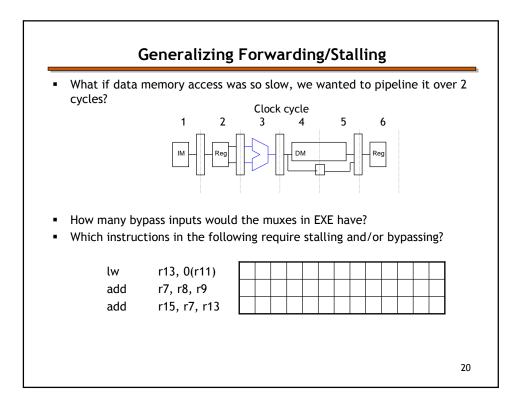

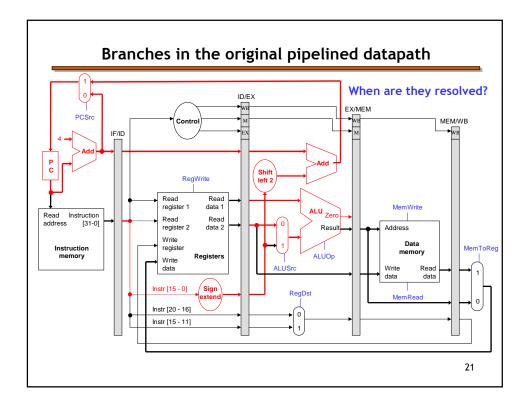

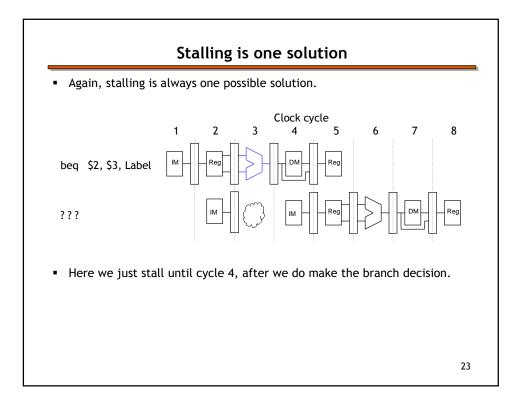

## Summary Three kinds of hazards conspire to make pipelining difficult. Structural hazards result from not having enough hardware available to . execute multiple instructions simultaneously. - These are avoided by adding more functional units (e.g., more adders or memories) or by redesigning the pipeline stages. Data hazards can occur when instructions need to access registers that haven't been updated yet. - Hazards from R-type instructions can be avoided with forwarding. - Loads can result in a "true" hazard, which must stall the pipeline. Control hazards arise when the CPU cannot determine which instruction . to fetch next. - We can minimize delays by doing branch tests earlier in the pipeline. - We can also take a chance and predict the branch direction, to make the most of a bad situation. 31