|                        | hole poi                       |          | pelinin | g is to  | allow r  | nultip    | le inst   | ructior | ns to ex | kecute |

|------------------------|--------------------------------|----------|---------|----------|----------|-----------|-----------|---------|----------|--------|

| • We m                 | ay need                        | to perfo | orm sev | veral o  | peratio  | ns in t   | the sar   | ne cvc  | le.      |        |

|                        | crement                        | •        |         |          | •        |           |           |         |          |        |

|                        | etch one                       |          |         | -        |          |           |           |         | data     |        |

|                        |                                | instruc  |         | inc un   |          |           |           | whites  | uutu.    |        |

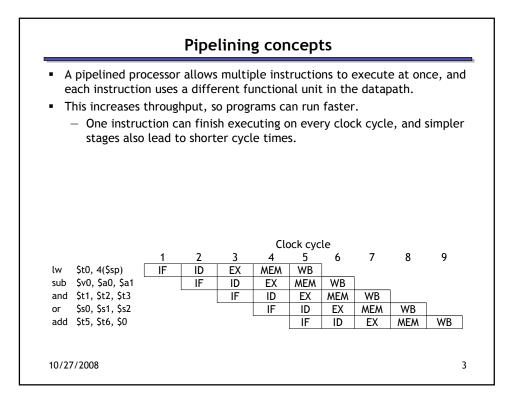

|                        |                                |          |         |          |          | ock cyc   | le        |         |          |        |

| L                      | 4(****                         | 1        | 2       | 3        | 4        | 5         | 6         | 7       | 8        | 9      |

|                        | 4(\$sp)                        | IF       | ID      | EX       | MEM      | WB        |           | 1       |          |        |

| sub \$v0,<br>and \$t1, | \$a0, \$a1                     |          | IF      | ID<br>IF | EX<br>ID | MEM<br>EX | WB<br>MEM | WB      | 1        |        |

| . ,                    | \$s1, \$s2                     |          |         | IF       | IF       |           | EX        | MEM     | WB       | 1      |

| add \$t5,              | . , .                          |          |         |          |          | IF        | ID        | EX      | MEM      | WB     |

| uuu <i>4</i> 00,       | <i>4</i> 00, 40                |          |         |          |          |           |           | LA      | /*\L/*\  | 110    |

| duplic                 | like the<br>ate hard<br>cycle. |          |         |          |          |           |           |         |          |        |

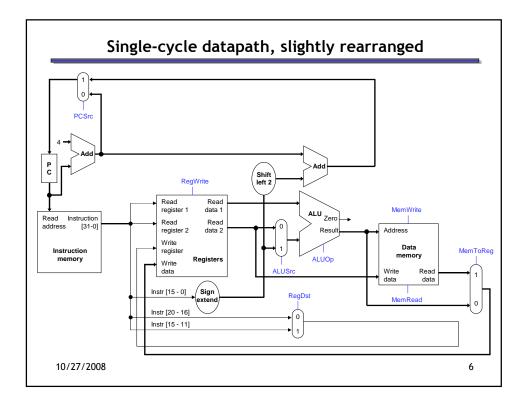

## What's been changed?

- Almost nothing! This is equivalent to the original single-cycle datapath.

- There are separate memories for instructions and data.

- There are two adders for PC-based computations and one ALU.

- The control signals are the same.

- Only some cosmetic changes were made to make the diagram smaller.

- A few labels are missing, and the muxes are smaller.

- The data memory has only one Address input. The actual memory operation can be determined from the MemRead and MemWrite control signals.

7

• The datapath components have also been moved around in preparation for adding pipeline registers.

10/27/2008

| Multiple cycles                                                                                                                                                                                                                                                                                                                                                         |   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

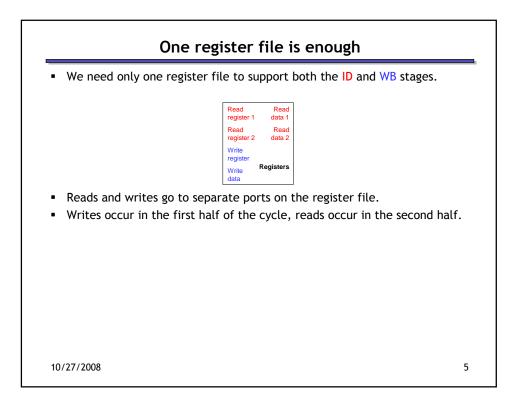

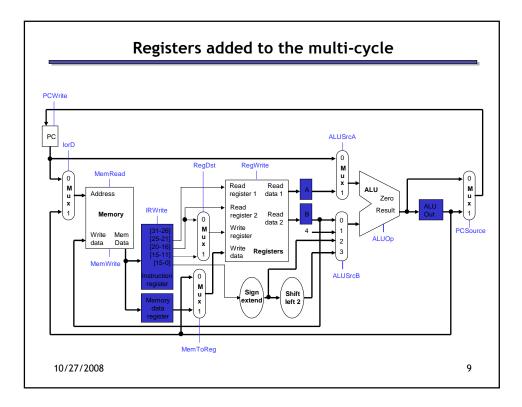

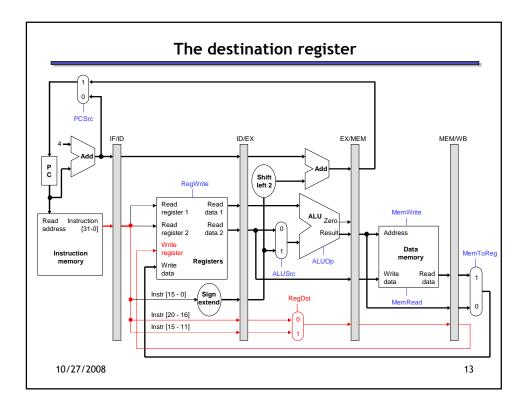

| <ul> <li>In pipelining, we also divide instruction execution into multiple cycles.</li> <li>Information computed during one cycle may be needed in a later cycle.</li> <li>The instruction read in the IF stage determines which registers are fetched in the ID stage, what constant is used for the EX stage, and what the destination register is for WB.</li> </ul> | _ |

| <ul> <li>The registers read in ID are used in the EX and/or MEM stages.</li> <li>The ALU output produced in the EX stage is an effective address for the MEM stage or a result for the WB stage.</li> <li>We added several intermediate registers to the multicycle datapath to</li> </ul>                                                                              |   |

| preserve information between stages, as highlighted on the next slide.                                                                                                                                                                                                                                                                                                  |   |

|                                                                                                                                                                                                                                                                                                                                                                         |   |

|                                                                                                                                                                                                                                                                                                                                                                         |   |

|                                                                                                                                                                                                                                                                                                                                                                         |   |

| 10/27/2008                                                                                                                                                                                                                                                                                                                                                              | 8 |

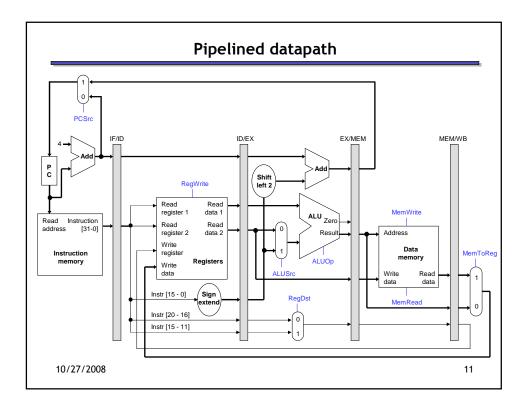

| Pipeline registers                                                                                                                                                                                                                                                                                  |       |                  |        |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------|--------|--|--|--|--|--|

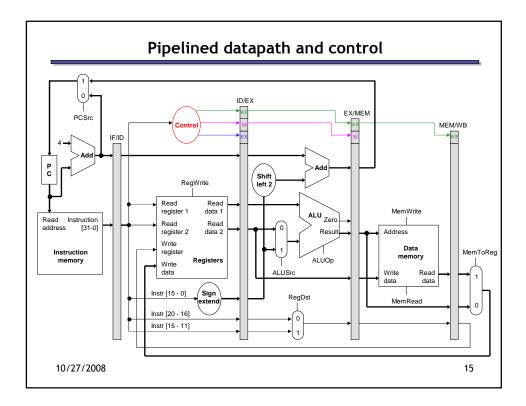

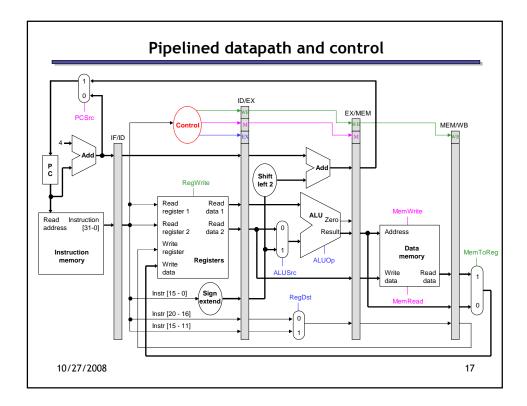

| <ul> <li>We'll add intermediate registers to our pipelined datapath too.</li> <li>There's a lot of information to save, however. We'll simplify our diagrams by drawing just one big pipeline register between each stage.</li> <li>The registers are named for the stages they connect.</li> </ul> |       |                  |        |  |  |  |  |  |

| IF/ID                                                                                                                                                                                                                                                                                               | ID/EX | EX/MEM           | MEM/WB |  |  |  |  |  |

| <ul> <li>No register is need<br/>instruction is done</li> </ul>                                                                                                                                                                                                                                     |       | stage, Decause a |        |  |  |  |  |  |

| 10/27/2008                                                                                                                                                                                                                                                                                          |       |                  | 10     |  |  |  |  |  |

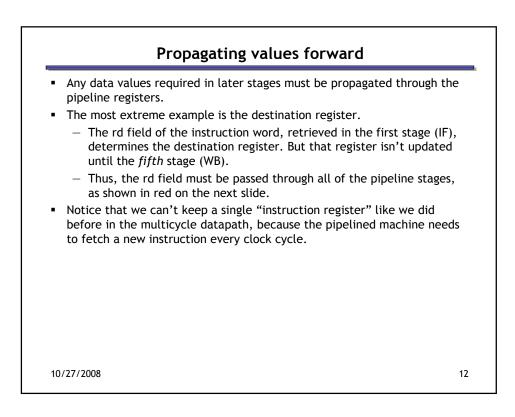

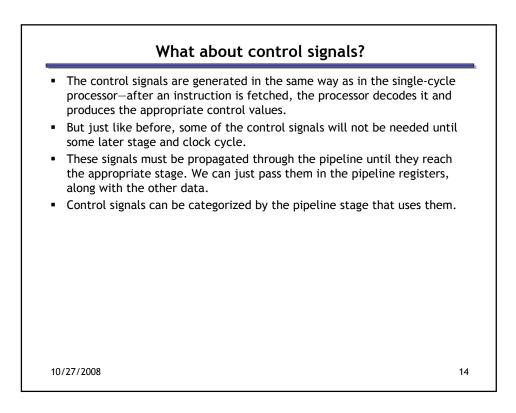

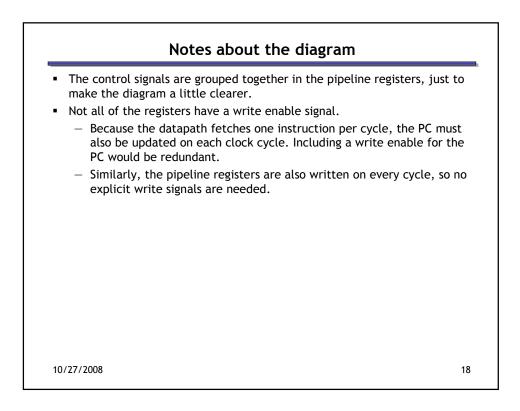

| processor-                       | The control signals are generated in the same way as in the single-cycle processor—after an instruction is fetched, the processor decodes it and produces the appropriate control values. |                          |                                       |                 |                    |     |  |  |  |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------------------|-----------------|--------------------|-----|--|--|--|

| <ul> <li>But just lik</li> </ul> | ke before,                                                                                                                                                                                |                          | e control sigi                        | nals will n     | ot be needed un    | til |  |  |  |

| along with                       | the other                                                                                                                                                                                 |                          | ust pass the                          | n in the p      | ipeline registers, |     |  |  |  |

| <ul> <li>Control sig</li> </ul>  | nals can b                                                                                                                                                                                | e categoriz              | ed by the pi                          | peline stag     | ge that uses then  | n.  |  |  |  |

| <ul> <li>Control sig</li> </ul>  | nals can b                                                                                                                                                                                | -                        | ed by the pip                         |                 | ge that uses ther  | n.  |  |  |  |

| <ul> <li>Control sig</li> </ul>  |                                                                                                                                                                                           | -                        |                                       |                 | ge that uses then  | n.  |  |  |  |

| <ul> <li>Control sig</li> </ul>  | Stage                                                                                                                                                                                     | Cor                      | ntrol signals ne                      | eeded           | ge that uses then  | n.  |  |  |  |

| <ul> <li>Control sig</li> </ul>  | Stage<br>EX                                                                                                                                                                               | Cor<br>ALUSrc            | ntrol signals ne                      | eeded<br>RegDst | ge that uses then  | n.  |  |  |  |

| <ul> <li>Control sig</li> </ul>  | Stage<br>EX<br>MEM                                                                                                                                                                        | Cor<br>ALUSrc<br>MemRead | ntrol signals ne<br>ALUOp<br>MemWrite | eeded<br>RegDst | ge that uses then  | n.  |  |  |  |

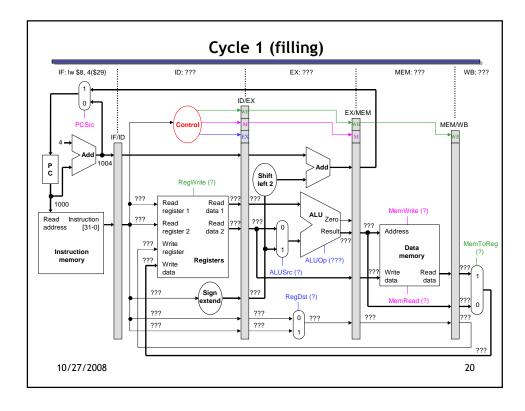

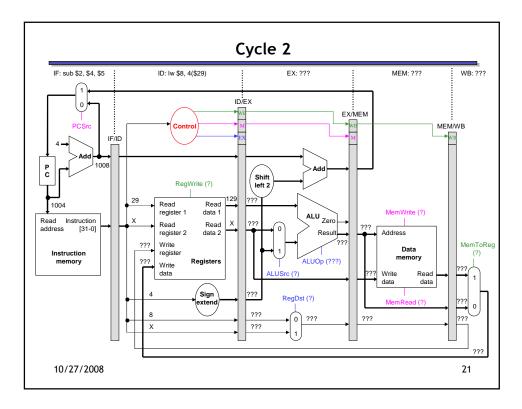

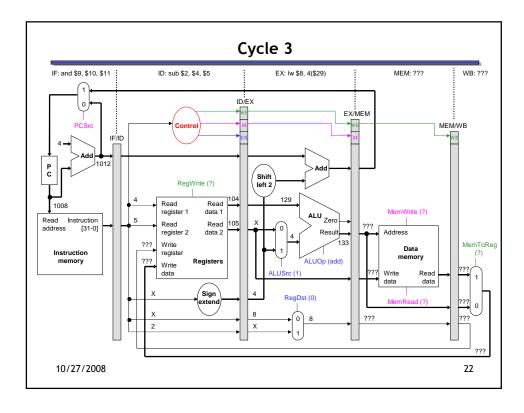

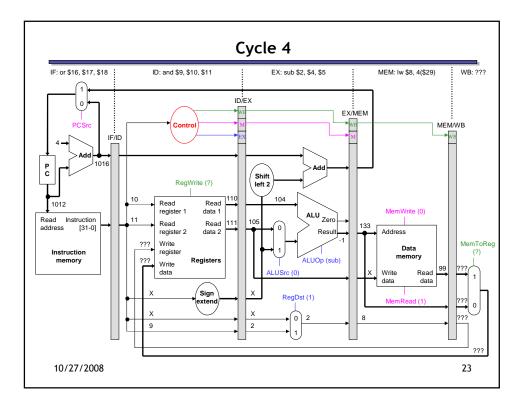

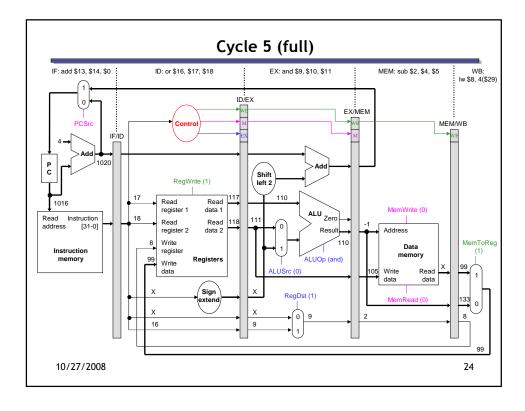

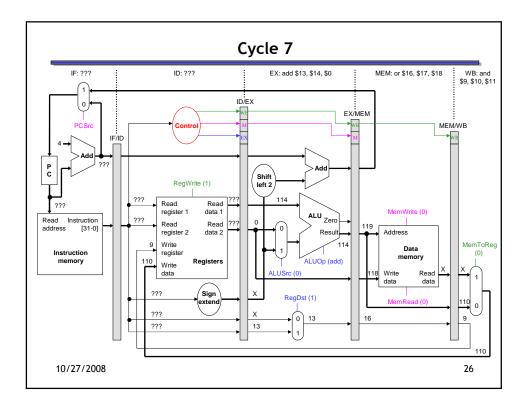

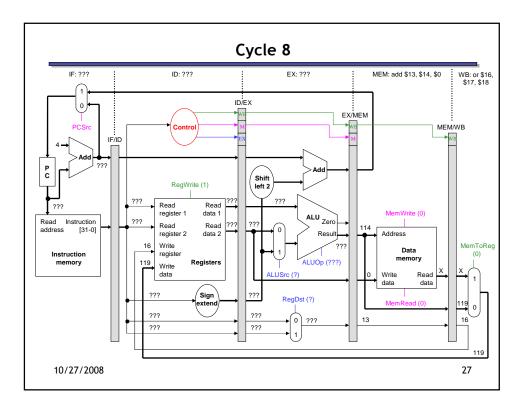

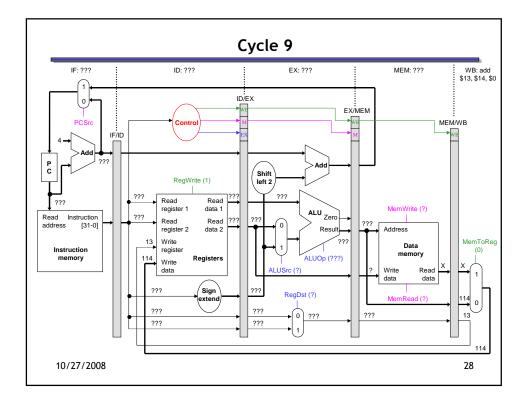

| <ul> <li>Here's a samp</li> </ul>                                                                                   | le sequence of instructions to execute.                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| addresses<br>in decimal                                                                                             | 1000: lw \$8, 4(\$29)<br>1004: sub \$2, \$4, \$5<br>1008: and \$9, \$10, \$11<br>1012: or \$16, \$17, \$18<br>1016: add \$13, \$14, \$0                                                                                                                                                                                             |

| <ul> <li>Each regis contains 1</li> <li>Every data</li> <li>Our pipeline d</li> <li>An X indic an R-type</li> </ul> | me assumptions, just so we can show actual data values.<br>ter contains its number plus 100. For instance, register \$8<br>08, register \$29 contains 129, and so forth.<br>a memory location contains 99.<br>iagrams will follow some conventions.<br>ates values that aren't important, like the constant field o<br>instruction. |

| -                                                                                                                   | narks ??? indicate values we don't know, usually resulting uctions coming before and after the ones in our example.                                                                                                                                                                                                                 |

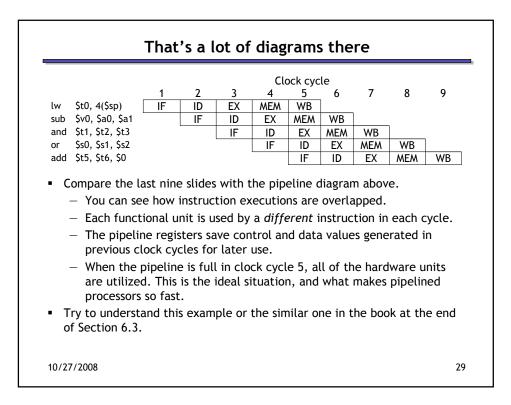

|     |                                                                 |          |         |        | Clo | ock cyc | le  |     |     |    |

|-----|-----------------------------------------------------------------|----------|---------|--------|-----|---------|-----|-----|-----|----|

|     |                                                                 | 1        | 2       | 3      | 4   | 5       | 6   | 7   | 8   | 9  |

| lw  | \$t0, 4(\$sp)                                                   | IF       | ID      | EX     | MEM | WB      |     |     |     |    |

| sub | 1 , 1 , 1                                                       |          | IF      | ID     | EX  | MEM     | WB  |     |     |    |

|     | \$t1, \$t2, \$t3                                                |          |         | IF     | ID  | EX      | MEM | WB  |     |    |

| or  | \$s0, \$s1, \$s2                                                |          |         |        | IF  | ID      | EX  | MEM | WB  |    |

| add | \$sp, \$sp, -4                                                  |          |         |        |     | IF      | ID  | EX  | MEM | WB |

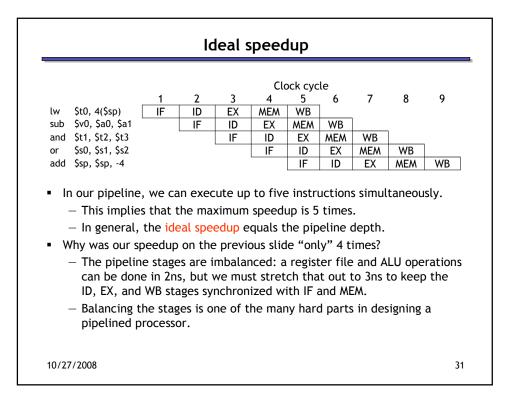

| lr  | ycle datapath<br>nstead, pipeli<br>er unit time.<br>lock cycle. | ning ind | creases | the th |     |         |     |     |     |    |

| Summary                                                                                                                                                                                                                                                                                                                                                                                                               | _  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

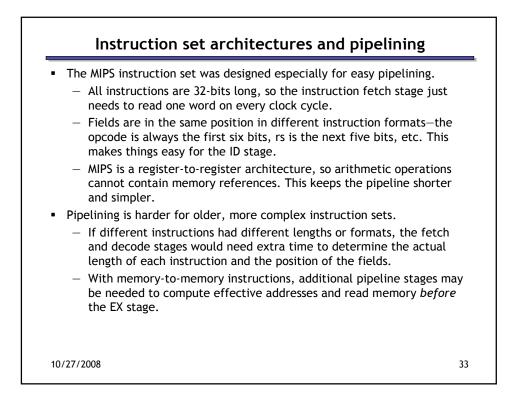

| <ul> <li>The pipelined datapath combines ideas from the single and multicycle processors that we saw earlier.         <ul> <li>It uses multiple memories and ALUs.</li> <li>Instruction execution is split into several stages.</li> </ul> </li> <li>Pipeline registers propagate data and control values to later stages.</li> <li>The MIPS instruction set architecture supports pipelining with uniform</li> </ul> |    |

| <ul> <li>The MIPS instruction set architecture supports pipelining with uniform<br/>instruction formats and simple addressing modes.</li> </ul>                                                                                                                                                                                                                                                                       |    |

| <ul> <li>Next lecture, we'll start talking about Hazards.</li> </ul>                                                                                                                                                                                                                                                                                                                                                  |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| 10/27/2008                                                                                                                                                                                                                                                                                                                                                                                                            | 34 |