|   | Pipelining Processors                                                                                                                                                                                          |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

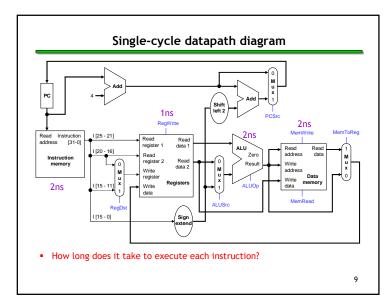

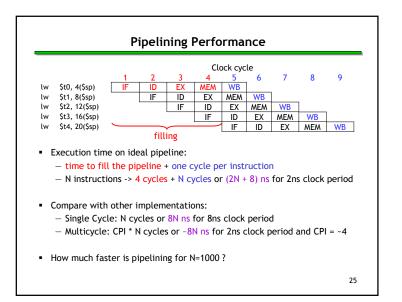

| • | <ul> <li>We've seen two possible implementations of the MIPS architecture.</li> <li>A single-cycle datapath executes each instruction in just one clock cycle, but the cycle time may be very long.</li> </ul> |

- A multicycle datapath has much shorter cycle times, but each instruction requires many cycles to execute.

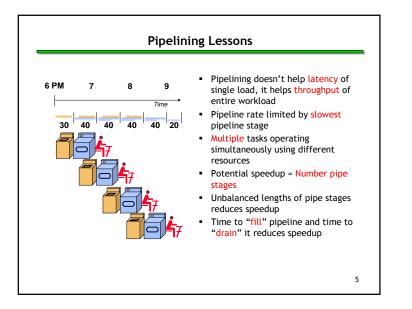

- Pipelining gives the best of both worlds and is used in just about every modern processor.

- Cycle times are short so clock rates are high.

- But we can still execute an instruction in about one clock cycle!

| Single Cycle Datapath | CPI = 1  | Long Cycle Time  |

|-----------------------|----------|------------------|

| Multi-cycle Datapath  | CPI = ~4 | Short Cycle Time |

| Pipelined Datapath    | CPI = ~1 | Short Cycle Time |

7

## Instruction execution review

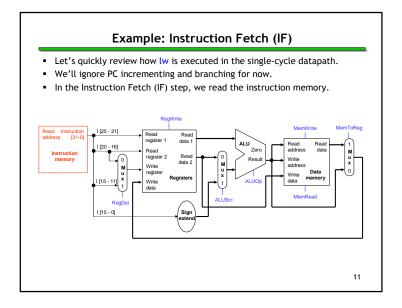

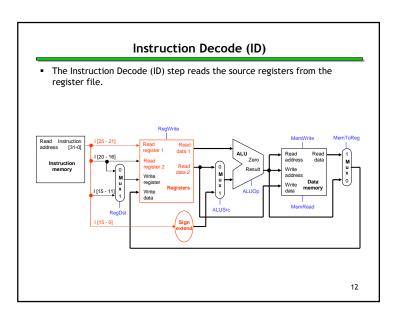

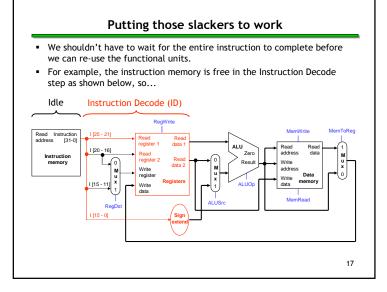

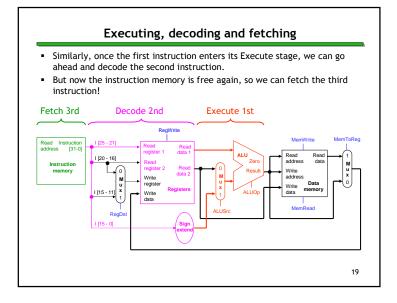

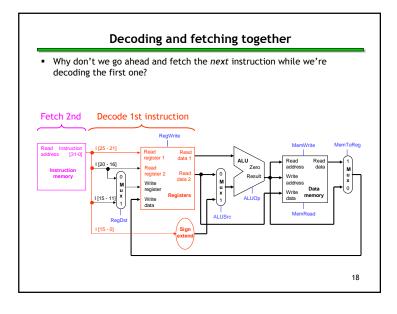

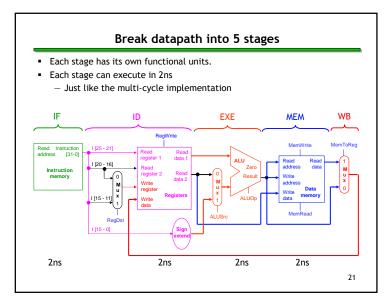

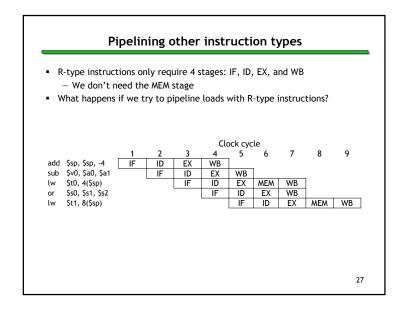

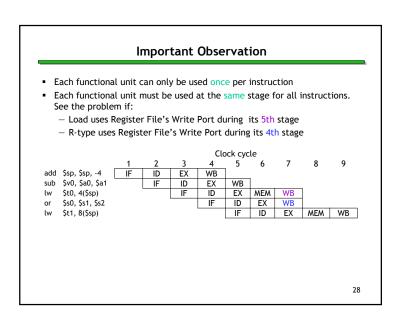

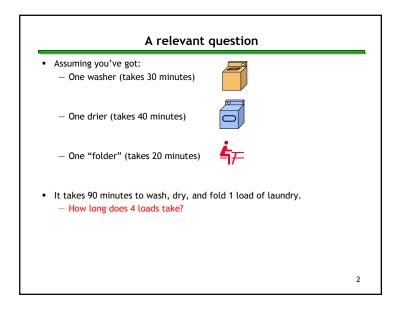

• Executing a MIPS instruction can take up to five steps.

| Step               | Name | Description                                         |

|--------------------|------|-----------------------------------------------------|

| Instruction Fetch  | IF   | Read an instruction from memory.                    |

| Instruction Decode | ID   | Read source registers and generate control signals. |

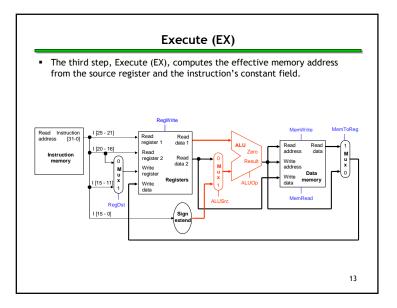

| Execute            | EX   | Compute an R-type result or a branch outcome.       |

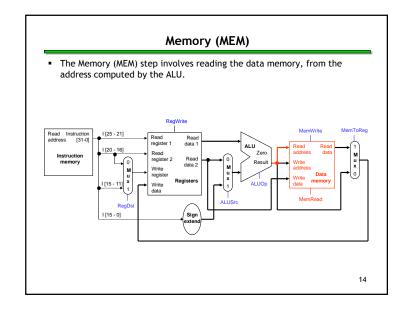

| Memory             | MEM  | Read or write the data memory.                      |

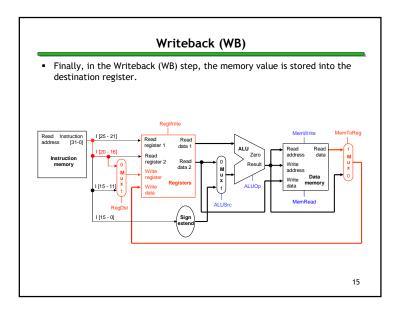

| Writeback          | WB   | Store a result in the destination register.         |

• However, as we saw, not all instructions need all five steps.

| Instruction | Steps required |    |    |     |    |  |

|-------------|----------------|----|----|-----|----|--|

| beq         | IF             | ID | EX |     |    |  |

| R-type      | IF             | ID | EX |     | WB |  |

| sw          | IF             | ID | EX | MEM |    |  |

| lw          | IF             | ID | EX | MEM | WB |  |

8