## Examples of what to store in pipeline registers

- The following is not an exhaustive list (just a sample)

- The register number where the result will be stored – Known at stage 2; needed at stage 5

- The register number of the data containing the contents of a "store" as well as the contents of that register

Known at stage 2; needed at stage 4

- The immediate value

- Known at stage 2; needed at stage 3

- The updated PC (we'll see why later)

- etc ..

6

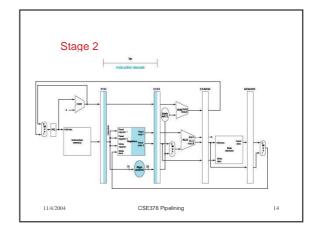

- Stage 2: Instruction decode and register read (same for all instructions)

- We save in ID/EX everything that can be needed in next stages:

The instruction and the incremented PC (from IF(ID) (e.g., function)

- The instruction and the incremented PC (from IF/ID) (e.g., function bits can be needed, the name of the register to be written etc.)

- The contents of registers rs and rt (recall registers A and B)

The sign extended immediate field (for imm. Inst., load/store, branch)

- The sign extended immediate field (for imm. Inst., load/store, brail

Control lines et-ups. We'll deal with control later

- Note that we do not compute the branch target address here (why?).

Resources needed: register file, control unit

13

ID/EX contains PC, instruction, contents of rs and rt, extended imm. Field, control lines set-ups

11/4/2004