### Levels in Processor Design

- Circuit design

- Keywords: transistors, wires etc.Results in gates, flip-flops etc.

- Logical design

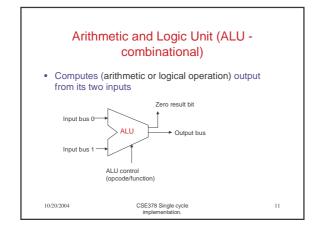

- Putting gates (AND, NAND, ...) and flip-flops together to build basic blocks such as registers, ALU's etc (cf. CSE 370)

- Register transfer

- Describes execution of instructions by showing data flow between the basic blocks

- Processor description (the ISA)

- System description

- Includes memory hierarchy, I/O, multiprocessing etc

CSE378 Single cycle implementation. 10/20/2004

## Register transfer level

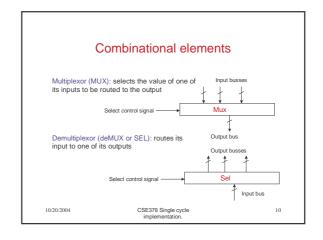

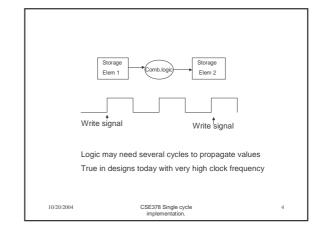

- Two types of components (cf. CSE 370)

- Combinational: the output is a function of the input (e.g., adder)

- Sequential: state is remembered (e.g., register)

10/20/2004 CSE378 Single cycle implementation.

## Synchronous design • Use of a periodic clock edge-triggered clocking determines when signals can be read and when the output of circuits is stable Values in storage elements can be updated only at clock edges Clock tells when events can occur, e.g., when signals sent by control unit are obeyed in the ALU Storage Note: the same storage element can be read/written in the same cycle 10/20/2004 CSE378 Single cycle implementation.

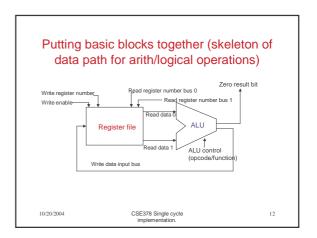

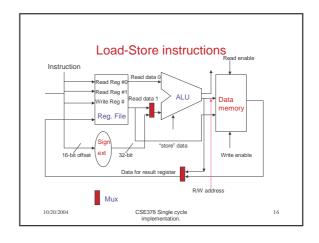

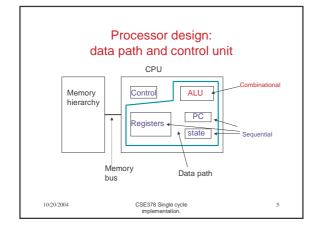

• Data path

10/20/2004

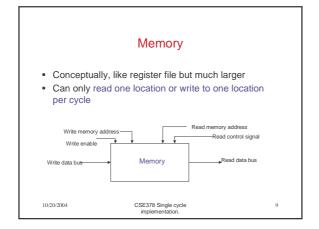

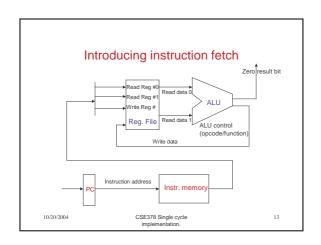

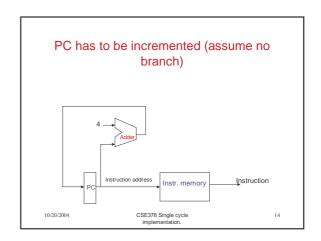

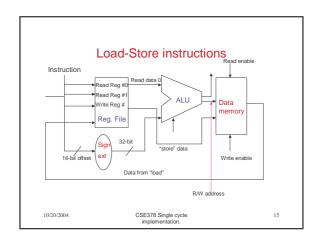

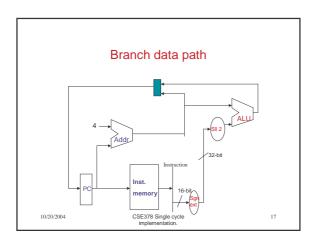

# Processor design - How does data flow between various basic blocks - What operations can be performed when data flows - What can be done in one clock cycle Control unit Sends signals to data path elements Tells what data to move, where to move it, what operations are to be performed · Memory hierarchy Holds program and data CSE378 Single cycle implementation.

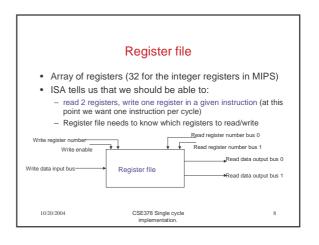

# Data path basic building blocks. Storage elements Basic building block (at the RT level) is a register In our mini-MIPS implementation registers will be 32-bits A register can be read or written Register Write enable signal Output bus CSE376 Single cycle implementation.