#### University of Washington - College of Engineering

Spring 2023 Instructor: Justin Hsia 2023-06-01

# EE/CSE371 QUIZ 5

| Name:                 | <br>_ |

|-----------------------|-------|

| Student ID<br>Number: |       |

## Please do not turn the page until 11:30.

#### **Instructions**

- This quiz contains 4 pages, including this cover page. You may use the backs of the pages for scratch work.

- The quiz is closed book and closed notes, though calculators are allowed.

- Please silence and put away all cell phones and other mobile or noise-making devices.

- Remove all headphones and watches.

- You have 50 (+5) minutes to complete this quiz.

#### Advice

- Read questions carefully before starting. Read *all* questions first and start where you feel the most confident to maximize the use of your time.

- There may be partial credit for incomplete answers; please show your work.

- Relax.

### **Static Timing Analysis** [10 pts]

```

\begin{array}{ll} setup \; slack = DRT_{su} - DAT_{su} \; = min \; clock \; path - max \; data \; path \\ hold \; slack \; = DAT_h - DRT_h \; = min \; data \; path - max \; clock \; path \end{array}

```

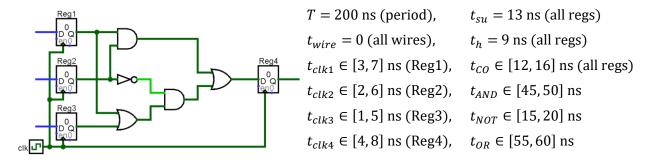

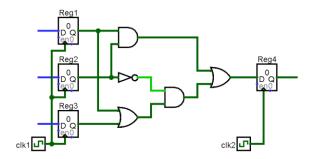

We will analyze the following circuit with the indicated timing constants:

**Solve for the setup slack and hold slack for this circuit** and put your answers in the boxes below. You are allowed to use a calculator on this problem, but no credit will be given without work.

| Setup Slack: | ns |

|--------------|----|

| Hold Slack:  | ns |

## Pipelining [12 pts]

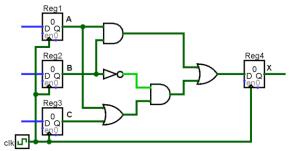

We will look at a simplified version of the same circuit:

$$t_{su} = t_h = t_{wire} = t_{clk} = 0$$

$t_{CO} = 10$  ns (all regs)

$t_{AND} = 50$  ns

$t_{NOT} = 20$  ns

$t_{OR} = 60$  ns

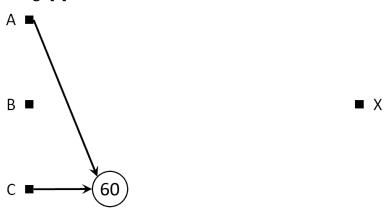

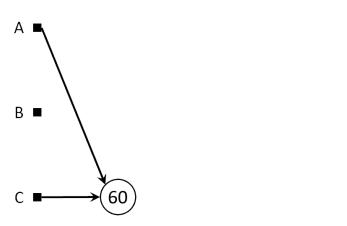

- 1) Complete *both copies* of the Data Flow Graph (DFG) for the circuit by adding nodes labeled with their delays and edges. Note that A, B, C, and X correspond to the labeled nets in the circuit above. One node, corresponding to the lower OR gate, has been provided for you.

- 2) Draw cutsets on your two DFGs to make a 2-stage pipelined and a 3-stage pipelined version of this circuit with *minimal clock period*.

- 3) Assuming we use the minimum clock periods, **compute the latency** for both pipelined versions of this circuit and write them into the boxes below. No credit will be given without work.

■ X

2-stage pipeline:

Latency: ns

3-stage pipeline:

Latency: ns

## **Clock Domain Crossing** [4 pts]

We tweaked the circuit so that Reg4 is now controlled by a separate clock with  $T_1 = 2 \times T_2$  (*i.e.*, clk1 has a longer period):

Predictably, the output of Reg4 is suffering from lots of timing issues. Assuming we cannot change the clocks, **name two changes to this circuit we could do to improve its behavior.** Provide a brief explanation for why each change helps.

|   | Change #1: |

|---|------------|

|   |            |

|   |            |

|   |            |

|   |            |

|   |            |

|   |            |

|   | Change #2: |

|   |            |

|   |            |

|   |            |

|   |            |

|   |            |

| ١ |            |

|   | Change #2: |