# Design of Digital Circuits and Systems Course Wrap-Up

Instructor: Vikram lyer

**Teaching Assistants:**

Ariel Kao Josh Wentzien

Selim Saridede Jared Yoder

**Derek Thorp**

Adapted from material by Justin Hisa

#### **Relevant Course Information**

- Quiz 5 (STA, Pipelining, CDC) today @ 11:30 am

- Scientific calculator allowed!

- Homework 6 (Advanced Testing) due Monday (5/27)

- Monday office hours as scheduled, but remote only

- Lab 6 due the next Monday (6/3)

- Demo, lab report, and video

- You can demo before submitting your report

- Next week's lecture slots will be extra office hours in the lab

- Course eval will be released over the weekend

- Will also post on Ed Discussion with an anonymous Google

Form to give feedback to the TAs

## **Review: Constraints**

#### Reminders:

- A standard constraint expression includes 1+ randomizable variables and at most one comparison operator

- Range: [A:B] means all integers from A to B, inclusive

- Sets: <var> inside {<set>};

- Distribution: <var> dist {<distribution>};

- Given low, mid, high write constraints such that:

- low is 1 half the time, 2 one-third of the time, and 3 onesixth of the time

- mid is evenly distributed between low and high

- high is one of 9, 11, or 13

#### **Review: Constraints**

- Given low, mid, high write constraints such that:

- low is 1 half the time, 2 one-third of the time, and 3 onesixth of the time

- mid is evenly distributed between low and high

- high is one of 9, 11, or 13

- What are the possible values of mid?

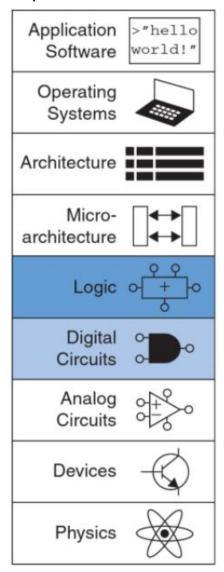

## **Review: Course Motivation**

Harris and Harris. "Digital Design and Computer Architecture" 2<sup>nd</sup> ed.

- More advanced digital logic design

- Higher-level circuit design and analysis techniques

- Interfacing with various devices/peripherals

- How to implement algorithms in hardware

- Practical timing analysis

- "Verilog finishing school"

- This course is the end of the road at UW for gate-level design

- Can start doing FPGA development

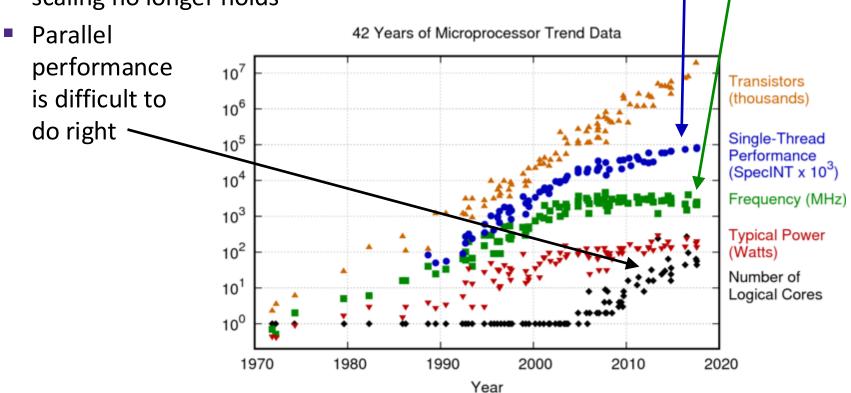

## **Engines of Innovation in Computing**

#### Moore's Law

- Transistor density doubling roughly very 2 years

- Expected trend: more transistors with which to make more complex processors

#### Dennard Scaling

- Smaller transistors should use less power and have shorter delays

- Expected trend: clock frequency should increase as transistors get smaller

#### Parallelism

- Multiple CPUs/cores can work on tasks simultaneously

- Expected trend: more and more cores

# **Engines of Innovation in Computing**

## These trends no longer hold!

Translating transistors into single-threaded performance is hard

Transistors are hitting physical and economic viability limits, so Dennard scaling no longer holds

## **Engines of Innovation**

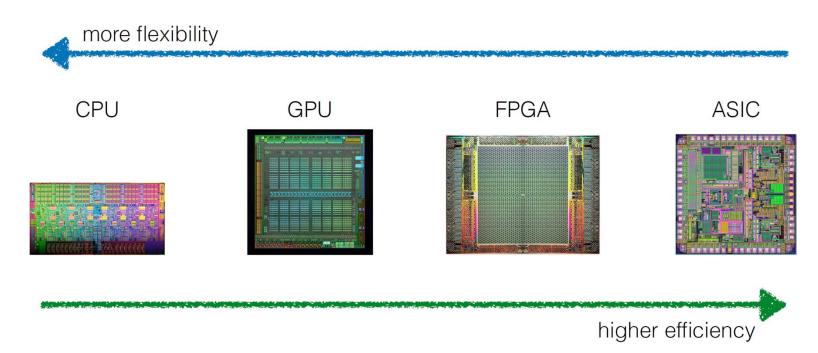

- Specialization: squeeze more work out of those transistors

- Tailor your chip architecture to the characteristics of a stable workload

# **Engines of Innovation**

- Specialization: squeeze more work out of those transistors

- Tailor your chip architecture to the characteristics of a stable workload

EE/CSE371, Spring 2025

## Reliance on Specialization Will Increase

- Compute demand is growing

- Fueled by heavy computations in web search, data science, machine learning, and blockchain technologies

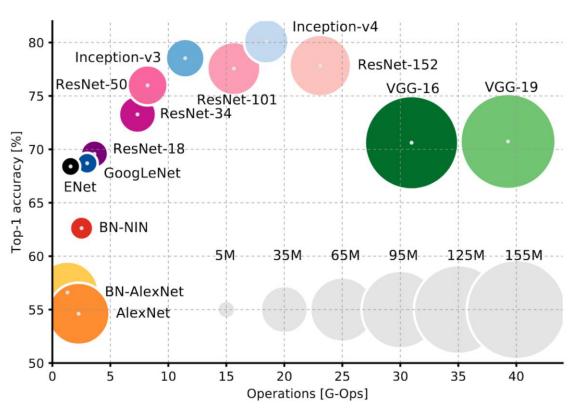

Source: Eugenio Culurciello, An Analysis of Deep Neural Network Models for Practical Applications, arXiv:1605.07678

## Reliance on Specialization Will Increase

We're in a golden age of hardware specialization

## Reliance on Specialization Will Increase

- We're in a golden age of hardware specialization

- Tons of companies are building specialized chips

- https://www.google.com/search?q=fpga+jobs

- https://www.google.com/search?q=verification+engineer+jobs

#### **FPGAs** in the Datacenter

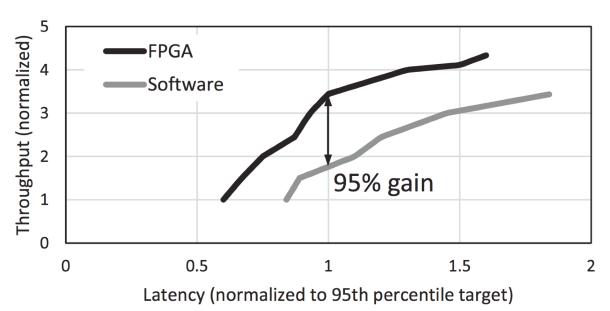

FPGAs have been used in deployment to accelerate

Bing search among other things at Microsoft \*

<sup>\*</sup> Putnam et al., A Reconfigurable Fabric for Accelerating Large-Scale Datacenter Services? [ISCA14]

#### **FPGAs** in the Datacenter

FPGAs have been used in deployment to accelerate Bing search among other things at Microsoft

techcrunch.com

Microsoft launches Project Brainwave, its deep learning acceleration platform – TechCrunch

Frederic Lardinois@fredericl / 1 year agocomment Comment 2 minutes

<u>Microsoft</u> today <u>announced</u> at its <u>Build conference</u> the preview launch of Project Brainwave, its platform for running deep learning models in its Azure cloud and on the edge in real time.

While some of Microsoft's competitors, including Google, are betting on custom chips, Microsoft continues to bet on FPGAs to accelerate its models, and Brainwave is no exception. Microsoft argues that FPGAs give it more flexibility than designing custom chips and that the performance it achieves on standard <a href="Intel Stratix">Intel Stratix</a> FPGAs is at least comparable to that of custom chips.

By highly tailoring the accelerator architecture to the workload (something we cannot do with ASICs without sacrificing generality), they were able to achieve 5x less latency than Google's TPU!

## Research Around FPGAs (at UW)

- Prof. Scott Hauck (ECE)

- "The application of FPGA technology to situations that can make use of their novel features: HPC, reconfigurable subsystems for SoCs, computer architecture education, hyperspectral image compression, and other areas."

- Prof. Rania Hussein (ECE)

- FPGAs for education (LabsLand)

- Prof. David Kohlbrenner (CSE)

- Developing attacks against cloud FPGA security systems

- Prof. Michael Taylor (ECE/CSE)

- BlackParrot: An Agile Open-Source RISC-V Multicore for Accelerator SoCs [FPGAs as testing environment]

## Research Around FPGAs (outside of UW)

- Emerging "MLSys" research area centered around software and hardware systems for deploying modern ML methods

- https://arxiv.org/pdf/1904.03257.pdf

- Look for general Systems keywords like hardware specialization and heterogeneous architectures

- "In heterogeneous architectures, an integrated circuit (ASIC) or a field-programmable gate array (FPGA) is used instead of just one CPU or GPU to perform highly specialized tasks."

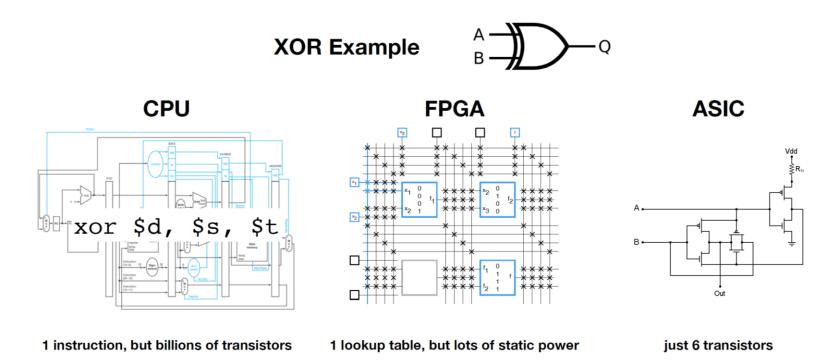

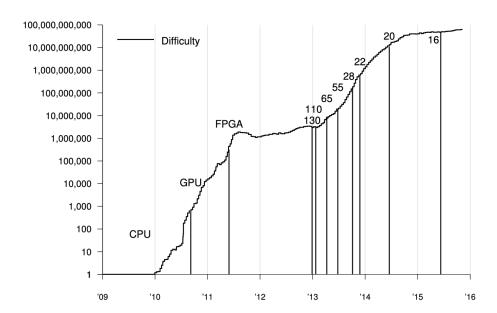

## **ASICs vs FPGAs**

- ASICs are unbeatable in efficiency for specific, highvolume computations

- The reason why mining Bitcoins on CPUs, GPUs, and FPGAs stopped being profitable

- https://www.amazon.com/s?k=bitcoin+miner+asic

Source: Magaki et. al., ASIC Clouds at ISCA 2016

#### **ASICs vs. FPGAs**

#### ASICs

- Huge one-time, up-front cost investment in design and production (mask generation)

- Higher throughput, better energy efficiency and smaller size

- Fully customizable can include any necessary analog components

#### \* FPGAs

- Cost-effective and can be repurposed for ever-changing applications via rapid prototyping

- Worse performance, but still better than CPU good as a "<u>hardware accelerator</u>"

- Reprogrammable, but limited to given components

## Benefits of reprogrammability

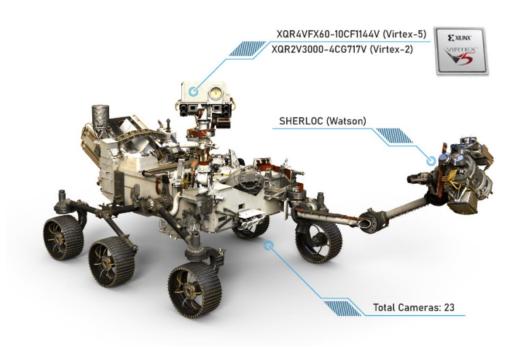

- Useful for inaccessible deployments like space

- Re-programmability

- Low power

- Radiation tolerant

- Security

- Cost efficiency vs ASIC

Figure 1: Perseverance Mars rover

# Benefits of reprogrammability

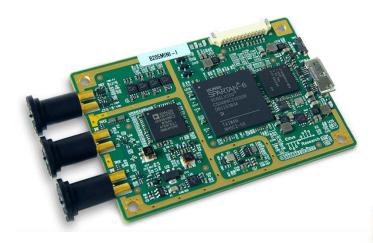

Can create general purpose tools like software defined radios and SmartNICs

# Benefits of reprogrammability

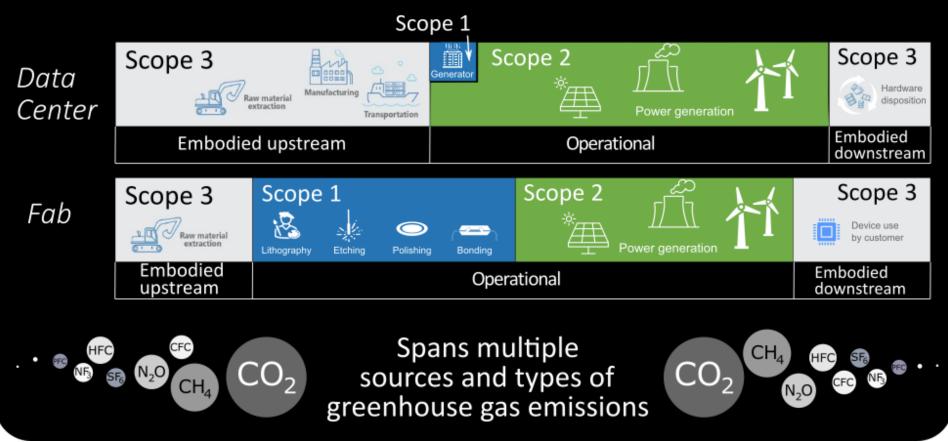

# The Carbon Footprint of Computing

ASICs give maximum efficiency and power reduction, but requires carbon intensive fab, whereas FPGA can be reprogrammed

## Where To Go From Here?

- This course is the end of the road at UW for gate-level design, but still other related areas

- Good building block for embedded systems, digital VLSI, and computer architecture

- Future classes

- Logic Gates: EE 331

- Embedded Systems: EE/CSE 474, EE/CSE 475 (capstone)

- Computer Architecture: EE/CSE 469, EE/CSE 470

- Digital VLSI: EE 476, EE 477, EE 478 (capstone)

# Thanks for a great quarter!

Huge thanks to your awesome TAs!

Thanks to the original course creators:

Hope you had fun this quarter and best of luck in the future!