## Design of Digital Circuits and Systems Static Timing Analysis

#### Instructor: Vikram lyer

#### **Teaching Assistants:**

Ariel Kao Selim Saridede Derek Thorp

Josh Wentzien

Jared Yoder

Adapted from material by Justin Hisa

#### **Relevant Course Information**

- Lab 4 due Friday (5/9)

- Quiz 3 is this Thursday at 11:50 am (30 min)

- ASM and ASMD charts

- Homework 5 (5/16) and Lab 5 (5/23) will be released on Thursday

- Lab 5 is the longest "regular" lab, mostly because of debugging – careful with number representation

- Rest of course material will NOT show up in labs

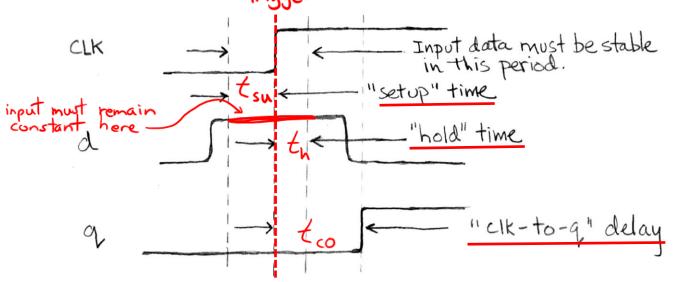

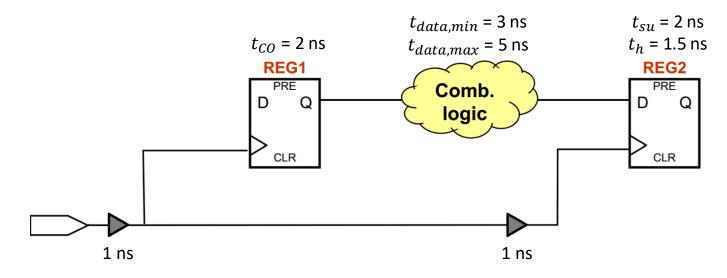

#### **Review: Sequential Timing Constraints**

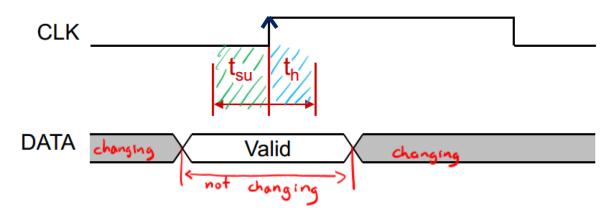

- Setup Time (t<sub>s</sub> or t<sub>su</sub>): how long the input must be stable before the CLK trigger for proper input read

- Hold Time (t<sub>h</sub>): how long the input must be stable after the CLK trigger for proper input read

- \* "CLK-to-Q" Delay ( $t_{C2Q}$  or  $t_{CO}$ ): how long it takes the output to change, measured from the CLK trigger

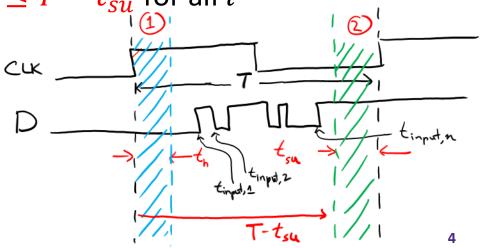

## When Can the Input Change?

- When a register input changes shouldn't violate hold time (t<sub>h</sub>) or setup time (t<sub>su</sub>) constraints within a clock period (T)

- Let t<sub>input,i</sub> be the time it takes for the input of a register to change for the *i*-th time in a single clock cycle, measured from the CLK trigger:

- Then we need  $t_h \leq t_{input,i} \leq T t_{su}$  for all *i*

- Two separate constraints!

- (1)  $\neq_{input,1} \geq \neq_h$

- 2 tinput, n ≤ T tsu

### **Timing Constraint Questions**

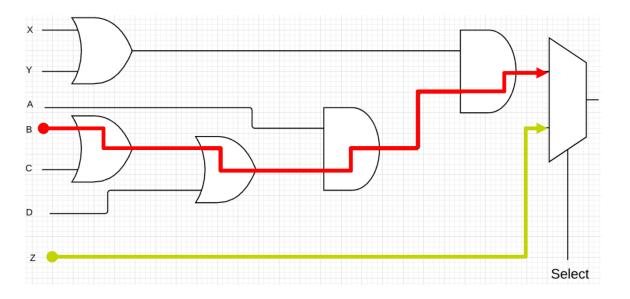

- 1) What are you solving for? Which constraint/inequality is relevant?

- $t_h \rightarrow \text{hold time constraint}$

- $t_{su}$  or  $T \rightarrow$  setup time constraint

- Combinational logic delay → "max" means setup time constraint, "min" means hold time constraint

- 2) Find the most relevant pathway to a register input

- Hold time constraint → shortest pathway

- Setup time constraint → longest pathway

- 3) Solve the inequality for chosen path using the given constants

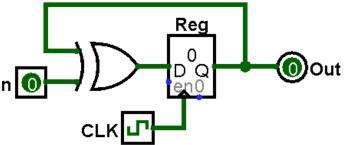

#### **Practice Question**

\* Let T = 300 ps,  $t_{su} = 80 \text{ ps}$ ,  $t_h = 50 \text{ ps}$ ,  $t_{CO} = 100 \text{ ps}$ .

- 1) If In changes exactly on clock triggers, what are the limits on the XOR gate delay that ensure proper behavior?  $t_{XOR} \in (\_\_\_]$  ps

- 2) Now let  $t_{XOR} = 100$  ps and In change a fixed  $t_{in}$  after each clock trigger, what ranges of  $t_{in}$  will result in proper behavior? Answer within a single clock cycle:

$t_{in} \in [0, \_] \cup (\_, 300] \text{ ps}$

#### What Affects Circuit Timing?

- A more realistic picture:

- Logic depth of circuit pathways

- Length, resistance, and capacitance of wire

- Size of the transistors

- Operating conditions: Voltage & Temperature

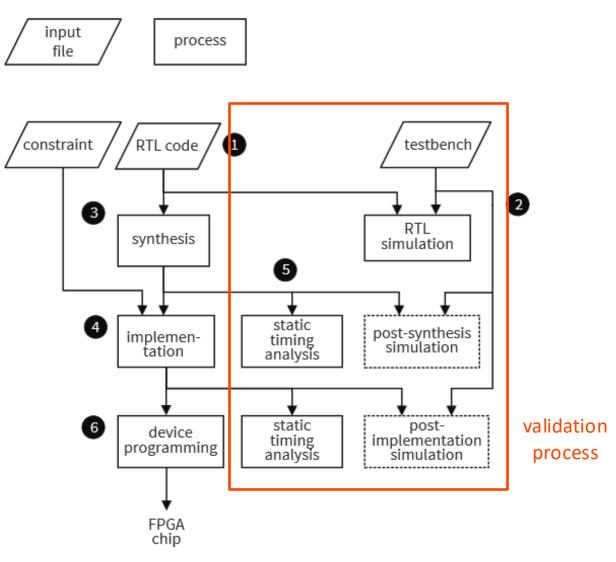

#### **Review: FPGA-Based Design Flow**

Source: Figure 2.3 from "FPGA Prototyping" by P. Chu

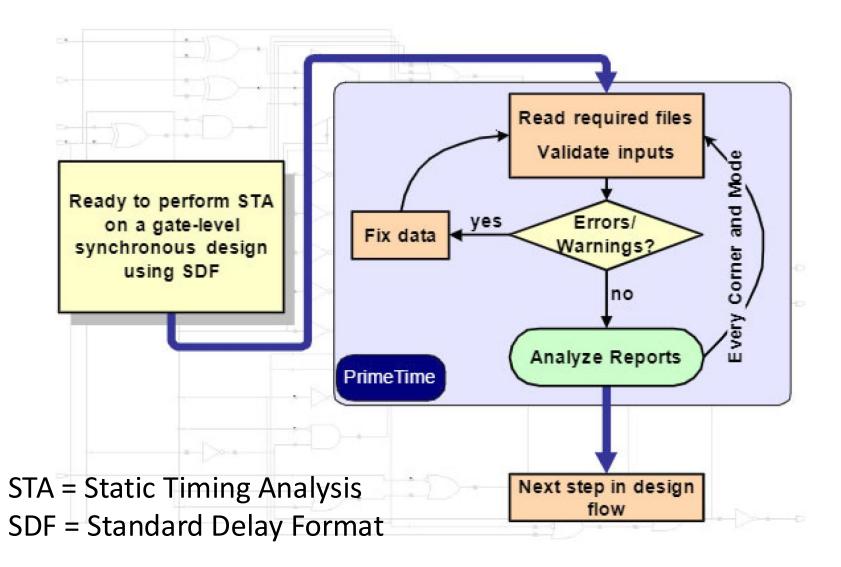

#### **Static Timing Analysis Flow**

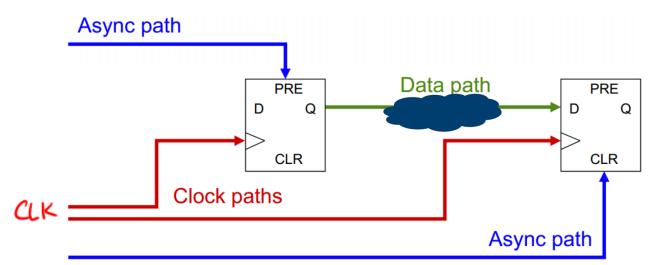

#### **Circuit Path Categorization**

- Data paths are between inputs, sequential elements, and outputs

- Clock paths are from device ports or internally-generated clocks to the clock pins of sequential elements

- Asynchronous paths are between inputs and asynchronous set and clear pins of sequential elements

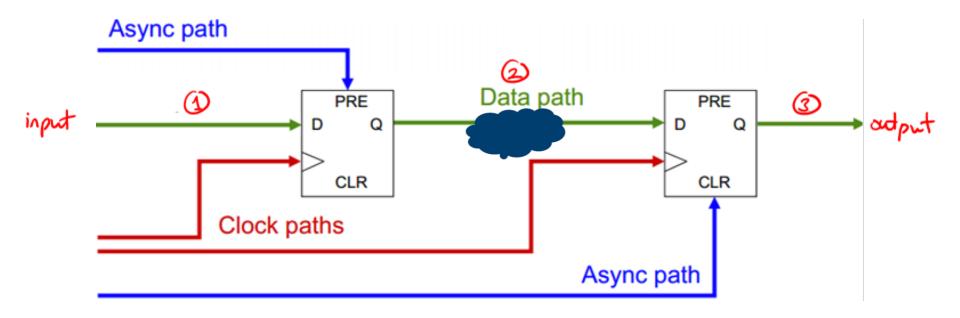

#### **Data Paths**

- Three data path types:

- 1) Input to sequential element

- 2) Sequential element to sequential element

- 3) Sequential element to output

#### **Data Path Validity**

- A data signal is considered valid when is has finished computing and is stable

- Note that this remains true until the next round of computation begins, which can cross clock cycle boundaries

- For proper behavior (*i.e.*, correct reads), the input to a register must remain valid throughout the setup and hold time constraints

#### **Clock Edges**

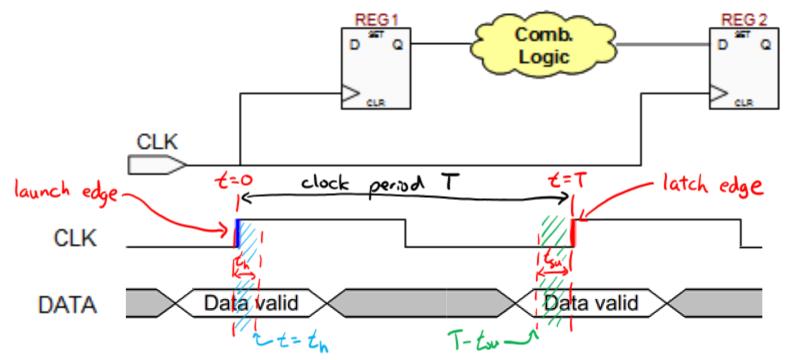

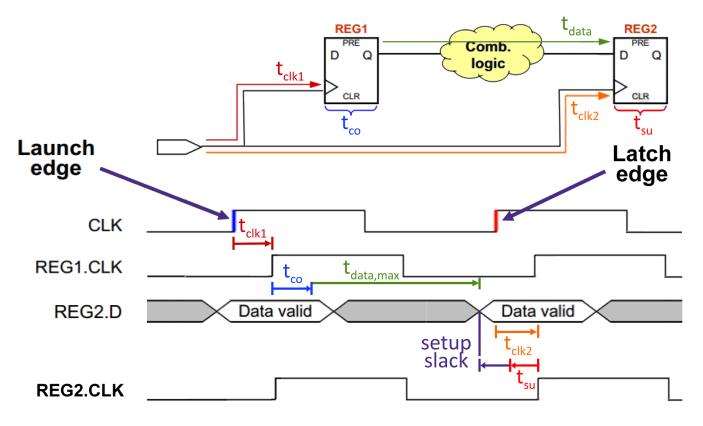

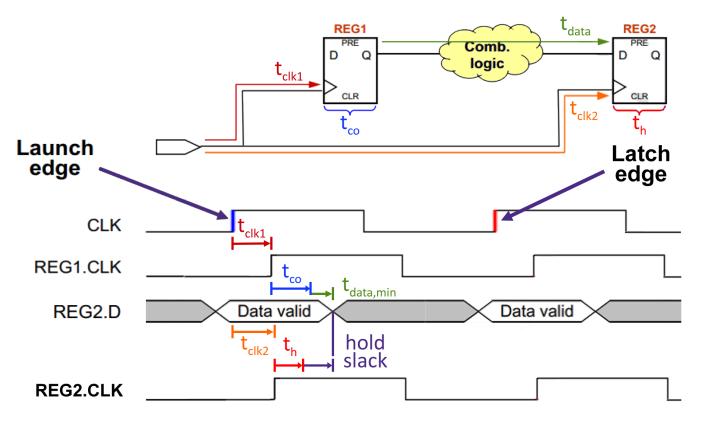

- Looking at a single clock cycle

- Launch Edge: the clock edge that activates or *launches* the source register

- Latch Edge: the clock edge that *latches* the data into the destination register

#### **Timing Delays and Points of Interest**

- \* Clock Network Delay  $(t_{clk})$

- How long it takes for changes in the clock signal to arrive at the register – the cause of *clock skew*

- \* Clock-to-Q or Clock-to-out Delay ( $t_{C2Q}$ ,  $t_{CQ}$ , or  $t_{CO}$ )

- How long it takes the output to change, measured from the register's received clock edge – a property of the FF/register

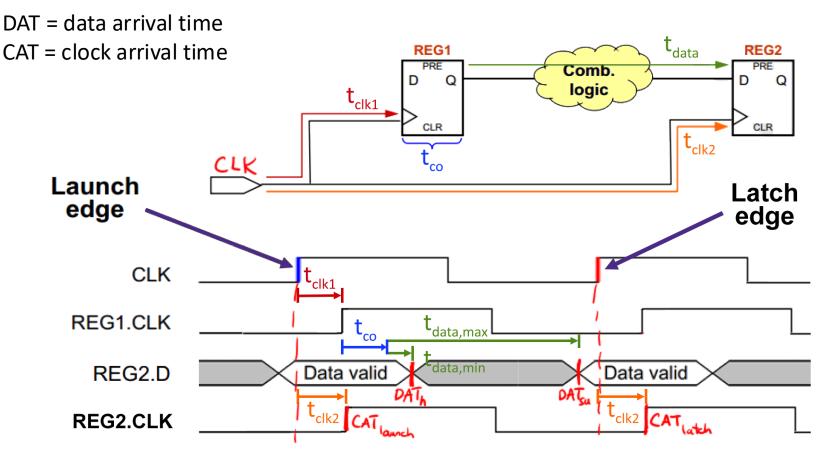

#### Data Arrival Time (DAT)

The time at which the destination register's input is settled

#### Clock Arrival Time (CAT)

The time at which a clock edge arrives at the destination register

#### **Timing Delays and Points of Interest**

DAT<sub>su</sub> = *launch* edge + t<sub>clk1,max</sub> + t<sub>co,max</sub> + t<sub>data,max</sub>

• DAT<sub>h</sub> = *launch* edge +  $t_{clk1,min} + t_{co,min} + t_{data,min}$

•

$$CAT_{latch/launch} = edge + t_{clk2}$$

#### Data Required Time (DRT)

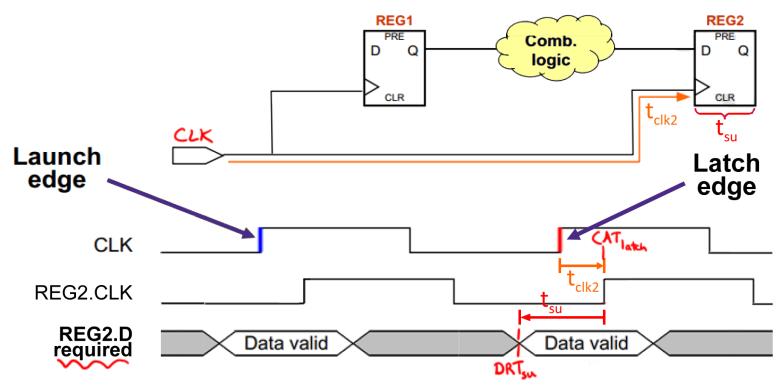

- Data Required Time for Setup (DRT<sub>su</sub>)

- The minimum time required *before* the *latch* edge for data to get latched into the destination register

- Clock Arrival Time<sub>latch</sub> Setup Time

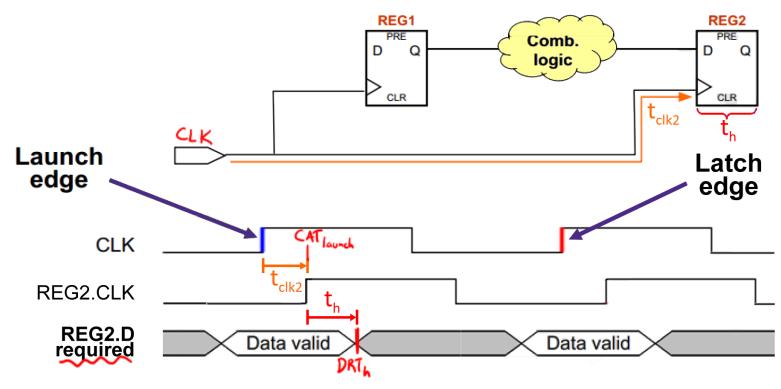

#### Data Required Time (DRT)

- Data Required Time for Hold (DRT<sub>h</sub>)

- The minimum time required *after* the *launch* edge for the data to remain valid for successful latching

- Clock Arrival Time<sub>launch</sub> + Hold Time

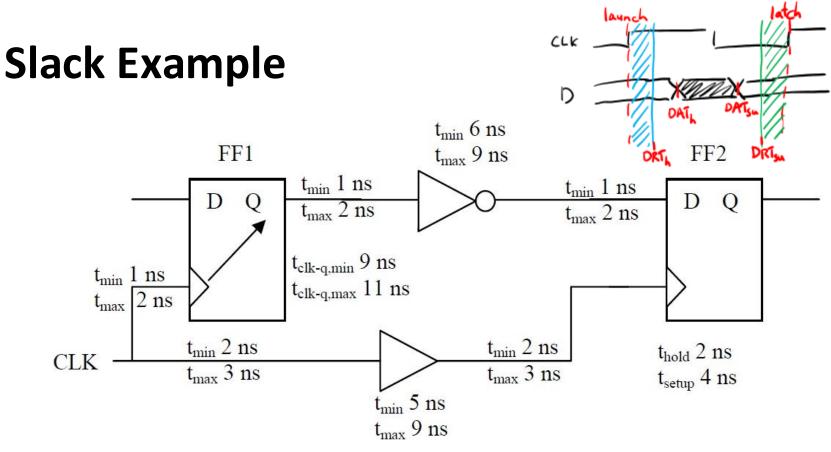

#### **Setup Slack**

- Wiggle room for setup time violations

- Setup slack = DRT<sub>su</sub> DAT<sub>su</sub>

- Depends on clock frequency

#### **Hold Slack**

- Wiggle room for hold time violations

- Hold slack = DAT<sub>h</sub> DRT<sub>h</sub>

- Does not depend on clock frequency

# Technology

## Break

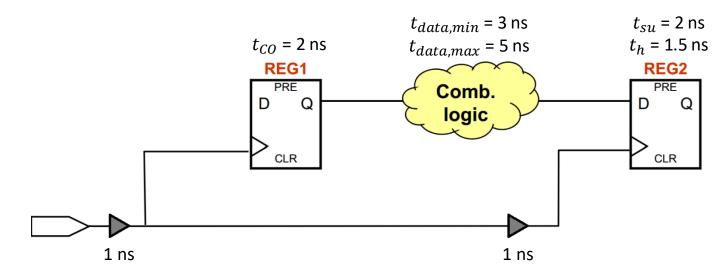

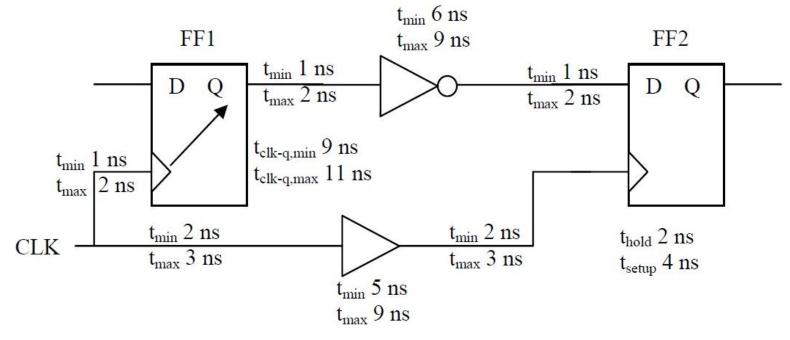

#### **Setup Slack Example**

- Assume 100 MHz clock; clock period T = 10 ns

- Setup slack = DRT<sub>su</sub> DAT<sub>su</sub>

= min clock path max data path

#### **Hold Slack Example**

- Assume 100 MHz clock; clock period T = 10 ns

- Hold slack = DAT<sub>h</sub> DRT<sub>h</sub>

= min data path max clock path

- Calculate the setup and hold slacks:

- Assume 50 MHz clock; clock period T = 20 ns

- setup slack = min clock path max data path

- hold slack = min data path max clock path

#### **Slack Example**

What is the fastest clock we can use with this circuit?

## Synopsys Design Constraints (SDC)

- Synopsys Design Constraints describe timing constraints and exceptions

- Quartus uses . sdc files to define clocks, I/O constraints, and other information that the fitter needs to make the best decisions

- You can make and edit these using the TimeQuestGUI or by editing the . sdc file in a text editor (see hw5)

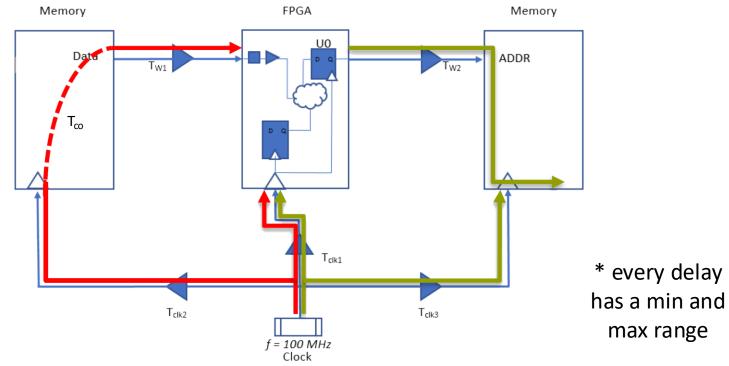

## I/O Constraints

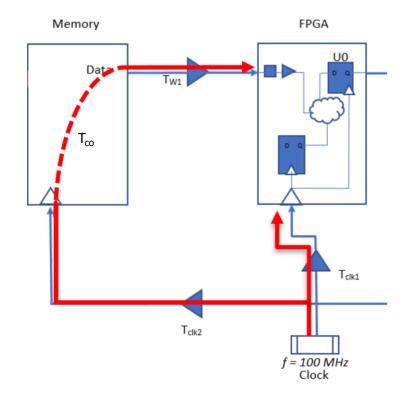

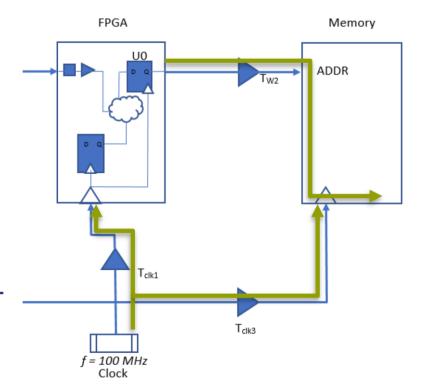

- Let's examine the design constraints for the following example FPGA setup:

- FPGA circuit between two external chips

- T<sub>w</sub> are wire/board delays, T<sub>clk</sub> are clock delays \*

## **Input Delays**

- \* set\_input\_delay

- Command to specify external delays feeding into the FPGA's input ports

- <u>https://www.intel.com/content/</u> <u>www/us/en/programmable/</u> <u>quartushelp/13.0/mergedProjects/</u> <u>tafs/tafs/tcl\_pkg\_sdc\_ver\_1.5\_cmd</u> <u>set\_input\_delay.htm</u>

- Applied to this setup:

- input delay<sub>min</sub> =  $(T_{clk2,min} T_{clk1,max}) + T_{CO,min} + T_{W1,min}$

- input delay<sub>max</sub> =  $(T_{clk2,max} T_{clk1,min}) + T_{CO,max} + T_{W1,max}$

#### **Output Delays**

- \* set\_output\_delay

- Command to specify external delays leaving the FPGA's output ports

- <u>https://www.intel.com/content/</u> <u>www/us/en/programmable/</u> <u>quartushelp/13.0/mergedProjects/</u> <u>tafs/tafs/tcl\_pkg\_sdc\_ver\_1.5\_cmd</u> <u>set\_output\_delay.htm</u>

- Applied to this setup:

- output delay<sub>min</sub> =  $(T_{clk1,min} T_{clk3,max}) + T_{W2,min} T_{h,max}$

- output delay<sub>max</sub> = (T<sub>clk1,max</sub> T<sub>clk3,min</sub>) + T<sub>W2,max</sub> + T<sub>su,max</sub>

## I/O Constraints

#### Check the datasheet!

#### **READ/WRITE CYCLE SWITCHING CHARACTERISTICS** (Over Operating Range)

| Symbol                 | Parameter                        | -166 |      | -133 |      |      |

|------------------------|----------------------------------|------|------|------|------|------|

|                        |                                  | Min. | Max. | Min. | Max. | Unit |

| fmax <sup>(3)</sup>    | Clock Frequency                  | _    | 166  | _    | 133  | MHz  |

| tKC <sup>(3)</sup>     | Cycle Time                       | 6    | _    | 7.5  | _    | ns   |

| tкн                    | Clock High Time                  | 2.4  | _    | 2.8  | _    | ns   |

| tKL <sup>(3)</sup>     | Clock Low Time                   | 2.4  | _    | 2.8  | _    | ns   |

| tKQ <sup>(3)</sup>     | Clock Access Time                | _    | 3.5  | _    | 4    | ns   |

| tkox <sup>(1)</sup>    | Clock High to Output Invalid     | 3    | _    | 3    | _    | ns   |

| tkqlz <sup>(1,2)</sup> | Clock High to Output Low-Z       | 0    | _    | 0    | _    | ns   |

| tkqHZ <sup>(1,2)</sup> | Clock High to Output High-Z      | 1.5  | 3.5  | 1.5  | 3.5  | ns   |

| toeq <sup>(3)</sup>    | Output Enable to Output Valid    | _    | 3.5  | _    | 3.8  | ns   |

| toeqx <sup>(1)</sup>   | Output Disable to Output Invalid | 0    | _    | 0    | _    | ns   |

| toelz <sup>(1,2)</sup> | Output Enable to Output Low-Z    | 0    | _    | 0    | _    | ns   |

| toehz <sup>(1,2)</sup> | Output Disable to Output High-Z  | 2    | 4.5  | 2    | 5    | ns   |

| tas <sup>(3)</sup>     | Address Setup Time               | 2.1  | _    | 2.1  | _    | ns   |

| tss <sup>(3)</sup>     | Address Status Setup Time        | 1.5  | _    | 1.5  | _    | ns   |

| tws <sup>(3)</sup>     | Write Setup Time                 | 1.5  | _    | 1.5  | _    | ns   |

| tces <sup>(3)</sup>    | Chip Enable Setup Time           | 1.5  | _    | 1.5  | _    | ns   |

| tavs <sup>(3)</sup>    | Address Advance Setup Time       | 1.5  | _    | 1.5  | _    | ns   |

| tah <sup>(3)</sup>     | Address Hold Time                | 1.0  | _    | 1.0  | _    | ns   |

| tsн <sup>(3)</sup>     | Address Status Hold Time         | 0.5  | _    | 0.5  | _    | ns   |

| twH <sup>(3)</sup>     | Write Hold Time                  | 0.5  | _    | 0.5  | _    | ns   |

| tceh <sup>(3)</sup>    | Chip Enable Hold Time            | 0.5  | _    | 0.5  | _    | ns   |

| tavh <sup>(3)</sup>    | Address Advance Hold Time        | 0.5  | _    | 0.5  | _    | ns   |

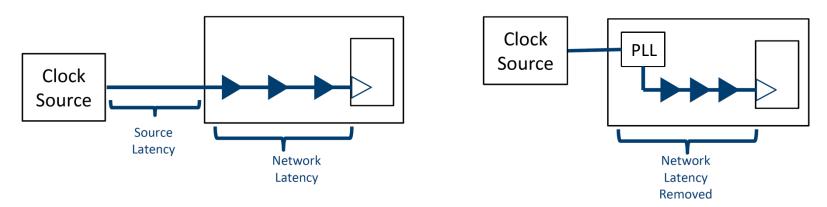

## **Clock Effects**

- Clock Latency: delay for clock signal to reach components

- <u>Source latency</u>: the delay between the clock definition and its source

- <u>Network latency</u>: the delay between the clock definition and register clock pins

- [extra] Often dealt with using an onboard phase-locked loop (PLL) see derive\_pll\_clocks command

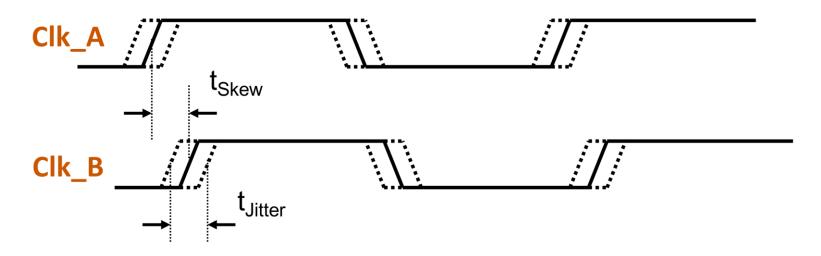

#### **Clock Effects**

- Clock Uncertainty: clock signal does not arrive at every clock pin simultaneously

- <u>Skew</u>: differences in arrival time of a clock signal to different components

- Jitter: deviations from defined period

- Synchronous clock domain crossings (future lecture)

## **Timing Closure**

- Timing constraints need to be met *simultaneously*

- Sometimes fixing one violation will introduce another

- Fixing hold violations: caused by fast data path and destination register's clock latency

- Add delay in the data path with buffers or pairs of inverters (done automatically by Quartus)

- Fixing setup violations: data arrives too late compared to the destination register's clock speed

- Slow down the clock (undesirable)

- Tell fitter to try harder or confine logic to a smaller area

- Rewrite code to simplify logic

- Add *pipelining* (next lecture)