# Design of Digital Circuits and Systems ASM with Datapath III

Instructor: Vikram lyer

**Teaching Assistants:**

Ariel Kao Josh Wentzien

Selim Saridede Jared Yoder

**Derek Thorp**

#### **Relevant Course Information**

- Homework 3 due tomorrow

- Homework 4 released today and due 5/5

- ASMDs and algorithm implementation debugging

- Quiz 2 (ROM, RAM, Reg files) @ 11:50 am

- Lab 3 reports due next Friday (5/2)

- Ideally finish by early next week so you can start Lab 4

- Lab 4 released today and due 5/9

- Implementing bit counting and binary search algorithms

### **ASMD Chart Review Questions**

- Circle all that apply:

- Where can control signals be found?

State boxes

Decision boxes

Conditional output boxes

Where can status signals be found?

State boxes

Decision boxes

Conditional output boxes

Where can external input signals be found?

State boxes

Decision boxes

Conditional output boxes

What is the first thing a path should encounter in an ASM block?

State boxes

Decision boxes

Conditional output boxes

What can be found outside of ASM blocks?

State boxes

Decision boxes

Conditional output boxes

What can RTL operations be attached to?

Control signals

Status signals

External output signals

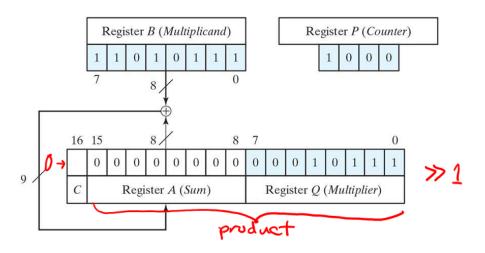

# **Sequential Binary Multiplier Operation**

A few steps of:

11010111

x 00010111

| Operation (completed)  | C | A              | Q                 | P    |              |

|------------------------|---|----------------|-------------------|------|--------------|

| Initialize computation | 0 | ၟၜၟၜၟၜၟၜၟၜၟၜၟၜ | 00010111          | 1000 | 1            |

| Add (GLB = 1)          | O | 11010111       | 00016111          | 0111 |              |

| Shift                  | S | 01101011       | 71000101 <u>0</u> | 0111 | ١.           |

| Add (Q[0]=1)           | 1 | 01000010       |                   | Ollo | <i>)</i> - ( |

| SLiFt                  | 0 | 10100001       | 01000101          | 0110 | ) -1         |

| Add (Q (0)=1)          | 1 | 01111000       | 01000 101         | 0101 |              |

| Shiffs                 | 0 | 210111100      | 00100010          | 0101 |              |

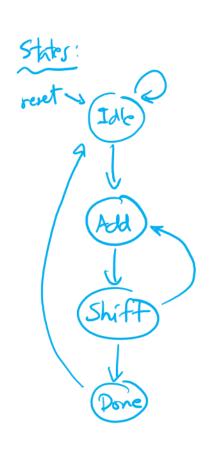

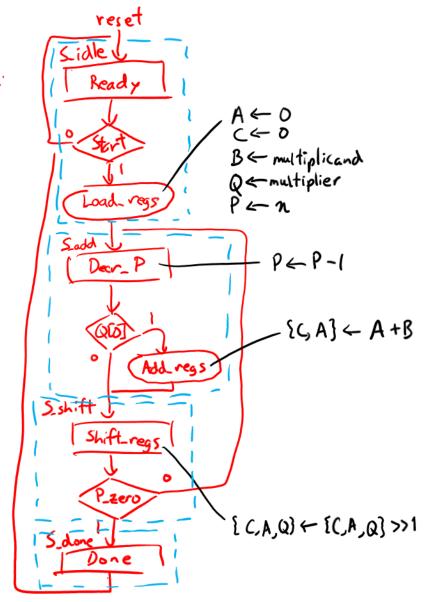

# **Binary Multiplier (ASMD Chart)**

ASMD

#### **ASMD Process Review**

- Identify datapath components, control signals, and status signals from description or pseudocode.

- 2) [optional] Create control-datapath circuit diagram.

- 3) [optional] Create state outline to plan out states and transitions between them.

- 4) Draw out ASM state boxes, decision boxes, and paths between them.

- Augment state boxes with Moore-type outputs and add conditional output boxes with Mealy-type outputs.

- 6) Add ASM blocks to organize states.

- 7) Add RTL operations to control signals.

- 8) Double-check decision box edge cases and timing of operations (i.e., debug).

# Short Tech

# Break

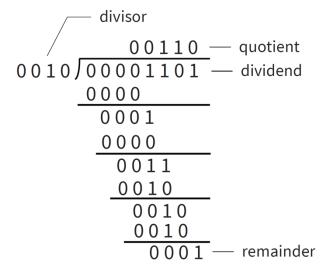

#### **Division Circuit**

Design a circuit that implements the long-division algorithm:

$$\begin{array}{c|c}

& 15 \\

\hline

9 & 140 \\

& 9 \\

\hline

50 \\

\hline

45 \\

5

\end{array}$$

divisor  $\longrightarrow$  1001  $\nearrow$  10001111  $\longrightarrow$  quotient  $\longrightarrow$  dividend  $\bigcirc$  1001  $\bigcirc$  10001  $\bigcirc$  10000  $\bigcirc$  1001  $\bigcirc$  1110  $\bigcirc$  1001  $\bigcirc$  1110  $\bigcirc$  1001

(a) An example using decimal numbers

- Considerations:

- Main operations?

- Stop condition?

(b) Using binary numbers

101

remainder

#### **Division Circuit**

- Design a circuit that implements the long-division algorithm:

- 1) Double the dividend width by appending 0's in front and align the divisor to the leftmost bit of the *extended* dividend.

- 2) If the corresponding dividend bits are ≥ the divisor, subtract the divisor from the dividend bits and make the corresponding quotient bit 1. Otherwise, keep the original dividend bits and make the quotient bit 0.

- Append one additional dividend bit to the previous result and shift the divisor to the right one position.

- 4) Repeat steps 2 and 3 until all dividend bits are used.

#### **Division Circuit**

#### Implementation Notes:

- If current dividend window is smaller than the divisor, skip subtraction

- Instead of shifting divisor to the right, we will shift the dividend (and the quotient) to the left

- We will re-use the lower half of the dividend register to store the quotient

# **Division Circuit Operation**

A few steps of:

$0010 \int \frac{---}{1111}$

| Op (done)  | В    | R    | Q    | q_bit | R_tmp       | R_nxt | Q_nxt | Р   |

|------------|------|------|------|-------|-------------|-------|-------|-----|

| Initialize | 0010 | 0000 | 1111 | Θ     | 0000        | 0001  | 1110  | 100 |

|            |      |      |      |       | 1<br>1<br>1 |       |       |     |

|            |      | <br> | <br> |       | <br>        | <br>  | <br>  |     |

|            |      |      |      |       | 1<br>       |       |       |     |

|            |      | <br> |      |       | <br>        | <br>  |       |     |

|            |      |      |      |       | <br>        |       |       |     |

## **Division Circuit Specification**

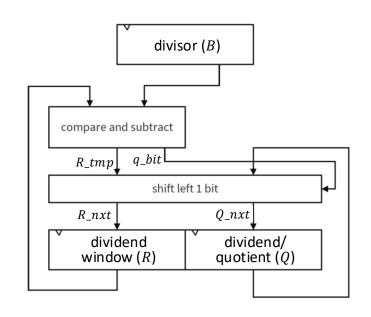

#### Datapath

- 2n-bit register with bits split into n-bit R and n-bit Q

- Divisor stored in register B, dividend stored in Q, R holds 0

- A "compare and subtract" module outputs  $\{R, 0\}$  if R < B and  $\{R B, 1\}$  otherwise  $(\{R\_tmp, q\_bit\})$

- A *shifter* left shifts  $q\_bit$  into  $\{R\_tmp, Q\}$  and outputs to the inputs of R and Q

- A  $\lceil \log_2(n+1) \rceil$ -bit counter P

#### Control

- Inputs Start and Reset, outputs Ready and Done

- Status signals:

- Control signals:

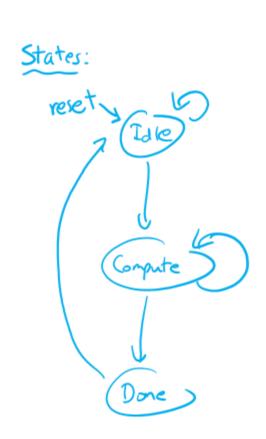

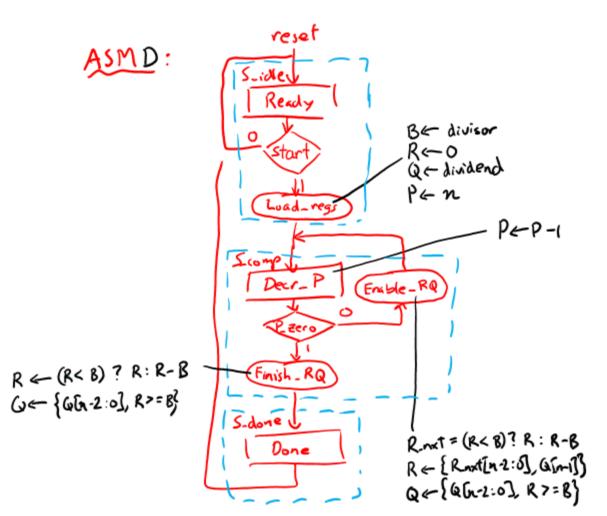

# **Division Circuit (ASMD Chart)**

# **Division Circuit Implementation**

#### Controller Logic

# **Division Circuit (ASMD Chart)**

# **Division Circuit Implementation**

#### Controller Logic

Load\_regs =

$$S_{idle} \cdot S_{tart}$$

$Enable_RQ = S_{comp} \cdot P_{zero}$

$Finish_RQ = S_{comp} \cdot P_{zero}$

$Decr_P = S_{comp}$

$Ready = S_{idle}$

$Done = S_{done}$

# **Division Circuit (SV, Datapath)**

```

module datapath #(parameter WIDTH=4)

(Q, P, divisor, dividend, clk,

Load_regs, Enable_RQ, Enable_R, Decr_P);

// port definitions

output logic [2*WIDTH-1:0] product;

output logic [WIDTH-1:0] Q, P; // note: unnecessary bits for P

input logic [WIDTH-1:0] multiplicand, multiplier;

input logic clk, Load_regs, Shift_regs, Add_regs, Decr_P;

// internal logic

logic [WIDTH-1:0] B, R, R_tmp, R_nxt;

logic q_bit;

endmodule

```

## **Division Circuit (SV, Datapath)**

```

module datapath #(parameter WIDTH=4)

(Q, P, divisor, dividend, clk,

Load_regs, Enable_RQ, Enable_R, Decr_P);

// port definitions & internal logic

// assignments

assign q_bit = (R >= B);

assign R_tmp = (R < B) ? R : R-B;</pre>

assign R_nxt = {R_tmp[WIDTH-2:0], Q[WIDTH-1]};

assign Q_nxt = {Q[WIDTH-2:0], q_bit};

// datapath logic

always_ff @(posedge clk) begin

if (Load_regs) begin

R \le 0; Q \le dividend;

P <= WIDTH; B <= divisor;

end

if (Decr_P)     P <= P - 1;

if (Comp_regs) {R, Q} <= {R_nxt, Q_nxt};</pre>

if (Done_regs) {R, Q} <= {R_tmp, Q_nxt};</pre>

end // always_ff

endmodule

```

#### **Lab 4 Preview: Bit Counter**

- Design a circuit that counts the number of bits in a register A that have the value 1

- Algorithm:

```

B = 0;  // counter

while A != 0 do

if A[0] = 1 then

B = B + 1

endif

A = A >> 1

endwhile

```