## **Remaining Topics**

- Basic State Machine Design Study Problems

- > Study Problems: 8.3, 8.5, 8.6, 8.7, 8.14, 9.2, 9.5,

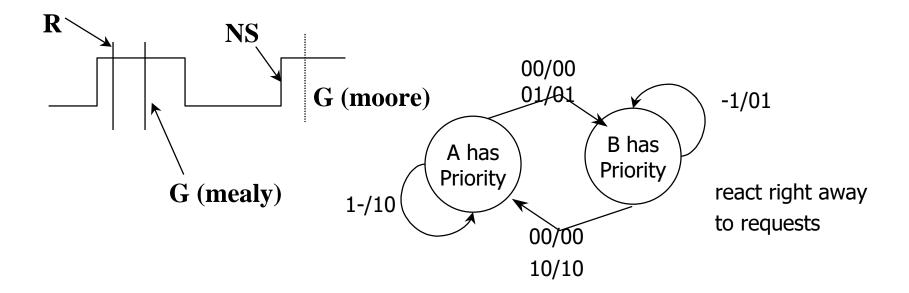

- Moore v. Mealy and Timing Issues

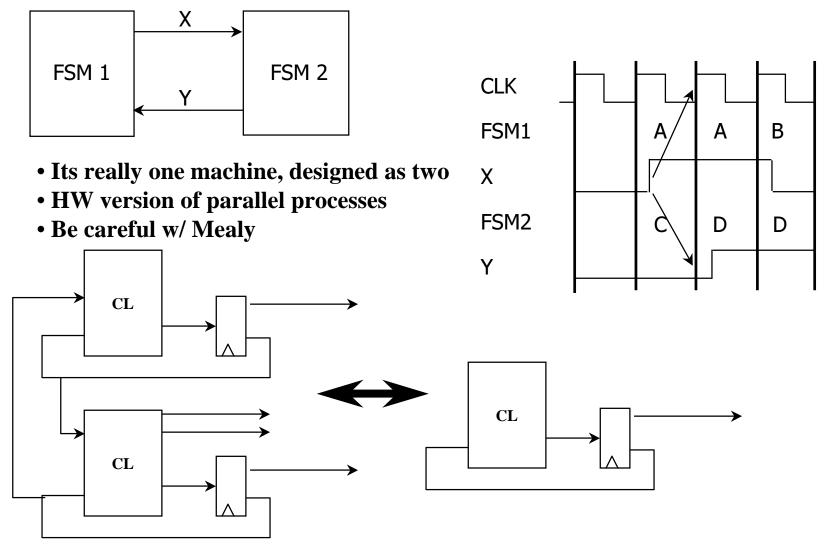

- □ Communicating State Machines

- ☐ State Minimization

- ☐ State Assignment

- State Machines in Verilog

- Datapath and Control Architecture

- ☐ Counter Based Design

- Computer Organization

#### Mealy vs. Moore machines

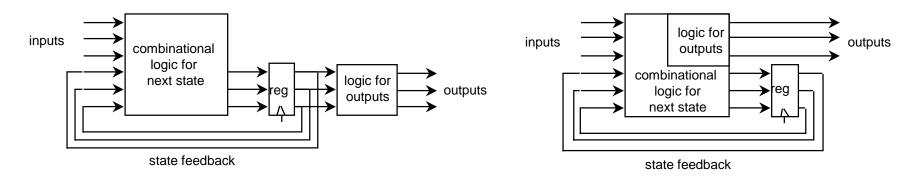

- Moore: outputs depend on current state only

- Mealy: outputs may depend on current state and current inputs

- Our ant brain is a Moore machine

- output does not react immediately to input change

- We could have specified a Mealy FSM

- > outputs have immediate reaction to inputs

- > as inputs change, so does next state, doesn't commit until clocking event

## **Timing Issues**

#### **Mealy Machine with Synchronizers**

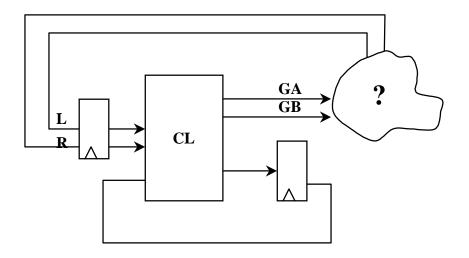

- □Synchronous (or registered) Mealy machine

- ➤ registered state AND outputs

- ➤ avoids 'glitchy' outputs

- ➤ easy to implement in PLDs

- ☐ Moore machine with no output decoding

- >outputs computed on transition to next state rather than after entering

- ➤ view outputs as expanded state vector

#### **Comparison of Mealy and Moore machines**

- Mealy machines tend to have less states

- different outputs on arcs (n^2) rather than states (n)

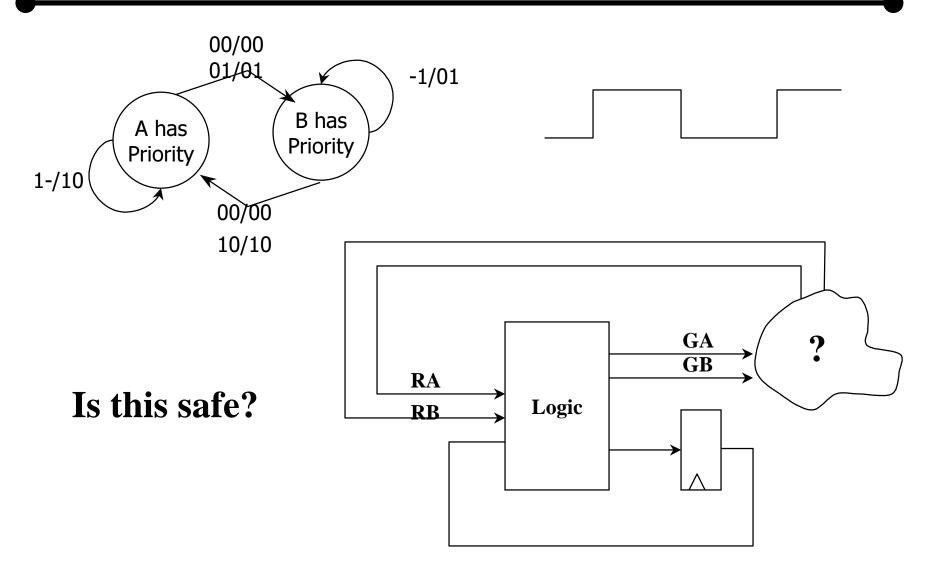

- Moore machines are safer to use

- > outputs change at clock edge (always one cycle later)

- ➤ in Mealy machines, input change can cause output change as soon as logic is done – a big problem when two machines are interconnected – asynchronous feedback

- Mealy machines react faster to inputs

- > react in same cycle don't need to wait for clock

- in Moore machines, more logic may be necessary to decode state into outputs – more gate delays after

## **Communicating State Machines (Decomposition)**

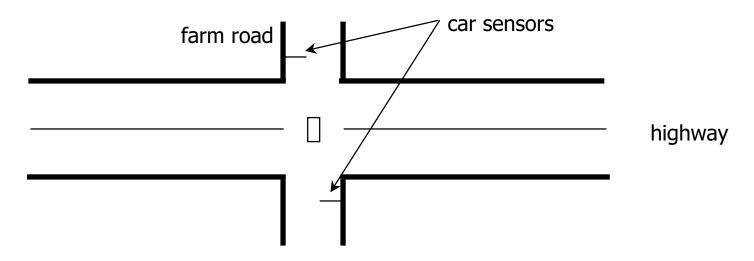

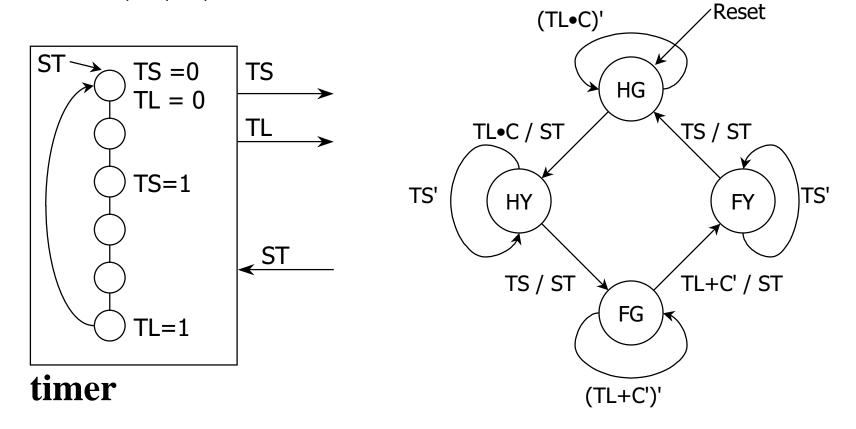

- ☐ Example: A busy highway is intersected by a little used farmroad

- ☐ Detectors C sense the presence of cars waiting on the farmroad

- > with no car on farmroad, light remain green in highway direction

- ➢ if vehicle on farmroad, highway lights go from Green to Yellow to Red, allowing the farmroad lights to become green

- these stay green only as long as a farmroad car is detected but never longer than a set interval

- when these are met, farm lights transition from Green to Yellow to Red, allowing highway to return to green

- even if farmroad vehicles are waiting, highway gets at least a set interval as green

## **Example: traffic light controller (cont')**

☐ Tabulation of inputs and outputs

inputs description

reset place FSM in initial state

C detect vehicle on the farm road

□ <u>outputs</u> <u>description</u>

☐ HG, HY, HR highway lights

☐ FG, FY, FR Farm road lights

☐ Too many states

## **Decomposition (Parallel Processes)**

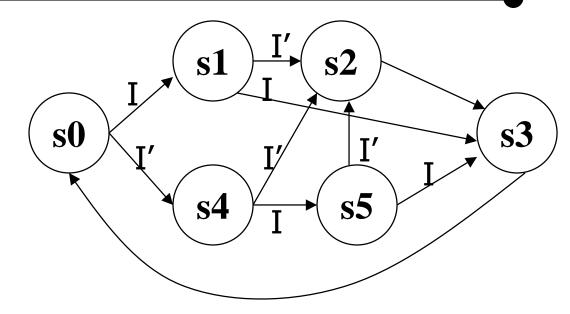

## **Communicating finite state machines**

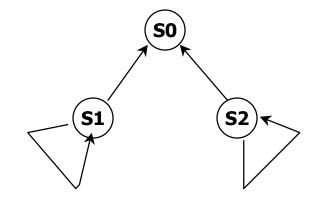

☐ One machine's output is another machine's input

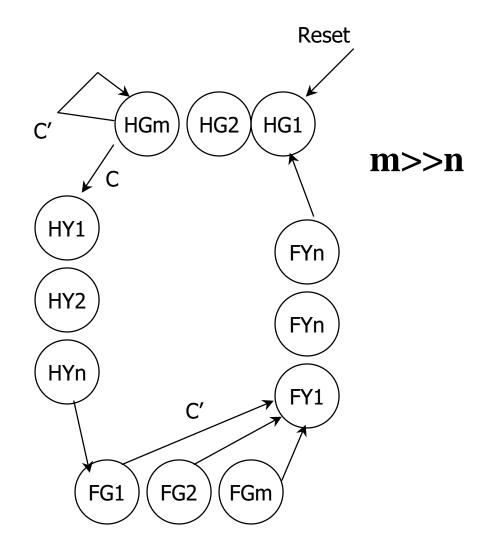

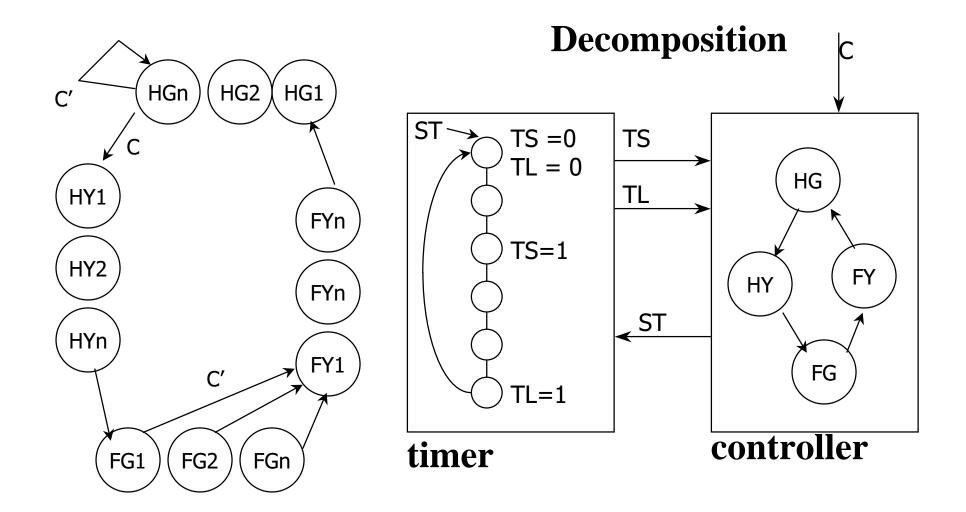

## **Decomposition: traffic light controller**

□ Controller State diagram

States: HG, HY, FG, FY

#### Finite state machine optimization

- ☐ State minimization

- > fewer states require fewer state bits

- fewer bits require fewer logic equations

- ☐ Encodings: state, inputs, outputs

- > state encoding with fewer bits has fewer equations to implement

- however, each may be more complex

- > state encoding with more bits (e.g., one-hot) has simpler equations

- complexity directly related to complexity of state diagram

- input/output encoding may or may not be under designer control

## **FSM Optimization: Traffic Light Controller**

**State Minimization**

State Encoding

**Output Encoding**

output encoding – similar problem to state assignment (Green = 00, Yellow = 01, Red = 10)

|                        | puts                            | Out                | Next State                 | ent State            | Prese              |         | uts         | Inp              |

|------------------------|---------------------------------|--------------------|----------------------------|----------------------|--------------------|---------|-------------|------------------|

| <u>H</u> F             | ST                              |                    |                            |                      |                    | TS      | TL          | C                |

| Red                    | Green                           | 0                  | HG                         | HG                   |                    | -       | _           | 0                |

| Red                    | Green                           | 0                  | HG                         | HG                   |                    | -       | 0           | _                |

| Red                    | Green                           | 1                  | HY                         | HG                   |                    | -       | 1           | 1                |

| Red                    | Yellow                          | 0                  | HY                         | HY                   |                    | 0       | _           | _                |

| Red                    | Yellow                          | 1                  | FG                         | HY                   |                    | 1       | _           | _                |

| Green                  | Red                             | 0                  | FG                         | FG                   |                    | -       | 0           | 1                |

| Green                  | Red                             | 1                  | FY                         | FG                   |                    | _       | _           | 0                |

| Green                  | Red                             | 1                  | FY                         | FG                   |                    | _       | 1           | _                |

| Yellow                 | Red                             | 0                  | FY                         | FY                   |                    | 0       | _           | _                |

| Yellow                 | Red                             | 1                  | HG                         | FY                   |                    | 1       | _           | _                |

|                        |                                 |                    |                            | I                    | I                  |         |             |                  |

| ray code)<br>guential) |                                 | FY = 10<br>FV = 11 | FG = 11<br>FG = 01         | HY = 01              | HG = 00            |         | SA1:        |                  |

|                        | Red<br>Red<br>Red<br>Red<br>Red | 1<br>1<br>0<br>1   | FG<br>FY<br>FY<br>FY<br>HG | FG<br>FG<br>FY<br>FY | HG = 00<br>HG = 00 | 1<br>H( | 1<br>-<br>- | 1<br>0<br>-<br>- |

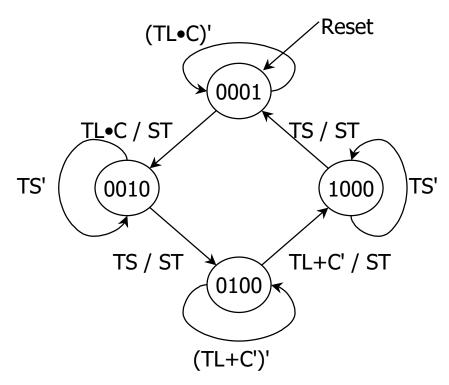

SA3:

HG = 0001

HY = 0010

FG = 0100

FY = 1000

(sequential) (one-hot)

#### **One-hot state assignment**

- □ Simple

- > easy to encode

- > easy to debug

- ☐ Small logic functions

- > each state function requires only predecessor state bits as input

- □ Good for programmable devices

- lots of flip-flops readily available

- > simple functions with small support (signals its dependent upon)

- Impractical for large machines

- > too many states require too many flip-flops

- decompose FSMs into smaller pieces that can be one-hot encoded

- Many slight variations to one-hot

- > one-hot + all-0

## **State Assignment: One Hot**

SA3: HG = 0001

HY = 0010

FG = 0100

FY = 1000

SA3 (One Hot): Read Next State logic from the state diagram!

$$NS3 = C' \cdot PS2 + TL \cdot PS2 + TS' \cdot PS3$$

$$NS2 = TS \bullet PS1 + C \bullet TL' \bullet PS2$$

$$NS1 = C \cdot TL \cdot PS0 + TS' \cdot PS1$$

$$NS0 = C' \cdot PS0 + TL' \cdot PS0 + TS \cdot PS3$$

$$ST = C \bullet TL \bullet PS0 + TS \bullet PS1 + C' \bullet PS2 + TL \bullet PS2 + TS \bullet PS3$$

$H1 = PS3 + PS2$

$H0 = PS1$

$F1 = PS1 + PS0$

$F0 = PS3$

#### **State Assignment: Comparison of Results**

```

☐ SA1 (Gray Code)

NS1 = C \bullet TL' \bullet PS1 \bullet PS0 + TS \bullet PS1' \bullet PS0 + TS \bullet PS1 \bullet PS0' + C' \bullet PS1 \bullet PS0 + TL \bullet PS1 \bullet PS0

NSO = C \cdot TL \cdot PS1' \cdot PSO' + C \cdot TL' \cdot PS1 \cdot PSO + PS1' \cdot PSO

ST = C \bullet TL \bullet PS1' \bullet PS0' + TS \bullet PS1' \bullet PS0 + TS \bullet PS1 \bullet PS0' + C' \bullet PS1 \bullet PS0 + TL \bullet PS1 \bullet PS0

H1 = PS1

H0 = PS1' \cdot PS0

F1 = PS1'

F0 = PS1 \cdot PS0'

□ SA2 (Sequential)

NS1 = C \bullet TL \bullet PS1' + TS' \bullet PS1 + C' \bullet PS1' \bullet PS0

NSO = TS \bullet PS1 \bullet PS0' + PS1' \bullet PS0 + TS' \bullet PS1 \bullet PS0

ST = C \bullet TL \bullet PS1' + C' \bullet PS1' \bullet PS0 + TS \bullet PS1

H1 = PS0

H0 = PS1 \cdot PS0'

F1 = PS0'

F0 = PS1 \cdot PS0

SA3 (One Hot)

NS3 = C' \cdot PS2 + TL \cdot PS2 + TS' \cdot PS3

NS2 = TS \cdot PS1 + C \cdot TL' \cdot PS2

NS1 = C \bullet TL \bullet PS0 + TS' \bullet PS1

NS0 = C' \cdot PSO + TL' \cdot PSO + TS \cdot PS3

ST = C \bullet TL \bullet PSO + TS \bullet PS1 + C' \bullet PS2 + TL \bullet PS2 + TS \bullet PS3

H1 = PS3 + PS2

H0 = PS1

F1 = PS1 + PS0

F0 = PS3

```

## But, if we already had a counter...

#### **State assignment strategies**

- Possible strategies

- sequential just number states as they appear in the state table (Timer)

- > random pick random codes

- one-hot use as many state bits as there are states (Small)

- output use outputs to help encode states (Intersection)

- heuristic rules of thumb that seem to work in most cases (Opcode)

- No guarantee of optimality another intractable problem

## **Heuristics for state assignment**

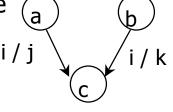

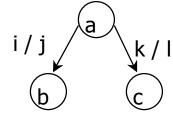

- ☐ 1. Adjacent codes to states that share a common next state

- group 1's in next state map

| Ι | Q | Q <sup>+</sup> | 0 |

|---|---|----------------|---|

| i | а | С              | j |

| i | b | С              | k |

$$c = i * a + i * b$$

- 2. Adjacent codes to states that share a common ancestor state

- group 1's in next state map

- ☐ 3. Adjacent codes to states that have a common output behavior

- > group 1's in output map

#### General approach to heuristic state assignment

- □ All current methods are variants of this

- > 1) determine which states "attract" each other (weighted pairs)

- > 2) generate constraints on codes (which should be in same cube)

- > 3) place codes on Boolean cube so as to maximize constraints satisfied sum (distance\*weighted)

- ☐ Different weights make sense depending on whether we are optimizing for two-level or multi-level forms

- ☐ Can't consider all possible embeddings of state clusters in Boolean cube

- heuristics for ordering embedding

- > to prune search for best embedding

- expand cube (more state bits) to satisfy more constraints -- eventually becomes one-hot

#### **Example**

**Common Next State**

S3: S1, S4, S5

S2: S1, S2, S5

**Common Ancestor**

**S0: S1,S4**

S5: S2,S3

S4: S2,S5

S1: S2,S3

| b2b1b0 | 00 | 01 | 11 | 10 |

|--------|----|----|----|----|

| 0      | ?  | S4 | S5 | S0 |

| 1      | ?  | S1 | S2 | S3 |

Can we satisfy all Constraints? How do I use empty cells?

Symbolically: S2 = I'(S1+S2+S4). If codes for S1,S2,S4 then logic is simpler

$$S1 = I(S0)$$

$$S4 = I'(S0)$$

If codes for S1, S4 are close then logic is simpler

## **Example: Output Encoding**

# If state machine's Ouputs are opcodes

$$s0 = [NEG] + [NOT]$$

$$s1 = [INC] + [DEC] + [PASS] + [NEG] + [NOT]$$

$$s2 = [DEC] + [SUB] + [CMP] + [XNOR]$$

s3 = [OR]

s4 = [ARITHMETIC]

s5 = [SH(L/R)]

s6 = [AND] + [OR] + [SHR]

s7 = [ARITHMETIC]

s8 = [SHL]

s9 = ([ADD] + [DEC])'

| P3P2P1P0 | 00  | 01   | 11  | 10  |

|----------|-----|------|-----|-----|

| 00       | OR  | PASS |     | X   |

| 01       | AND | NOT  | NEG | x   |

| 11       | SHR | XNOR | DEC | ADD |

| 10       | SHL | XOR  | CMP | SUB |

#### State Encoding: Output-based encoding

- ☐ Reuse outputs as state bits use outputs to help distinguish states

- > why create new functions for state bits when output can serve as well

- > fits in nicely with synchronous Mealy implementations

| Inp | uts |    | Present State | Next State | Out | puts (ea | ch row is unique |

|-----|-----|----|---------------|------------|-----|----------|------------------|

| С   | TL  | TS |               |            | ST  | Н        | F                |

| 0   | _   | -  | HG            | HG         | 0   | 00       | 10               |

| _   | 0   | _  | HG            | HG         | 0   | 00       | 10               |

| 1   | 1   | _  | HG            | HY         | 1   | 00       | 10               |

| _   | _   | 0  | HY            | HY         | 0   | 01       | 10               |

| _   | _   | 1  | HY            | FG         | 1   | 01       | 10               |

| 1   | 0   | _  | FG            | FG         | 0   | 10       | 00               |

| 0   | _   | _  | FG            | FY         | 1   | 10       | 00               |

| _   | 1   | _  | FG            | FY         | 1   | 10       | 00               |

| _   | _   | 0  | FY            | FY         | 0   | 10       | 01               |

| _   | _   | 1  | FY            | HG         | 1   | 10       | 01               |

|     |     |    |               |            |     |          |                  |

HG = ST' H1' H0' F1 F0' + ST H1 H0' F1' F0 HY = ST H1' H0' F1 F0' + ST' H1' H0 F1 F0' FG = ST H1' H0 F1 F0' + ST' H1 H0' F1' F0' HY = ST H1 H0' F1' F0' + ST' H1 H0' F1' F0 Output patterns are unique to states, we do not need ANY state bits – implement 5 functions (one for each output) instead of 7 (outputs plus 2 state bits)

#### **Current state assignment approaches**

- ☐ For tight encodings using close to the minimum number of state bits

- best of 10 random seems to be adequate (averages as well as heuristics)

- heuristic approaches are not even close to optimality

- used in custom chip design

- One-hot encoding

- easy for small state machines

- generates small equations with easy to estimate complexity

- > common in FPGAs and other programmable logic

- Output-based encoding

- > ad hoc no tools

- > most common approach taken by human designers

- > yields very small circuits for most FSMs

- ☐ Tools for

- Partitioning (Decomposition)

- State and output Encoding

#### Algorithmic approach to state minimization

- ☐ Goal identify and combine states that have equivalent behavior

- ☐ Equivalent states:

- > same output

- > for all input combinations, states transition to same or equivalent state

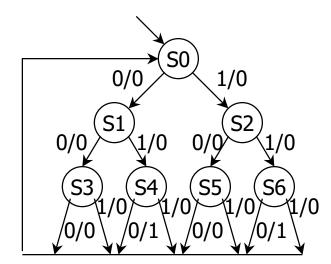

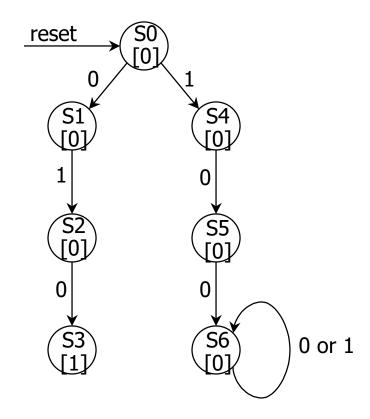

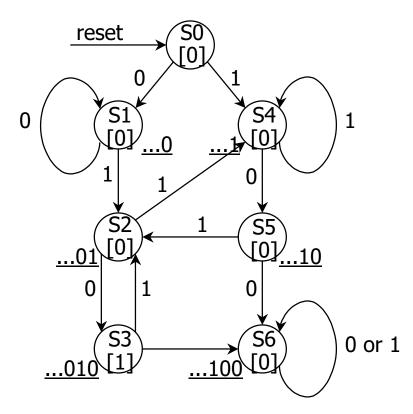

- ☐ Example: Sequence Detector: 010 or 110

## State minimization example: Sequence Detector

- ☐ Goal identify and combine states that have equivalent behavior

- ☐ Equivalent states:

- > same output

- > for all input combinations, states transition to same or equivalent state

- ☐ Sequence detector for 010 or 110

| Input<br>Sequence                       | _                                      |                                        | t State                                |                            | utput                      |

|-----------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|----------------------------|----------------------------|

| Sequence                                | Present State                          | X=0                                    | X=1                                    | X=0                        | X=1                        |

| Reset<br>0<br>1<br>00<br>01<br>10<br>11 | S0<br>S1<br>S2<br>S3<br>S4<br>S5<br>S6 | S1<br>S3<br>S5<br>S0<br>S0<br>S0<br>S0 | S2<br>S4<br>S6<br>S0<br>S0<br>S0<br>S0 | 0<br>0<br>0<br>0<br>1<br>0 | 0<br>0<br>0<br>0<br>0<br>0 |

## **Row Matching Method**

| Input    |                                  | l .                                        | xt State |        | utput |

|----------|----------------------------------|--------------------------------------------|----------|--------|-------|

| Sequence | Present State                    | X=0                                        | X=1      | X=0    | X=1   |

| Reset    | S0                               | S1                                         | S2       | 0      | 0     |

| 0        | S1                               | S1<br>  S3<br>  S5<br>  S0<br>  S0<br>  S0 | S4       | 0      | 0     |

|          | S2                               | S5                                         | S6       | 0      | 0     |

| 00       | S3                               | S0                                         | S0       | 0      | 0     |

| 01       | S4<br>  C5                       | 50                                         | S0       | 1      | 0     |

| 10       | S1<br>S2<br>S3<br>S4<br>S5<br>S6 |                                            | S0       | U<br>1 | U     |

| 11       | 30                               | S0                                         | S0       | T      | U     |

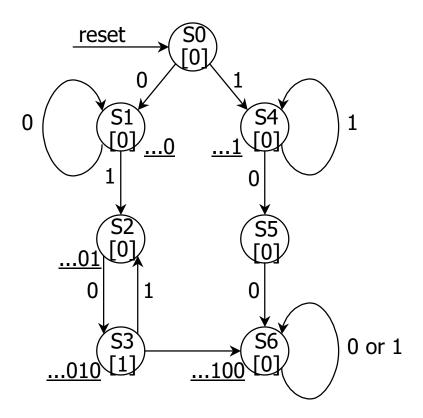

(S0 S1 S2 S3 S4 S5 S6)

S4 is equivalent to S6

(S0 S1 S2 S3 S5) (S4 S6)

S3 is equivalent to S5

(S0 S1 S2) (S3 S5) (S4 S6)

S1 is equivalent to S2

(S0) (S3 S5) (S1 S2) (S4 S6)

#### **Minimized FSM**

☐ State minimized sequence detector for 010 or 110

| Input    |               | Next State  |             | Ou  | tput |

|----------|---------------|-------------|-------------|-----|------|

| Sequence | Present State | X=0         | X=1         | X=0 | X=1  |

| Reset    | S0            | S1'         | <b>S1</b> ' | 0   | 0    |

| 0 + 1    | S1'           | <b>S3</b> ' | <b>S4</b> ' | 0   | 0    |

| X0       | S3'           | S0          | S0          | 0   | 0    |

| X1       | S4'           | S0          | S0          | 1   | 0    |

#### what about this case?

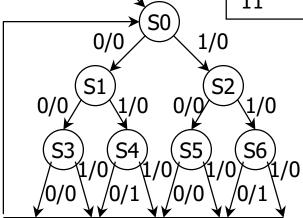

#### More complex state minimization

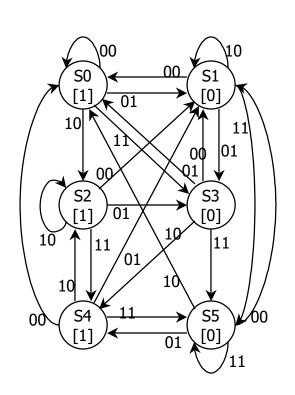

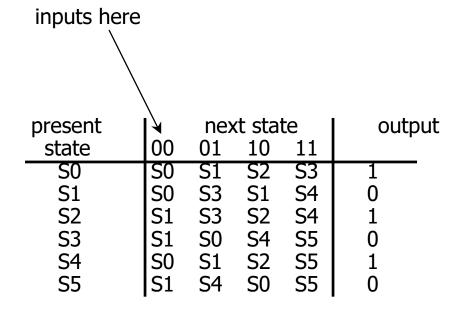

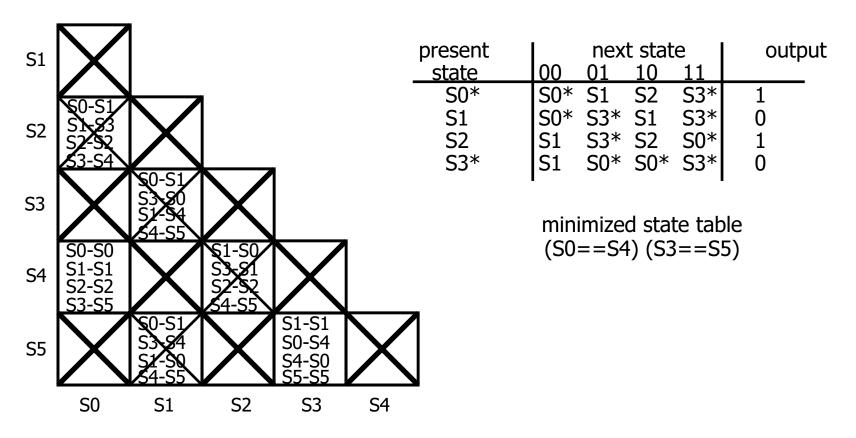

■ Multiple input example

symbolic state transition table

#### **Minimized FSM**

- Implication chart method

- > cross out incompatible states based on outputs

- > then cross out more cells if indexed chart entries are already crossed out

#### Minimizing incompletely specified FSMs

- ☐ Equivalence of states is transitive when machine is fully specified

- ☐ But its not transitive when don't cares are present

e.g., state output S0

$$-0$$

S1 is compatible with both S0 and S2 S1  $1-$  but S0 and S2 are incompatible S2  $-1$

□ No polynomial time algorithm exists for determining best grouping of states into equivalent sets that will yield the smallest number of final states

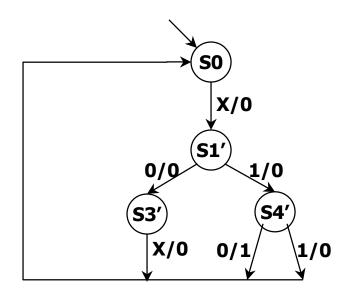

## Minimizing states may not yield best circuit

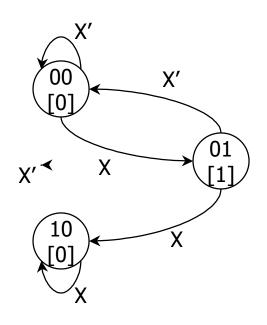

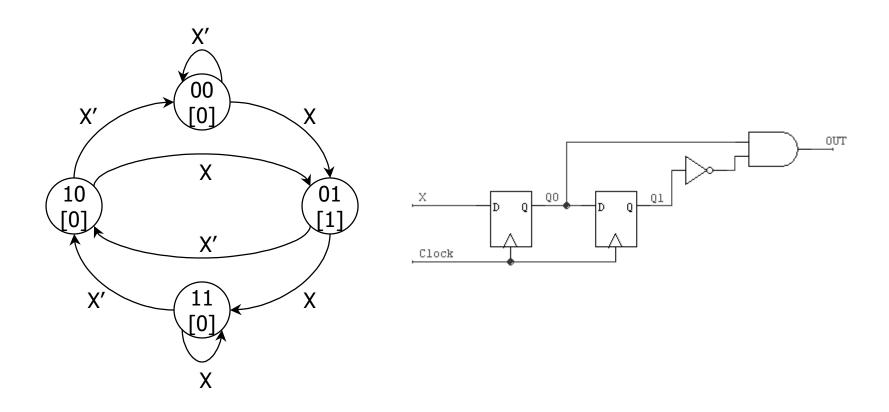

☐ Example: edge detector - outputs 1 when input changes from 0 to 1

| Χ | $Q_1$ | $Q_0$ | $Q_1^+$ | $Q_0^+$ |

|---|-------|-------|---------|---------|

| 0 | 0     | 0     | 0       | 0       |

| 0 | 0     | 1     | 0       | 0       |

| 0 | 1     | 0     | 0       | 0       |

| 1 | 0     | 0     | 0       | 1       |

| 1 | 0     | 1     | 1       | 0       |

| 1 | 1     | 0     | 1       | 0       |

| _ | 1     | 1     | 0       | 0       |

$$Q_1^+ = X (Q_1 xor Q_0)$$

$$Q_0^+ = X Q_1 Q_0$$

## **Another implementation of edge detector**

- ☐ "Ad hoc" solution not minimal but cheap and fast

- ☐ State compression from 4 to 3 states not very helpful

#### Sequential logic implementation summary

- Models for representing sequential circuits

- > abstraction of sequential elements

- finite state machines and their state diagrams

- > inputs/outputs

- Mealy, Moore, and synchronous Mealy machines

- ☐ Finite state machine design procedure

- deriving state diagram

- deriving state transition table

- determining next state and output functions

- implementing combinational logic

- Implementation of sequential logic

- > state minimization

- > state assignment

- support in programmable logic devices

#### **Sequential logic examples**

- ☐ Finite state machine concept

- > FSMs are the decision making logic of digital designs

- > partitioning designs into datapath and control elements

- > when inputs are sampled and outputs asserted

- ☐ Basic design approach: a 4-step design process

- ☐ Implementation examples and case studies

- finite-string pattern recognizer

#### **General FSM design procedure**

- ☐ (1) Determine inputs and outputs

- ☐ (2) Determine possible states of machine

- > state minimization

- ☐ (3) Encode states and outputs into a binary code

- state assignment or state encoding

- output encoding

- possibly input encoding (if under our control)

- ☐ (4) Realize logic to implement functions for states and outputs

- Verilog model for simulation and synthesis

- > -- combinational logic implementation and optimization

- > choices made in steps 2 and 3 can have large effect on resulting logic

#### Finite string pattern recognizer (step 1)

- ☐ Finite string pattern recognizer

- one input (X) and one output (Z)

- > output is asserted whenever the input sequence ...010... has been observed, as long as the sequence 100 has never been seen

- ☐ Step 1: understanding the problem statement

- sample input/output behavior:

```

X: 00101010010...

```

Z: 00010101000...

X: 11011010010...

Z: 00000001000...

## Finite string pattern recognizer (step 2)

- ☐ Step 2: draw state diagram

- > for the strings that must be recognized, i.e., 010 and 100

- > a Moore implementation

#### Finite string pattern recognizer (step 2, cont'd)

- ☐ Exit conditions from state S3: have recognized ...010

- $\rightarrow$  if next input is 0 then have ...0100 = ...100 (state S6)

- $\rightarrow$  if next input is 1 then have ...0101 = ...01 (state S2)

Exit conditions from S1:

recognizes

strings of form ...0 (no 1 seen)

loop back to S1 if input is 0

Exit conditions from S4:

recognizes

strings of form ...1 (no 0 seen)

loop back to S4 if input is 1

#### Finite string pattern recognizer (step 2, cont'd)

- ☐ S2 and S5 still have incomplete transitions

- ➤ S2 = ...01; If next input is 1, then string could be prefix of (01)1(00) S4 handles just this case

- ➤ S5 = ...10; If next input is 1, then string could be prefix of (10)1(0) S2 handles just this case

- ☐ Reuse states as much as possible

- look for same meaning

- state minimization leads to smaller number of bits to represent states

- Once all states have a complete set of transitions we have a final state diagram

## Finite string pattern recognizer (step 3)

□ Verilog description including state assignment (or state encoding)

```

module string (clk, X, rst, Q0, Q1, Q2, Z);

always @(posedge clk) begin

input clk, X, rst;

if rst state = 'S0;

output 00, 01, 02, Z;

else

case (state)

req state[0:2];

'S0: if (X) state = 'S4 else state = 'S1;

'define S0 = [0,0,0]; //reset state

'S1: if (X) state = 'S2 else state = 'S1;

'S2: if (X) state = 'S4 else state = 'S3;

'define S1 = [0,0,1]; //strings ending in

. . . 0

'define S2 = [0,1,0]; //strings ending in ...01

'S3: if (X) state = 'S2 else state = 'S6;

'define S3 = [0,1,1]; //strings ending in ...010

'S4: if (X) state = 'S4 else state = 'S5;

'define S4 = [1,0,0]; //strings ending in

'S5: if (X) state = 'S2 else state = 'S6;

'define S5 = [1,0,1]; //strings ending in ...10

S6: state = S6;

'define S6 = [1,1,0]; //strings ending in ...100

default: begin

$display ("invalid state reached");

assign Q0 = state[0];

state = 3'bxxxi

assign Q1 = state[1];

endcase

assign Q2 = state[2];

assign Z = (state == `S3);

end

endmodule

```

#### Finite string pattern recognizer

- ☐ Review of process

- understanding problem

- write down sample inputs and outputs to understand specification

- derive a state diagram

- write down sequences of states and transitions for sequences to be recognized

- > minimize number of states

- add missing transitions; reuse states as much as possible

- > state assignment or encoding

- encode states with unique patterns

- simulate realization

- verify I/O behavior of your state diagram to ensure it matches specification