# $\mathbf{DesignWorks}^{{}^{\scriptscriptstyle{\mathrm{M}}}} \ \mathbf{for} \ \mathbf{Windows}$

Version 3.1

## Simulator and Associated Tools Reference Manual

September 1994

406 - 960 Quayside Drive New Westminster, B.C., Canada, V3M 6G2 (604) 522-6200

©1994 Capilano Computing Systems Ltd.

| CHAPTER I - INTRODUCTION              | 1  |

|---------------------------------------|----|

| Chapter Organization                  | 1  |

| Notes Regarding Copyright             | 2  |

| CHAPTER II - GETTING STARTED          | 3  |

| Installation                          |    |

| Installing the Simulation Tools       |    |

| Installing the Device Models          |    |

| Memory Usage                          | 4  |

| CHAPTER III - SIMULATION DETAILS      | 5  |

| General Information on Simulation     | 5  |

| Type of Simulation                    |    |

| Simulation Memory Usage               |    |

| Time Units                            |    |

| Signal Simulation Characteristics     | 6  |

| Signal States                         |    |

| Stuck-at Levels                       |    |

| Resolution of Multiple Device Outputs |    |

| Resistive vs. Forcing Drive           |    |

| Probe Tool                            |    |

| Busses                                |    |

| Bus Pins                              |    |

| Device Simulation Characteristics     |    |

| Device and Pin Delay                  |    |

| Device Storage State                  |    |

| Input Signal Values                   |    |

| Setup and Hold Times                  |    |

| Device Pin Types                      |    |

| Device Pin Inversion                  |    |

| Triggers                              | 19 |

| Simulation Clearing and Initialization |  |

|----------------------------------------|--|

| The Clear Simulation Operation         |  |

| The Clear Unknowns Operation           |  |

| Setting Initial Values.                |  |

| 8                                      |  |

### **CHAPTER IV - SCHEMATIC CHANGES TO SUPPORT SIMULATION.25**

| Schematic Simulation Issues              |    |

|------------------------------------------|----|

| Hierarchy Mode                           |    |

| Working With Hierarchical Blocks         |    |

| Power and Ground Connectors              |    |

| Special Signal Names 0 and 1             |    |

| Simulation Models                        |    |

| Primitive Devices on the Schematic       |    |

| Simulation Pseudo-Devices                |    |

| Using External Sub-Circuit Models        |    |

| Probing Signals / Schematic Tool Palette |    |

| Probing a Signal                         |    |

| Probing a Pin                            |    |

| Injecting a Value Using the Probe Tool   |    |

| Schematic Menu Changes                   |    |

| Simulation Menu                          |    |

| Timing Menu                              |    |

| CHAPTER V - THE SIMULATOR TOOL           |    |

| Introduction                             |    |

| Starting the Simulator                   |    |

| Simulator Window                         |    |

| Simulator Window Menu Commands           | 38 |

| Speed Menu                               |    |

| Options Menu                             |    |

| Simulator Procedures                     | 40 |

| Triggers                                 |    |

| Simulation Parameters                    |    |

| Simulation Scope                         |    |

| Stick Signals                            |    |

|                                          |    |

| CHAPTER VI - THE SIMLOAD TOOL           | 53 |

|-----------------------------------------|----|

| Introduction                            | 53 |

| Starting SimLoad                        |    |

|                                         |    |

| The SimLoad Window                      |    |

| SimLoad Window Controls and Fields      |    |

| SimLoad Procedures                      |    |

| Checking Individual External References |    |

| Batch Updating or Reloading Models      |    |

| Creating External Sub-Circuit Models    |    |

| Customizing Delays for Logic Families   |    |

| Model File Naming Conventions           |    |

|                                         |    |

| CHAPTER VII - THE TIMING TOOL           | 61 |

| Introduction                            |    |

| Starting the Timing Tool                |    |

| Timing Window                           | 61 |

|                                         |    |

| Timing Window Menu Commands             |    |

| File Menu                               |    |

| Edit Menu                               |    |

| Timing Menu                             |    |

| Signal Menu                             |    |

| Timing Window Pop-Up Menu               |    |

| Timing Procedures                       |    |

| Repositioning Signals                   |    |

| Displaying Groups                       |    |

| Copying and Pasting                     |    |

| CHAPTER VIII - THE TEST VECTOR TOOL     | 75 |

| CHAPTER VIII- THE TEST VECTOR TOOL      |    |

| Introduction                            |    |

| Starting the Test Vector Tool           |    |

| Test Vector Window                      |    |

| Test Vector Menu Commands               |    |

| iii                                     |    |

| File Menu                          |  |

|------------------------------------|--|

| Edit Menu                          |  |

| Options Menu                       |  |

| Test Vector Procedures             |  |

| Multiple Test Vector Windows       |  |

| Manipulating the Data Spreadsheet  |  |

| Clipboard Operations               |  |

| Test Vector Modes                  |  |

| Hierarchical Designs               |  |

| Interaction With Other Tools       |  |

| Test Vector Commands               |  |

| Row and Column Usage               |  |

| \$Commands                         |  |

| Definition Commands                |  |

| Control Commands                   |  |

| Test Vector Examples               |  |

| Testing a Circuit                  |  |

| Test Vector as a Pattern Generator |  |

##

| Gates and Buffers      |  |

|------------------------|--|

| Gate Definition        |  |

| Gate Pin Order         |  |

| Pin Inversions         |  |

| Transmission Gate      |  |

| Three-State Buffer     |  |

| Resistor               |  |

| Logic Devices          |  |

| Multiplexer            |  |

| Decoder                |  |

| Adder/Incrementer      |  |

| Subtracter/Decrementer |  |

| D Flip-Flop            |  |

| D Latch                |  |

| JK Flip-Flop           |  |

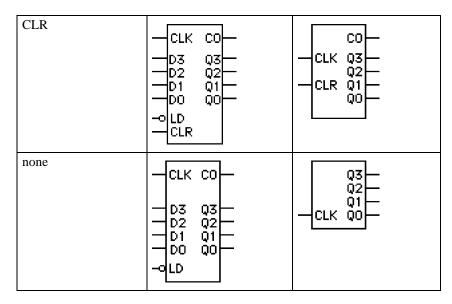

| Register               |  |

| Counter                |  |

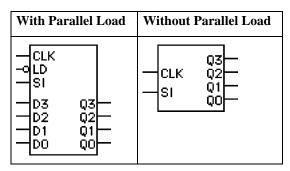

| Shift Register         |  |

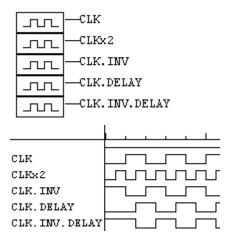

| Clock                  |  |

|                        |  |

| One Shot                                  |     |

|-------------------------------------------|-----|

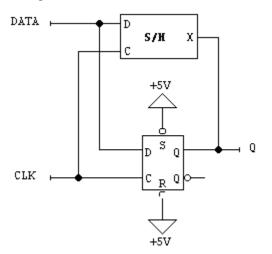

| I/O Simulation Pseudo-Devices             |     |

| Binary Switch                             |     |

| SPST Switch                               |     |

| SPDT Switch                               |     |

| Binary Probe                              |     |

| Hex Keyboard                              |     |

| Hex Display                               |     |

| SetupHold                                 |     |

| Unknown Detector                          |     |

| APPENDIX A - TIMING TEXT DATA FORMAT      | 131 |

| General Description                       |     |

| Specific Description                      |     |

| Header Format                             |     |

| Data Line Format                          |     |

| Timing Text Example                       |     |

| APPENDIX B - SIMULATION ATTRIBUTE FIELDS  | 135 |

| APPENDIX C - DEVICE PIN TYPES             | 141 |

| What Pin Types are Used For               |     |

| Pin Types Table                           | 141 |

| Device Pin Type and Simulator Efficiency  |     |

| Bidirectional Pins                        |     |

| Output Pins                               |     |

| Input Pins                                |     |

| APPENDIX D - PRIMITIVE DEVICE PIN SUMMARY | 147 |

| Pin Inversion                             |     |

| Pin Function Table                        |     |

| CREDITS           |     |

|-------------------|-----|

| TECHNICAL SUPPORT | 154 |

| INDEX             |     |

## **Chapter I - Introduction**

The DesignWorks Digital Simulation package consists of a number of tools that work interactively within the DesignWorks MEDA<sup>TM</sup> Framework:

| Simulator   | is the digital simulation engine and is required for all simulation functions. |  |

|-------------|--------------------------------------------------------------------------------|--|

| SimLoad     | associates internal simulation models with parts as they are used.             |  |

| Timing      | displays timing diagrams.                                                      |  |

| Test Vector | used to enter and run test vectors.                                            |  |

## **Chapter Organization**

| Chapter/Title                                              | Comment                                                                                                                                                                          |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter II - Getting<br>Started                            | Describes installation and initial startup.                                                                                                                                      |

| Chapter III - Simulation<br>Details                        | Describes simulation details including signals, devices, triggers and initialization.                                                                                            |

| Chapter IV - Schematic<br>Changes to Support<br>Simulation | Describes schematic related issues including<br>signal naming, power and ground, simulation<br>models, probing as well as changes to the<br>Schematic tool to support simulation |

| Chapter V - The Simulator<br>Tool                          | Describes control of the simulator via the simulator window.                                                                                                                     |

| Chapter VI - The<br>SimLoad Tool                           | Describes automatic or manual loading of simulation models.                                                                                                                      |

| Chapter VII - The Timing<br>Tool                           | Describes displaying of timing waveforms.                                                                                                                                        |

| Chapter VIII - The Test<br>Vector Tool                     | Describes the creation and execution of test vectors.                                                                                                                            |

| Chapter IX - Primitive<br>Devices                          | Describes information on the simulation characteristics of the primitive device types.                                                                                           |

| Appendix A - Timing<br>Text Data Format                    | Describes the text format used for clipboard operations in the Timing tool.                                                                                                      |

| Appendix B - Simulation<br>Attribute Fields                | Describes the attribute fields used by the various simulation tools.                                                                                                             |

The DesignWorks manual is divided into the following chapters:

| Appendix C - Device Pin<br>Types             | Describes the available pin types and their effect on simulation. |

|----------------------------------------------|-------------------------------------------------------------------|

| Appendix D - Primitive<br>Device Pin Summary | Describes pin orders and options for primitive devices.           |

## **Notes Regarding Copyright**

The DesignWorks Simulator software and manual are copyrighted products. The software license entitles you to use the software on a single machine, with copies being made only for backup purposes, unless a specific license extension has been purchased. Any unauthorized copying of the program or documentation is subject to prosecution.

#### Note regarding trademarks

A number of product trademarks are referred to in this manual. Full credit for these is given in the last section.

## **Chapter II - Getting Started**

This chapter describes installation and initial startup of the DesignWorks Digital Simulator and associated tools.

**NOTE**: Since the DesignWorks package and Microsoft Windows are constantly being upgraded, there may be recent changes and additional information supplied in the release notes with this package. It is important that these notes be reviewed prior to installation as they may contain information that supersedes those given here.

It is assumed that the user is already familiar with general Microsoft Windows operations, such as copying files, creating directories, etc. If not, then please see the Microsoft Windows user's guide.

#### **IMPORTANT:** Make a backup copy

Before proceeding, make a backup copy and a working copy of the DesignWorks disks, then put the originals away for safekeeping.

### Installation

For more detailed information on the files included with the system or directions for installing the current version, see the release notes supplied with the current software version.

#### **Installing the Simulation Tools**

The following table summarizes the code modules making up the DesignWorks Simulator package:

| Tool        | Status   |

|-------------|----------|

| Simulator   | Required |

| SimLoad     | Optional |

| Timing      | Optional |

| Test Vector | Optional |

In order to be loaded when DesignWorks starts up, these tools must be in the same directory as the DesignWorks Schematic Module (not the DesignWorks program directory), or in the directory specified in the TOOLSFOLDER statement in the DesignWorks initialization file, normally "Tools".

By default, the installer will install the program files into the correct location.

#### **Installing the Device Models**

Simulation models for the standard digital library components are supplied in the form of "external sub-circuit models", described elsewhere in this manual. These should normally be located in a directory called Models under the DesignWorks directory.

See the Installation Notes supplied with the package for specific installation instructions.

#### **Memory Usage**

Each tool occupies a certain amount of memory space regardless of whether it is being used or not. If DesignWorks is operating on a system with a minimal amount of memory, it may be desirable to keep unused tools in another directory where they will not be found and loaded by DesignWorks . When they are actually needed, they can be moved temporarily into the Tools directory.

While operating, the Simulator and associated tools can consume large amounts of memory depending upon the size of the design and the amount of data being displayed.

## **Chapter III - Simulation Details**

This chapter describes simulation details including signals, devices, triggers and initialization.

### **General Information on Simulation**

DesignWorks has the ability to perform a realistic simulation of any digital circuit. Obviously, though, any simulation of any system must be limited in detail and must make certain assumptions. In particular, when simulating digital circuits, it must be understood that real circuits are never completely "digital" in nature, and in fact have many "analog" properties which affect how they operate.

DesignWorks is primarily intended to assist with the logical design of a circuit, and does not take into account factors such as line loading, power supply noise, rise and fall times, output drive, etc. As more of these factors are taken into account, the simulation becomes slower and less interactive, which defeats the purpose for which the DesignWorks simulator was created.

#### **Type of Simulation**

DesignWorks performs a discrete simulation of the signal changes in a logic circuit, meaning that signal levels and time change only in steps, rather than continuously. The program does not attempt to analyze your circuit, but simply tracks signal level changes through the devices. Thus, circuits with feeback loops or other delay-dependent features will be simulated correctly as long as they don't rely on particular analog characteristics of devices.

The simulation is "event driven", an event being a change in level of a signal. Each time an event occurs, a list is made of all the devices whose inputs are affected by that event. Any other events occurring at the same time are similarly evaluated, and affected devices added to the list. A type-specific routine is then called for each device on the change list in order to determine what output changes are going to occur. These changes are added to the event list, their time of occurrence depending upon the device delay. No computation is performed for times when no event occurs, so that device delay settings and clock values have no effect on how fast the simulation is performed.

DesignWorks performs strictly a digital simulation. It does not take into account factors such as fan-out (i.e. the number of inputs connected to a given output), line length (capacitance), asymmetrical output drive, etc., except in as much as these affect delay time.

#### **Simulation Memory Usage**

When a circuit is opened or created by DesignWorks, the circuit data is retained completely in the memory of your machine. Since the total memory available is fixed (until you buy your next memory expansion!), this places some limits on circuit size and simulation.

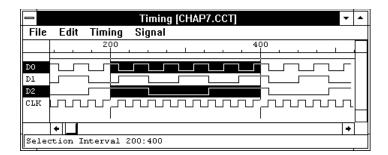

Each time a signal changes state, an "event" record is created in memory. If the signal is not being displayed in the Timing tool, then this record is deallocated again after the signal change has occurred. If the signal is being displayed, then the record is retained in memory until that change has scrolled off the left-hand side of the Timing window. As a result, the memory used by event records will increase when the number of displayed signals is increased, the resolution of the timing display is decreased or the "retain time" setting is increased.

#### **Time Units**

DesignWorks uses 32-bit signed integer arithmetic to calculate all time values used in the simulation. It is usually convenient to think of these values as being in nanoseconds, but the actual interpretation is left up to the user.

The simulation will wrap if any time value approaches the 32-bit integer limit.

## **Signal Simulation Characteristics**

#### **Signal States**

DesignWorks uses thirteen different device output states in order to track conditions within your circuit. These states can be broken into three groups, as follows.

Forcing States (denoted by suffix .F):

LOW.F HIGH.F DONT01.F DONT0Z.F DONT1Z.F CONF.F Resistive States (denoted by suffix .R): LOW.R HIGH.R DONT01.R DONT0Z.R DONT1Z.R CONF.R High Impedance:

HIGHZ

Note that the Forcing/Resistive distinction is used only to resolve conflicts between multiple outputs connected to the same signal. The final value stored or displayed for a given signal line can only be one of five possibilities:

LOW HIGH DONT CONF HIGHZ

#### **Description of States**

The High and Low states are the normal ones expected in a binary circuit, but are not sufficient to realistically simulate circuit operation, so the High Impedance, Don't Know and Conflict states are added. There will always be some cases where the simulation will not correctly mimic what would appear in a real circuit, and some of these cases are discussed below. In particular, if a circuit takes advantage of some analog property of a specific device, such as inputs that float high, known state at power-up, input hysteresis, etc., it will in general not simulate correctly.

#### High Impedance

This state ("Z" on a binary probe) is used for cases when no device output is driving a given signal line. This may occur for an unconnected input, or for a disabled "three-state" or Open-collector" type device. If a device input is in the High Impedance state, it is treated as unknown for the purposes of simulation, even though in a real circuit the device may assume a high or low state, depending on the circuit technology used.

#### Don't Know

The Don't Know state is used in cases where the actual result in a real circuit would depend in the circuit technology used, on random chance, or on analog

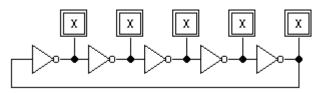

properties of the device not predictable using a strictly digital simulation. For example, if the following ring oscillator circuit is created in DesignWorks, all signals will be permanently unknown, since each depends on the previous one, which is also unknown. In actual hardware, this circuit may oscillate, or may settle into an intermediate logic level, which would not be defined in a digital circuit.

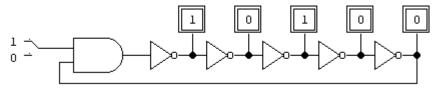

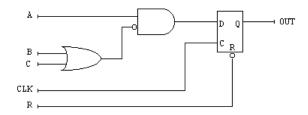

For the purposes of simulation, all circuits must have some provision for initialization to a known state. In most cases, circuits can be initialized using the Clear Unknowns command or by setting the initial value attribute, both described elsewhere in the manual. Alternatively, circuitry can be added to allow a reset to be done, as in the following modification to the ring oscillator:

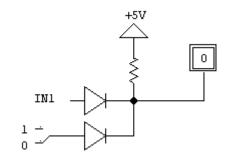

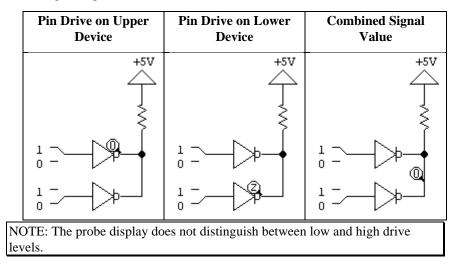

A problem arises in simulating circuits with multiple open collector devices, such as a bus line, illustrated below:

In this circuit the upper device has an unconnected input at IN1 and therefore outputs a "Don't Know" value. The lower device has a low input and therefore outputs a low value. In order to correctly resolve this situation the simulator needs to distinguish between a "Don't Know" output from a normal "totempole" type output and a "Don't Know" from an open collector, open-drain, or other single-drive output. In this case the upper device will produce a DONTOZ output which resolves correctly to a LOW on the output regardless of the state of IN1, using the rules described above.

#### **Conflict**

The "Conflict" state ("C" on a binary probe) results when two device outputs are connected and are of different or unknown state taking into account the rules described above.

#### State Display

The Timing tool displays the various signal states in different colors.

#### Stuck-at Levels

The DesignWorks simulator implements "stuck-at" levels to assist in setting initial simulation states, testing for faults, etc. When a signal is in a "stuck" state, it will not change state, regardless of changes in devices driving the line.

When the stuck status is set, the signal will retain the value it had at the time until some user action forces a change. When the stuck status is removed, the signal will return to the value determined by the devices driving the line.

#### Setting Stuck Levels

A signal can be placed in a Stuck High or Stuck Low state by any of the following means:

- applying the name "0" or "1" to the signal.

- typing "H" or "L" while viewing the signal value with the probe tool.

- using the Stick High or Stick Low control in the Simulators Stick Signals dialog.

• setting a "stuck" option in the Test Vector or other external simulation tool.

Each of these methods is described in more detail in the relevant sections of this manual.

#### **Clearing Stuck Levels**

The stuck status can only be cleared by one of the following user actions:

• typing the spacebar while viewing the signal using the probe tool.

- clearing the "stuck" state using the Simulators Stick Signals.

- clearing the "stuck" state using the Test Vector or other external simulation tool.

#### **Resolution of Multiple Device Outputs**

The DONT0Z and DONT1Z values are used primarily to handle cases of open collector or open emitter devices with unknown inputs (see more information below). Most other types of devices produce the DONT01 output when a value cannot be calculated.

In cases where two or more device outputs are connected together and each one drives the line with a different value, the following rules are used to resolve the actual value on the line.

• the forcing/resistive distinction is only used to resolve outputs from multiple devices. The final value used for display and simulation purposes is one of the forcing values or HIGHZ.

• a forcing drive always overrides a resistive drive or HIGHZ (i.e. the signal takes on the value of the forcing drive, ignoring all resistive drives and HIGHZs).

- a resistive drive always overrides HIGHZ.

- DONT0Z.F and LOW.F produce LOW.

- DONT1Z.F and HIGH.F produce HIGH.

- any other combination of conflicting forcing drives produces CONF.

- DONT0Z.R and LOW.R produce LOW.

- DONT1Z.R and HIGH.R produce HIGH.

- any other combination of conflicting resistive drives produces CONF.

#### **Resistive vs. Forcing Drive**

All primitive devices in DesignWorks output a forcing drive level except for the Resistor primitive device. The function of the Resistor device is to convert a forcing drive on one side into a resistive drive on the other. This can be used to modify the output of any existing device type by placing a resistor in series with it. Note that DesignWorks does not model analog properties of devices, so the resistor does not have a resistance value in the analog sense. In particular, there is no interaction between resistor and capacitor symbols to produce delay in lines. The delay effect can be simulated by setting a delay value for the resistor.

#### **Probe Tool**

The Probe tool is used to interactively examine <u>and</u> change values on individual signals and pins in the circuit schematic. When the probe tip is clicked and held on a signal or pin, the cursor will show the current value on the signal or pin and track changes that occur as the simulation progresses.

See "Probing a Signal" (page 31) in Chapter IV - Schematic Changes to Support Simulation for more information.

#### Busses

Busses (i.e. groups of signals represented by a single line on the schematic) have no particular significance to the simulator. The value of a bus is completely determined by the values of the individual signals it contains. The simulator performs no operations on the bus itself.

NOTE: A bus can be displayed in the Timing window using the Add To Timing command, but this is really equivalent to displaying all the internal signals individually and then grouping them.

#### **Bus Pins**

Bus pins, like busses, have no particular significance to the simulator. The value of a bus is completely determined by the values of the individual pins it contains. The simulator performs no operations on the bus pin itself. Bus pins are not supported on primitive device types.

## **Device Simulation Characteristics**

#### **Device and Pin Delay**

#### Primitive Device Delay

Primitive devices (i.e. those with a program-defined simulation model) have a single delay value which can be set to any integer value from 0 to 32767. This delay is applied when any input change causes any output change. In addition, a pin delay in the range 0 to 32767 can be set on any input or output pin. Pin delays can be used to set arbitrary path delays through the device. See more information on pin delays below.

The initial delay value is set to 1 when the device is created, but this can be changed later using the Parameters command in the Options menu in the Simulator window. This delay applies whenever any input change causes an output change. There is no provision in the built-in simulation models for different delay values on low-to-high and high-to-low transitions. The Clock and I/O devices have no delay characteristic.

See "Working With Hierarchical Blocks" (page 25) in Chapter IV - Schematic Changes to Support Simulation for more information on settings of delays in hierarchical designs.

#### Sub-Circuit Device Delay

Sub-circuit devices inherit their delay characteristics from their internal circuit and have no "device delay" characteristic of their own. Simulation Parameters cannot be directly used on a sub-circuit device, although pin delays <u>can</u> be set separately on each instance of a sub-circuit device to customize path delays.

#### Pin Delays

Any input or output pin on any device (including port connectors and subcircuit devices) can have a pin delay associated with it. Pin delays normally default to 0 time units, but can be in the range 0 to 32767.

A pin delay acts like a "buffer" device with the given delay inserted in line with the pin. On an input pin, the device simulation model will not see a change in signal value until after the pin delay has elapsed. On an output pin, the pin delay is added to the overall device delay for any changes scheduled on that pin.

#### Effect of zero delay

A delay value of zero is permitted in a DesignWorks device, but this setting should be used only with an understanding of how the simulation is implemented as it can result in unexpected side-effects.

On a given pass through the simulation routine, all the events on the list which occur at the current time are scanned and then the new outputs for all affected devices are calculated. If any of these devices has a zero delay setting then this will result in more changes being placed on the event list at the current time. However, all these changes emerging from zero-delay devices will not be evaluated until the next pass through the simulator. This is done to allow for user interaction with the simulation.

Stepping interactively through a circuit with zero-delay elements results in all these value changes to be updated on the screen, even though "simulation time does not advance. If a signal changes value then reverts to its original state within the same time step, this will be displayed as a zero-width spike in the timing window.

If a zero-delay feedback loop exists in a circuit, the signal changes will be simulated and any probes on the schematic will be updated at each pass through the simulator. However the events at the head of the list will always have the same time value associated with them and the simulated time will never advance. Updating of the timing window will stop until some delay is inserted into the loop.

#### Where Delays are Stored

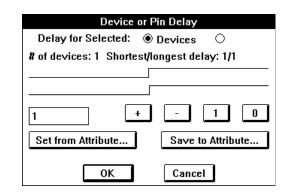

Delays are stored as decimal integers in text form in attribute fields associated with each device or pin. For devices, the delay field is called "Delay.Dev", for pins it is "Delay.Pin" An empty or invalid string will be interpreted as the default value, usually 1 for devices and 0 for pins.

Some special-purpose devices, such as the Clock, One Shot and SetupHold primitive devices take two delay characteristics. In this case, two integers separated by a comma should appear in the Delay.Dev field.

Note: The Simulation Parameters dialog should be used to control these attribute fields rather than the Schematic tools attribute dialog.

See each of these primitive types in Chapter IX - Primitive Devices (page 107) for more information.

A number of additional fields are pre-defined in DesignWorks for storage of alternate delay values. These fields <u>are not</u> used directly by the simulator, but are only provided as a convenient place to store these values. The Save to Attribute and Set from Attribute functions in the Simulation Parameters dialog can be used to copy values to or from alternate delay fields.

The following alternate fields are pre-defined.

| Field Name    | Function                 |

|---------------|--------------------------|

| Delay.Dev.Typ | Typical device/pin delay |

| Delay.Pin.Typ |                          |

| Delay.Dev.Min | Minimum device/pin delay |

| Delay.Pin.Min |                          |

| Delay.Dev.Max | Maximum device/pin delay |

|---------------|--------------------------|

| Delay.Pin.Max |                          |

#### **Device Storage State**

In DesignWorks, primitive storage devices (e.g. flip-flops, counters and registers) do not store their current state internally. The device state is completely determined by the values on the signals attached to the output pins. Thus, the following factors will affect the operation of these devices:

- Conflicting or overriding values on the output signals (e.g. a stuck state) will override the last device state calculated by the model.

- Device and pin delays will influence the calculation of a new device state. E.g. if the period of a clock applied to a counter is less than the total delay through it, an erroneous count sequence will result.

If desired, this behavior can be modified by placing the primitive devices in a sub-circuit device and setting appropriate pin types and delays on the parent device to "buffer" the outputs.

NOTE: These comments do not apply to RAM or bidirectional switch primitives, both of which store internal state information independent of the values of the attached signals.

See "Working With Hierarchical Blocks" (page 25) in Chapter IV - Schematic Changes to Support Simulation for more information.

#### **Input Signal Values**

Unless an alternate input value mapping is specified (see below), for all device types except switches, signal values "High-impedance" and "Conflict" are treated as "Don't Know" when applied to a device input. When a device is first created, all input signals take the "High Impedance" state and outputs are set depending on their type, normally to the "Don't Know" state. Thus, an unused input pin will appear as an unknown input to a device, which may affect its output level.

As with real circuits, all unused inputs should be connected to a high or low level as appropriate. This can be done by naming the pin signal either "0" or "1", using a power or ground symbol, or by using a pullup resistor to set a high level.

Note: "0" and "1" only work for simulation and are NOT equivalent to power and ground for netlist purposes.

#### Input Value Mapping

An alternate input value can be specified for a design by placing a speciallyformatted string in the Sim.InputMap attribute field for the design. This is intended primarily to model specific logic families that have a known response to high-impedance inputs. The mapping applies only to primitive devices and is global to the design that it is specified in. Note that this mapping <u>does not</u> occur at inputs to sub-circuit devices but <u>does</u> affect the primitives that they contain.

See Appendix B - Simulation Attribute Fields (page 135) for more information on the format of the Sim.InputMap field.

#### **Setup and Hold Times**

All standard device types having an edge-triggered clock, such as the D and JKflip-flops, register and shift register, have an effective setup time of 1 unit and a hold time of zero units. That is, if the data and clock inputs change simultaneously, the old value of the data input will be used.

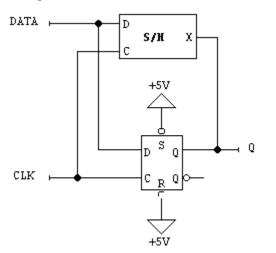

Setup and hold times can be checked by attaching a "SetupHold" primitive device to the inputs of the clocked device to be checked, as follows:

The SetupHold device puts out a highZ value until a setup or hold violation occurs when it switches to a "Don't Know" state. Thus, the output of the SetupHold device can be paralleled with the flip-flop so that the output line will enter a conflict state when an error occurs.

### **Chapter III**

See Chapter IX - Primitive Devices (page 107) for more information on the SetupHold device.

#### **Device Pin Types**

Every device pin has a characteristic known as its *pin type*, e.g. input or output. The pin type is set when the part entry in the library is created and cannot be changed for individual device pins on the schematic. Correct pin type settings are crucial to correct and efficient operation of the simulator.

The pin type is used by the simulator to determine the direction of signal flow and which output values are allowable on a given output pin.

See Appendix C - Device Pin Types (page 141) for more information on the available pin types and how they affect the simulation.

See Chapter X - Device Symbol Editing in the DesignWorks/Schematic Reference Manual for procedures on setting pin types when creating a symbol.

#### **Device Pin Inversion**

The logic of any pin on any device can be inverted by placing a non-empty value in the Invert.Pin attribute field of the pin. When this is done any value passing into or out from that pin will be inverted. This applies to primitive types as well as sub-circuit devices. The following table summarizes the level mappings that occur.

| External Signal Value | Internal Signal Value |

|-----------------------|-----------------------|

| LOW.H                 | HIGH.H                |

| LOW.L                 | HIGH.L                |

| HIGH.H                | LOW.H                 |

| HIGH.L                | LOW.L                 |

| All others            | Unchanged             |

#### NOTES:

1) The logical inversion of the pin is <u>completely independent</u> of the graphical representation of the pin. I.e. using the "inverted pin" graphic in the DevEditor tool <u>does not</u> invert the pin logic in the simulator. The Invert.Pin field must be set to have this effect.

2) Although pin inversion can be specified independently for each device on the schematic we do not recommend modifying these settings after a device has been placed on the schematic. This can create the confusing situation of two devices with the same name and symbol but different logical characteristics.

See also:

• "Pin Delays and Inversion" (page 28) in Chapter IV - Schematic Changes to Support Simulation for information on pin inversion in sub-circuit blocks.

• Chapter IX - Primitive Devices (page 107) for information on how pin inversion can be used with specific primitive types.

• Appendix D - Primitive Device Pin Summary (page 147) for more information on pin usage and pin inversion.

• Chapter X - Device Symbol Editing in the DesignWorks/Schematic Reference Manual for procedures on setting pin attributes when creating a symbol.

## Triggers

The DesignWorks Simulator has a powerful trigger capability analogous to a "word recognizer" on a logic analyzer. Any number of triggers can be set to perform various actions when certain time and signal value conditions are met. These actions include:

- Drawing reference lines in the timing window.

- Stopping the simulator.

- Enabling or disabling the timing display.

- Generating a beep from the computers speaker.

- Enable checking for another trigger.

Any number of triggers can be set up with different activation conditions. For display purposes, triggers are named T1, T2, T3, etc. To assist in setting up complex time-related conditions, trigger  $T_N$  can be used to enable  $T_{N+1}$ .

See Chapter V - The Simulator Tool (page 37) for more information on setting triggers.

### **Simulation Clearing and Initialization**

The DesignWorks Simulator provides a number of mechanisms to assist in setting initial values and restarting a simulation.

#### **The Clear Simulation Operation**

The Clear Simulation operation is invoked by clicking on the Reset control in the Simulator window. This operation performs the following steps:

• Other tools (such as Timing and Test Vector) are notified and perform their own processing.

• All signal change events on the queue are disposed of, whether pending or historical.

• Any clocks in the design are re-initialized.

• If any signal or pin initial values are specified, they are set up. See below for information on setting initial values.

• All devices are queued for immediate reevaluation.

#### **The Clear Unknowns Operation**

The Clear Unknowns operation is invoked by clicking on the Clear X control in the Simulator window. This operation performs the following steps, stopping as soon as all unknown states are removed from the design:

• Any pending signal change that would result in an unknown state is removed from the queue.

• Any primitive type with storage capability (i.e. flip-flop, register or counter) that has a "Don't Know" output value is cleared, either to its specified initial value (if any) or to zero.

• The input mapping for the design is temporarily set so that all unknown input values map to zero.

• A single device that currently has an unknown output state is randomly selected and queued for reevaluation. The simulator is cycled repeatedly as long as the number of unknown states in the design decreases. This step is then repeated until the number of unknowns ceases to diminish.

• The input mapping for the design is restored to its original state.

If this operation does not clear the design to an appropriate state, refer to the other techniques discussed below.

NOTE: Designs with "hard" unknowns, such as unconnected inputs or conflicting outputs will **not** be successfully cleared by this procedure. All device inputs should be specified to a known value if not driven by other devices.

#### **Setting Initial Values**

Initial values can be specified for signals and pins which will be applied by the Clear Simulation and Clear Unknowns operations, as described in the preceding sections.

For both object types, the initial value is entered into an attribute field, either Initial.Sig or Initial.Pin. The allowable values consist of a single character chosen from the following table.

| Character | Value  |

|-----------|--------|

| 0         | LOW    |

| 1         | HIGH   |

| Z         | HIGHZ  |

| Х         | DONT01 |

All other values will be ignored.

#### NOTES:

1) It is left completely to the user to decide if the specified initial values make sense. E.g. No checking is done to determine if a given device output value is the reasonable result of the device's current inputs.

2) Devices do not have initial value settings since their values are completely determined by the state of their output pins. See Pin Initial Values below.

#### Signal Initial Values

The initial value for a signal is stored in the Initial.Sig attribute field using the format described in the previous section. When a Clear Simulation operation is invoked, the initial value specified is placed on the signal without regard for the current output levels of devices driving the signal. The given value will stay on the signal until some device driving the signal changes state or some other user action changes it.

NOTE: If a pin initial value is specified for any output pin driving the signal, the signal value will be overridden.

#### Pin Initial Values

The initial value for a pin is stored in the Initial.Pin attribute field using the format described earlier. Initial values can only be specified for output or bidirectional pins and will be ignored on input pins.

When a Clear Simulation operation is invoked, the initial value specified is placed on the pin without regard for the current inputs affecting the device. The given value will stay on the pin until the device model schedules a state change or some other user action changes it. This page has been intentionally left blank.

## **Chapter IV - Schematic Changes to Support Simulation**

This chapter describes schematic related issues including signal naming, power and ground, simulation models, probing as well as changes to the Schematic tool to support simulation

## **Schematic Simulation Issues**

#### **Hierarchy Mode**

The DesignWorks Schematic tool supports three hierarchy modes: Flat, Physical and Pure. The following table summarizes these modes in terms of their significance for simulation.

| Mode     | Comment                                                                                                                                                                                                                                                                             |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Flat     | Despite its name, Flat mode does allow devices to have internal circuits for simulation purposes, although it will discourage access to them. Flat mode also changes the way device names are assigned and reports are generated, but these issues do not affect the simulator.     |  |

| Physical | This mode allows unrestricted access to internal circuits for simulation purposes.                                                                                                                                                                                                  |  |

| Pure     | Simulation is <u>not supported</u> in Pure mode as only a single<br>definition copy of device type data is kept in memory, regardless<br>of the number of times the device is used. Therefore, there is<br>nowhere to store the simulation states associated with each<br>instance. |  |

#### **Working With Hierarchical Blocks**

The simulator does not impose any new rules on working with hierarchical blocks, but there are some effects of editing a design with active simulation that should be noted.

See Chapter VII - Hierarchical Design in the DesignWorks/Schematic Reference Manual for additional information.

#### Editing an Open Internal Circuit

A number of issues arise if the same device type or hierarchical block appears multiple times in a design and one copy of the type or block is opened for editing (i.e. using the Push Into command or by double-clicking on the device):

• The Schematic tool creates a separate, temporary type definition for the open device when it is opened. Any simulation values viewed or changed, or any circuit changes made, will <u>apply only to that one device</u> instance while it remains open.

• When the open internal circuit is closed, the action taken depends on edits that have taken place. If no edits have been made or changes have been made <u>only to instance data</u> (i.e. simulation values or attributes marked as "keep with instance"), then the other blocks of the same type <u>will not</u> be affected by the close. If <u>any definition data</u> (i.e. any graphical or structural change to the circuit or any definition attribute change) has changed then a dialog is displayed prompting for the action to take. If the Update control is selected then all instance data (i.e. signal values, etc.) in other blocks of the same type will be <u>lost</u>. Instance data will be completely replaced by the values from the edited block.

#### The Port Interface

The connection between a pin on a parent device symbol and the corresponding signal in the internal circuit is quite complex from a simulation standpoint. In order for this connection to act like a "hard wire" between the two levels, the following conditions must be met:

- the *pin type* on the parent device symbol must be "bidirectional".

- the *pin type* of the corresponding port connector in the internal circuit must be "bidirectional".

- the *pin delays* on <u>both</u> the pin on the parent device <u>and</u> the pin on the port connector must be zero.

- no *pin inversion* must be specified either on the parent device pin or the port connector pin.

Any other combination of settings will result in some degree of isolation or "buffering" between the two levels. I.e. The observed signal value on the signal in the internal circuit may be different from that on the parent pin.

NOTE: When a symbol is created in the DevEditor tool, all pins default to type "input", i.e. they will not drive any attached signal. When creating a hierarchical block symbol for simulation purposes, the pin types must be set to appropriate values.

The effects on these various settings are summarized in the following sections.

Parent Device Pin Type

Any signal value driven out of a parent pin by an internal circuit may be translated according to the pin type on the parent device. These effects are summarized in the following table.

| Pin Type                         | Effect                                                                                                                                                                                                              |  |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Input                            | This will prevent that pin from ever driving the attached signal, regardless of drives in the internal circuit.                                                                                                     |  |

| Output / Three-state             | This will pass the sum of the internal drives up to the parent pin without any translation. Signal value changes on the signal attached to the parent pin <u>will</u> <u>not</u> be passed to the internal circuit. |  |

| Open collector /<br>Open emitter | y drive level from the internal circuit will be<br>nslated according the capability of the pin type.<br>e Appendix C - Device Pin Types (page 141) for<br>ore details.                                              |  |

| Bidirectional                    | All changes on the internal signal are passed to the parent pin and vice versa.                                                                                                                                     |  |

| Other types                      | Other types, such as Tied High and Tied Low are not recommended.                                                                                                                                                    |  |

NOTE: Although it may be tempting to set all pins to "bidirectional", this is not recommended since it significantly increases simulation overhead and increases the difficulty of isolating circuit drive problems.

Port Connector Pin Type

The pin type on the port connector is also used to translate the value of any incoming signal changes, in a manner similar to the parent pin type. Normally, the pin type setting on a port connector should complement the setting of the parent pin as follows:

| Parent Pin Type | Port Connector Name | Port Connector Pin Type |

|-----------------|---------------------|-------------------------|

| Input           | Port In             | Output                  |

| Bidirectional   | Port Bidir          | Bidirectional           |

| All others      | Port Out            | Input                   |

Other settings on the port connector pin are not recommended.

#### Pin Delays and Inversion

The normal pin delay and inversion settings can be applied to the port interface. A non-empty value in the Invert.Pin attribute field will cause any signal values passing in either direction to be inverted. An integer value in the Delay.Pin attribute will cause the specified delay to be inserted in line with level changes passing in either direction.

#### NOTES:

1) It is recommended that pin delay and inversion settings be applied <u>only</u> to the pin on the parent device and <u>not</u> to the port connector in the internal circuit. Attribute settings on the port connector are more difficult to verify and edit since the port connector is a "pseudo-device" and some schematic editing operations will be disabled.

2) Changes made in Invert.Pin and Delay.Pin attribute field after a device has been placed on the schematic, will affect only that one device instance. Default values can be set in these attribute fields when the symbol is created in DevEditor tool.

#### **Power and Ground Connectors**

Power and Ground connector symbols do not have any inherent simulation signal drive unless their pin type has been set to "Tied High" or "Tied Low", as appropriate. Most of the positive-supply symbols provided with this DesignWorks have "tied high" settings, while others will be "tied low". The symbols provided with older DesignWorks releases may not have any drive setting, resulting in a high impedance level on these signals. This can be remedied by either:

• Replacing <u>any one or all of</u> the ground or power symbols with one that has the appropriate setting.

• Forcing a Stuck High or Stuck Low level onto the signal using the probe tool, Test Vector tool or other external means. Note that because all like-named ground or power segments are logically connected, this only needs to be done on any one segment.

#### **Special Signal Names 0 and 1**

The signal names "0" and "1" are recognized by the simulator as special. If any signal is named "0", it will be given a Stuck Low value. If "1" is found, it will be given a Stuck High value. These values can be cleared or changed using the probe tool, if desired.

See "Probing Signals" (page 31) in Chapter IV - Schematic Changes to Support Simulation for more information.

## **Simulation Models**

In order to completely simulate a design, every symbol must have an associated simulation model. In DesignWorks, simulation models can take one of the following forms:

• Primitive Devices - These types have "hard-wired" program code to evaluate input and output changes. They include the gates, flip-flops and other devices as described in Chapter IX - Primitive Devices, as well as the user-definable PROM and PLA primitives.

• Sub-circuit Devices - The simulation function of a sub-circuit device is completely determined by its internal circuit (except for the addition of pin delays and inversion). The definition of a device sub-circuit can be stored with the part in a library (referred to as an "internal sub-circuit") or can be stored in a separate design file on disk (an "external sub-circuit"). The subcircuit itself can contain any combination of primitive devices or other subcircuits (except itself, of course!) nested to any desired depth.

Whenever any device type is to be simulated, all information about the device must be loaded into memory. Unless internal circuits or code models are explicitly purged from the design, they will become a permanent part of the design and will be saved with the file.

#### **Primitive Devices on the Schematic**

Primitive devices are provided in various primitive libraries and can be used at any time as part of a schematic, whether or not the simulator is installed. However, these libraries are not intended to match any real logic families and do not have any part name, pin number or packaging information associated with them.

See Chapter IX - Primitive Devices (page 107) for more information on creating and using primitive types.

#### **Simulation Pseudo-Devices**

The simulation pseudo-devices (i.e. those in the Primitive I/O library) are handled specially by the Schematic tool. In general, the symbol, pin types or other characteristics of these devices cannot be modified. In addition, they are treated differently from normal device symbols in the following ways:

• By default, these devices are flagged "omit from report", meaning that they will not appear in any netlist or bill of materials produced by the Report tool. This setting can be changed using the Schematic tool's Get Info command.

• These symbols will not be assigned a name when placed on a schematic. A name can be manually assigned, if desired.

• The switch and keyboard types respond to a normal mouse click by changing state, rather than being selected. To select one of these devices hold the shift key down while clicking on it.

#### **Using External Sub-Circuit Models**

Most of the models for industry-standard device types (e.g. 74XX, 4000, etc.) are provided as external sub-circuits. These models are simply design files containing an equivalent circuit for the device. The circuits are designed to match with the symbol libraries provided with the Schematic package.

External sub-circuit models can be loaded either interactively, i.e. as each part is used, or in batch mode after the design is created. Both of these functions are provided by the SimLoad tool.

See Chapter VI - The SimLoad Tool (page 53) for more information.

## **Probing Signals / Schematic Tool Palette**

When the Simulator Tool is installed, a probe tool in available in the palette window displayed by the Schematic tool. Selecting the Probe tool places the schematic in Probe mode, allowing signal and pin values to be displayed and injected. When the probe tip is clicked and held on a signal or pin, the cursor will show the current value on the signal or pin and track changes that occur as the simulation progresses.

# **Probing a Signal**

Only the signal under the cursor at the time of the click is examined. Moving the mouse while the button is pressed does not change the signal being viewed.

# **Probing a Pin**

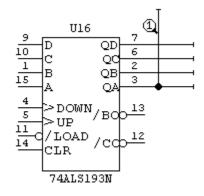

If the probe tip is clicked on a device pin close to the device body, the probe shows the driving level of that pin, rather than the state of the attached signal. This can be used to resolve drive conflicts in multiple drive situations, as in the following example:

# Injecting a Value Using the Probe Tool

While the mouse button is held, press the appropriate key to inject a new value onto a signal:

| Key   | Injected Value |  |

|-------|----------------|--|

| 0     | LOW.F          |  |

| 1     | HIGH.F         |  |

| Х     | DONT01.F       |  |

| С     | CONF.F         |  |

| Z     | HIGHZ          |  |

| L     | LOW.F stuck    |  |

| Н     | HIGH.F stuck   |  |

| space | Unstick        |  |

If a stuck value is forced onto a signal, it will not change state until the stuck value is cleared by some user action, regardless of device outputs driving the line. If a non-stuck value is forced, the signal value will revert to its appropriate new level when any change occurs on a device output driving the line.

The spacebar "unstick" command causes the signal to revert to its driven value.

Note: values cannot be injected onto pins.

See "Stuck-at Levels" (page 10) in Chapter III - Simulation Details for more information.

# **Schematic Menu Changes**

When the simulator is installed, two new menu items appears in the Schematic menu.

# **Simulation Menu**

### Parameters...

This command displays the Simulation Parameters dialog and is enabled when at least one device or pin is selected in the schematic.

See "Simulator Procedures / Simulation Parameters" (page 43) in Chapter V -The Simulator Tool for more information.

# **Timing Menu**

## Add Automatically

When signals are created or named they will be automatically added to the Timing window (if displayed) when this command has a check mark beside it.

### Add to Timing

This command adds all selected signals to the Timing window (if displayed).

### Add as Group

This command adds all selected signals as a group to the Timing window (if displayed).

See Chapter VII - The Timing Tool (page 61) for more information.

This page has been intentionally left blank.

# **Chapter V - The Simulator Tool**

# Introduction

The chapter describes control of the simulator via the Simulator tool.

### Starting the Simulator

By default, the simulator starts running as soon as a circuit is loaded. To display the simulator control window, select "Simulator" from the Tools menu in the DesignWorks window

# **Simulator Window**

The simulator window is a floating window. It is displayed when the Simulator tool is selected from the "Tool" menu in the DesignWorks window OR when a new timing window is created. It can be hidden by selecting "Close" from the system menu in the top left corner of the window.

|              | — Simu        | ılator [DESIGN1.CCT] |

|--------------|---------------|----------------------|

|              | Speed Options |                      |

| Time Display | ldle          | Reset Run Step       |

|              | < =           | > Triggers Clear X   |

| Item         | Comment                                                                                                                                                                                                                                                                               |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Time Display | The status area in the top left corner of the simulator<br>window displays the current simulation time as the<br>simulator progresses or "Idle" if the simulator is not<br>running.                                                                                                   |

| Reset        | Removes all scheduled signal events, sets all devices,<br>signals and pins to their specified initial values (if any)<br>and recalculates output values for all circuit elements. In<br>addition, it clears the timing window (if open) and resets<br>the Test Vector tool (if open). |

| Run          | Causes the simulator to execute at the fastest possible speed.                                                                                                                                                                                                                        |

| Step         | Causes the simulator to execute one time step. If the simulator is running then this control causes the simulator to stop after the next event time.                                                                                                                                  |

| Clear X        | Clears all flip-flop, counter and register primitives to the<br>zero state and attempts to remove all unknown signal<br>values from the circuit. Certain circuit conditions may<br>prevent signals from being placed in a known state such<br>as unconnected inputs that have not been set to a known<br>level, storage devices, such as RAMs that have an<br>unknown stored value and/or any simulation models that<br>do not produce a known output when all inputs are<br>known. |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Triggers       | Displays the trigger control dialog. See Simulator<br>Procedures / Triggers (page 40) for more information                                                                                                                                                                                                                                                                                                                                                                          |

| < (Zoom In)    | Increases the horizontal display resolution in the Timing window (if it is displayed).                                                                                                                                                                                                                                                                                                                                                                                              |

| > (Zoom Out)   | Decreases the horizontal display resolution in the Timing window (if it is displayed).                                                                                                                                                                                                                                                                                                                                                                                              |

| = (Clear Zoom) | Sets the horizontal display resolution in the Timing window (if it is displayed) to its initial defaults.                                                                                                                                                                                                                                                                                                                                                                           |

# **Simulator Window Menu Commands**

# Speed Menu

The Speed menu is used to control the simulation speed, i.e. the amount of delay inserted between simulation steps. Simulation speed can be set individually for each open design.

### <u>Stop</u>

This command stops the simulator immediately. No simulation processing is done when the simulator is in this state.

# <u>Run</u>

This command starts the simulator at the fastest possible speed.

# Single Step

This command simulates one time step. To perform the single step, the simulator looks at the time value associated with the next signal change event in the queue, simulates the effect of that and all following events scheduled at the

same time, then returns to the stopped state. The actual time value of a single step depends on the nature of the circuit.

### **Other Simulation Speeds**

The intermediate speed settings between Stop and Run insert various amounts of delay between executing successive simulation time steps. These can be used to slow the simulation progress for convenient observation.

## **Options Menu**

#### Parameters...

This command displays the Simulation Parameters dialog and is enabled when at least one device or pin is selected in the schematic.

*See "Simulator Procedures / Simulation Parameters" (page 43) in Chapter V - The Simulator Tool for more information.*

### Simulation Scope...

This command displays the Simulation Scope dialog.

See "Simulator Procedures / Simulation Scope" (page 50) in Chapter V - The Simulator Tool for more information.

### Stick Signals...

This command displays the Stick Signals dialog.

See "Simulator Procedures / Stick Signals" (page 51) in Chapter V - The Simulator Tool for more information.

# **Simulator Procedures**

## Triggers

Selecting the triggers control in the Simulator window displays the following dialog:

| Simulation Trigger Setup for T1 |                   |                               |  |

|---------------------------------|-------------------|-------------------------------|--|

|                                 |                   | 🛛 Enabled                     |  |

| TIME Test                       | SIGNALS Test      | DELAY Test                    |  |

|                                 | Names             | ]   🖲 N/A                     |  |

| ● N/A ○ =                       | Value             | │ ○ After<br>│ ○ Sig Stable > |  |

| ⊖ Every ○ >                     |                   | Sig Stable <                  |  |

| II – · –                        | iming Display On  | K Cancel Delete               |  |

| Stop 1<br>Enable T2             | Iming Display Off | Prev Next                     |  |

## **Trigger Conditions**

A trigger is activated when all three sets of conditions are met:

- The time condition, i.e. the current simulator time value is less than, equal to, greater than, or a multiple of, a given value.

- Signal value condition, i.e. one or more signals are at specified levels.

- The delay condition, i.e. the trigger is activated after a certain delay, or the signal condition exists for greater or less than a specified amount of time.

### Trigger Enabling

When the "Enabled" switch is on, the trigger is "armed" and the selected actions will take place as soon as the trigger's conditions are met. If this switch is off, this trigger is disabled until enabled by the previous trigger or by this switch being selected.

### **Time Test Controls**

The controls related to the time condition are summarized in the following table.

Control Comment

| Time<br>Value | Enter the time value as a decimal integer. The meaning of this value is determined by the switches below it.                                                     |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N/A           | This control specifies that the time condition should be<br>considered to be always true. The time value is ignored.                                             |

| Every         | This control specifies that the trigger will be activated every time<br>the simulator time equals a multiple of the specified value.                             |

| <, =, >       | These controls indicate that the trigger will be activated when<br>the simulation time is less than, equal to, or greater than the given<br>value, respectively. |

# Signal Test Controls

The controls related to the signal condition are summarized in the following table.

| Control          | Comment                                                                                                                                                                                                                                                   |                          |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|--|

| Names            | Enter the names of one or more signals whose values will be<br>compared to the hexadecimal integer value typed in the Value<br>field. One or more signals can be entered using the following<br>formats:                                                  |                          |  |  |

|                  | CLK The single signal CLK                                                                                                                                                                                                                                 |                          |  |  |

|                  | D70 The signals D7 (MSB), D6, D5 D0                                                                                                                                                                                                                       |                          |  |  |

|                  | IN1 OUT3                                                                                                                                                                                                                                                  | The signals IN1 and OUT3 |  |  |

| Signals<br>Value | Enter the signal comparison value as a hexadecimal integer. This value is converted to binary and compared bit-for-bit with the signals named in the Names field. The rightmost signal name is compared with the least significant bit of the value, etc. |                          |  |  |

# **Delay Condition Controls**

The controls related to the time condition are summarized in the following table.

| Control      | Comment                                                                                                                                                                                           |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N/A          | This control specifies that the delay condition should be<br>considered to be always true. The delay value is ignored.                                                                            |

| After        | With this control enabled, the trigger will be activated the specified amount of time after the time and signal value conditions are met, <u>regardless of whether they continue to be true</u> . |

| Sig Stable > | With this control enabled, the trigger will be activated after<br>the specified delay, <u>as long as the time and signal conditions</u><br><u>are still true</u> .                                |

| Sig Stable < | With this control enabled, the trigger will be activated if the time and signal conditions are true for less than the specified delay. I.e. Activation occurs when the time and signal conditions <u>cease to be true</u> if they have been true for less than the specified value. |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Delay Value  | Enter the delay value as a decimal integer.                                                                                                                                                                                                                                         |

# **Trigger Actions Controls**

When a trigger is activated, any combination of the displayed actions can be invoked.

| Control                 | Comment                                                                      |  |

|-------------------------|------------------------------------------------------------------------------|--|

| Веер                    | Generates a single system beep.                                              |  |

| Stop                    | Stops the simulator immediately.                                             |  |

| Enable T <sub>N+1</sub> | Enables the next numbered trigger.                                           |  |

| Timing Display On       | Turns on the timing waveform display.                                        |  |

| Timing Display<br>Off   | Turns off the timing waveform display.                                       |  |

| Reference Line          | Draws a vertical reference line at this time on the timing waveform display. |  |

# Navigation Controls

The navigation controls perform the following functions:

| Control | Comment                                                                                        |  |

|---------|------------------------------------------------------------------------------------------------|--|

| OK      | Accept changes for this trigger and close the dialog.                                          |  |

| Cancel  | Discard changes for this trigger and close the dialog.                                         |  |

| Delete  | Delete this trigger and close the dialog. All subsequent triggers, by number, are decremented. |  |

| Prev    | Accept changes for this trigger and display the previous trigger (if one exists).              |  |

| Next    | Accept changes for this trigger and display the next trigger.                                  |  |

# **Simulation Parameters**

The Simulation Parameters is a general method of setting device and pin delays and options. If no devices or pins are selected in a circuit then Simulation Parameters menu command will be disabled. This command displays the

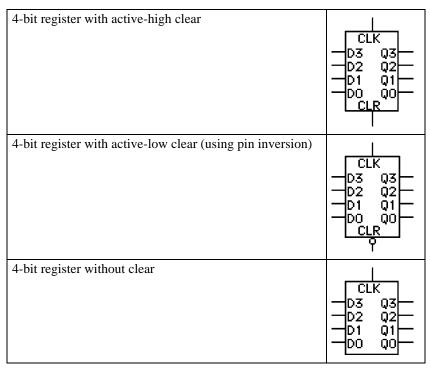

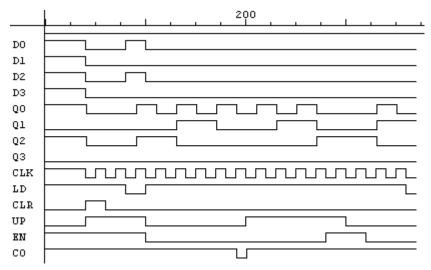

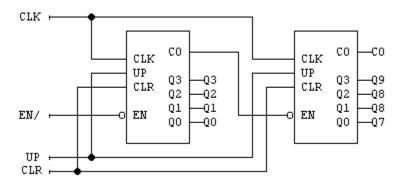

| Selection                                                  | Dialog              | Notes                                                                                                                                  |