CSE 370 FPGA IO Pins

IO Pins on FPGA

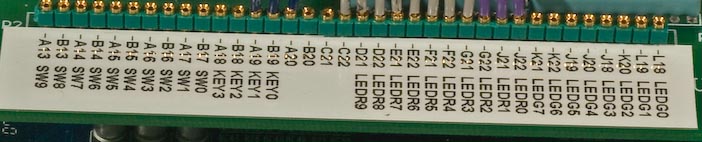

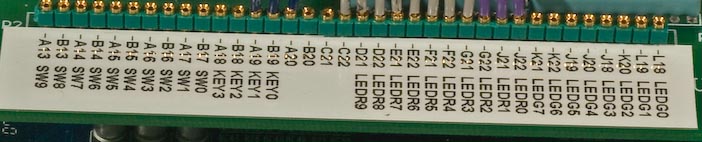

The IO Pins you see running along the bottom of your board are directly

connected to your FPGA. You can read more about these pins on Altera's

website here:

DE1 Specifications. You probably remember hooking Switches, Keys, and

LEDs up to these IO Ports. This is because your FPGA came pre-loaded with

a program that directed the Switches, Keys, and LEDs to these ports. However,

now that you are programming the FPGA yourself, the IO Ports are no

longer mapped which means you can map them however you like with your .qsf

file. Below is a table which describes the IO Port Pin, and the

functionality of the IO Port based on the pre-loaded FPGA program. You

can use this table as a guide when writing your .qsf file. As always, you can

also use the pinouts.html page as a guide for

accessing the Switches, Keys, and LEDs. The table below is in order from the

right side of the board to the left. The first half 18 PINS on the left side

of the table, and the second half of the 18 PINs on the right side of the

table.

The IO Pins

| Pin | Intial Function | | Pin |

Intial Function |

| PIN_L18 | LEDG0 | | PIN_C22 |

None |

| PIN_L19 | LEDG1 | | PIN_C21 |

None |

| PIN_K20 | LEDG2 | | PIN_B20 |

None |

| PIN_J18 | LEDG3 | | PIN_A20 |

None |

| PIN_J20 | LEDG4 | | PIN_B19 |

KEY0 |

| PIN_J19 | LEDG5 | | PIN_A19 |

KEY1 |

| PIN_K22 | LEDG6 | | PIN_B18 |

KEY2 |

| PIN_K21 | LEDG7 | | PIN_B18 |

KEY3 |

| PIN_J22 | LEDR0 | | PIN_B17 |

SW0 |

| PIN_J21 | LEDR1 | | PIN_A17 |

SW1 |

| PIN_G22 | LEDR2 | | PIN_B16 |

SW2 |

| PIN_G21 | LEDR3 | | PIN_A16 |

SW3 |

| PIN_F22 | LEDR4 | | PIN_B15 |

SW4 |

| PIN_F21 | LEDR5 | | PIN_A15 |

SW5 |

| PIN_E22 | LEDR6 | | PIN_B14 |

SW6 |

| PIN_E21 | LEDR7 | | PIN_A14 |

SW7 |

| PIN_D22 | LEDR8 | | PIN_B13 |

SW8 |

| PIN_D21 | LEDR9 | | PIN_A13 |

SW9 |

Comments to: cse370-webmaster@cs.washington.edu