***NOTE

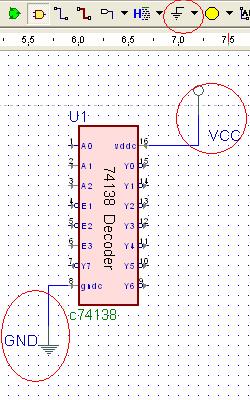

If you look on the chip you will see a few inputs called E1, E2, and E3. These are the enables, you need to use these to turn on and off the chip. Enables aren't too complicated though they are difficult to understand at first. Enables are like the power switch to the chip. If any of them are disabled the chip won't perform correctly, just like a computer won't work if you don't turn it on first.

Like with most electronics the enable is only considered "ON" when the chip sees the input to be a 1. Of course that means you generally have to connect up VCC to it so that the Enables are read as being "ON" or being a "1". However, sometimes if you look on the chipmap you will see that there is a little bar over the E. This means that the input is inverted, whatever goes in is flipped. In this case if you hooked up VCC, it would get inverted to GND and the chip still wouldn't work. In the case where there is a little bar you should hook up GND so that when it is inverted it is read as a "1" or "ON". Keep that in mind and everything should work well!