## Comparator example (con't) // Make a 4-bit comparator from 4 1-bit comparators module Compare4(Equal, Alarger, Blarger, A4, B4); input [3:0] A4, B4; output Equal, Alarger, Blarger; wire e0, e1, e2, e3, A10, A11, A12, A13, B10, B11, B12, B13; Compare1 cp0(e0, A10, B10, A4[0], B4[0]); Compare1 cp1(e1, Al1, Bl1, A4[1], B4[1]); Compare1 cp2(e2, A12, B12, A4[2], B4[2]); Compare1 cp3(e3, A13, B13, A4[3], B4[3], ); assign Equal = (e0 & e1 & e2 & e3); assign Alarger = (Al3 | (Al2 & e3) | (All & e3 & e2) | (Al0 & e3 & e2 & e1)); assign Blarger = (~Alarger & ~Equal); endmodule CSE370, Lecture 8 21

## **Functions** • Use functions for complex combinational logic module and\_gate (out, in1, in2); input in1, in2; output out; assign out = myfunction(in1, in2); function myfunction; input in1, in2; begin myfunction = in1 & in2; end **Benefit:** endfunction Functions force a result $\Rightarrow$ Compiler will fail if function endmodule does not generate a result CSE370, Lecture 8 22

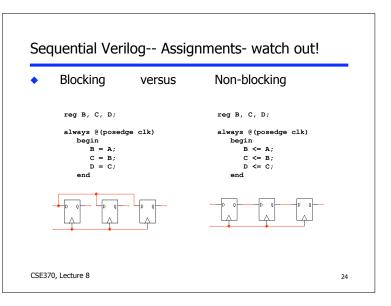

## Sequential Verilog-- Blocking and non-blocking assignments

Blocking assignments (Q = A) Variable is assigned immediately New value is used by subsequent statements Non-blocking assignments (Q <= A)</li> Variable is assigned after all scheduled statements are executed Value to be assigned is computed but saved for later Usual use: Register assignment Registers simultaneously take new values after the clock edge Example: Swap always @(posedge CLK) always @ (posedge CLK) begin begin A <= B; temp = B; B <= A; B = A: end A = temp;end CSE370, Lecture 8 23