***NOTE

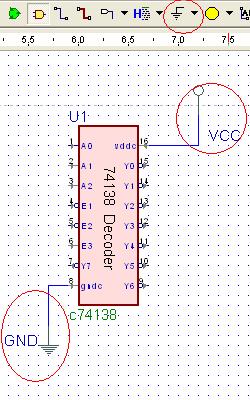

If you look on the chip shown above you will see a few inputs called E1, E2, and E3. These are the enables and if they are not set to the correct logic level the chip will not work. E1 and E2 are shown with circles on their inputs. This means they are active low and they must be set to GND in order for the chip to be enabled. E3 does not have a circle and must therefore be set to VCC. ALL enables must be hooked up correctly in order for the chip to work. Note that in the chip maps E1 and E2 are shown with a line over them. This is another way of indicating that they are active low.