## Overview Last lecture Sequential Verilog Today Review of D latches and flip-flops T flip-flops and SR latches State diagrams Asynchronous inputs

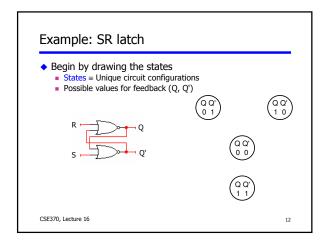

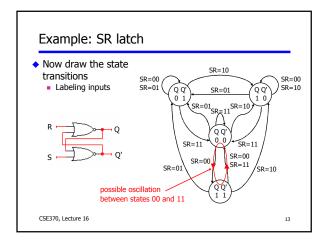

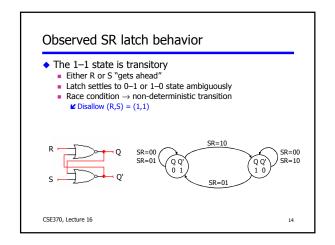

# State diagrams • How do we characterize logic circuits? ■ Combinational circuits: Truth tables ■ Sequential circuits: State diagrams • First draw the states ■ States ≡ Unique circuit configurations • Second draw the transitions between states ■ Transitions ≡ Changes in state caused by inputs

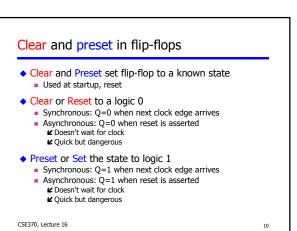

### System considerations

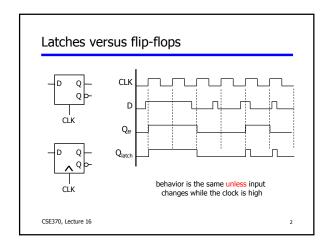

- Use edge-triggered flip-flops wherever possible

- Avoid latches

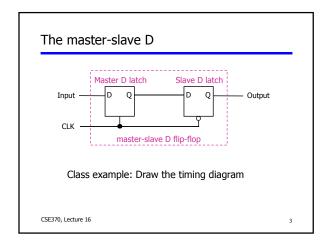

- Most common: Master-slave D

- ◆ Basic rules for correct timing

- Clock flip-flops synchronously (all at the same time)

✓ No flip-flop changes state more than once per clock cycle

- Avoid mixing positive-edge triggered and negative-edge triggered flip-flops in the same circuit

15

CSE370, Lecture 16

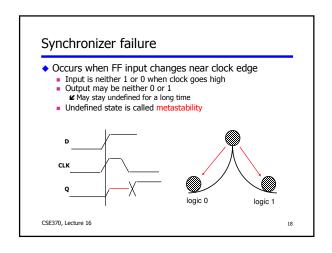

### Asynchronous inputs

- Clocked circuits are synchronous

- Circuit changes state only at clock edges

- Signals (voltages) settle in-between clock edges

- ◆ Unclocked circuits or signals are asynchronous

- No master clock

- Real-world inputs (e.g. a keypress) are asynchronous

- Synchronous circuits have asynchronous inputs

- Reset signal, memory wait, user input, etc.Inputs "bounce"

- Inputs can change at any time

We must synchronize the input to our clock ✔ Inputs will violate flip-flop setup/hold times

CSE370, Lecture 16 16

## Debouncing Switch inputs bounce i. e. don't make clean transitions Can use SR latch for debouncing Eliminates dynamic hazards "Cleans-up" inputs 3.3V -3.3V CSE370, Lecture 16 17