## CSE370 Final Exam (16 March 2005)

Please read through the entire examination first! This exam was designed to be completed in 110 minutes (one hour and 50 minutes) and, hopefully, this estimate will be reasonable.

There are 3 problems for a total of 100 points. The point value of each problem is indicated in the table below. Each problem and sub-problem is on a separate sheet of paper. Write your answer neatly in the space provided. If you need more space (you shouldn't), you can write on the back of the sheet where the question is posed, but please make sure that you indicate clearly the problem to which the comments apply. Do NOT use any other paper to hand in your answers. If you have difficulty with part of a problem, move on to the next one. They are mostly independent of each other.

The exam is CLOSED book and CLOSED notes. Please do not ask or provide anything to anyone else in the class during the exam. Make sure to ask clarification questions early so that both you and the others may benefit as much as possible from the answers.

Good luck and have a great break.

Name:

ID#:

| Problem | Max Score | Score |

|---------|-----------|-------|

| 1       | 25        |       |

| 2       | 40        |       |

| 3       | 35        |       |

| TOTAL   | 100       |       |

## 1. Combinational Logic (25 points)

(a - 5 pts) Write the following function in canonical sum-of-products form. Feel free to choose to write terms either with four variables each (e.g., A'B'CD) or in minterm notation (e.g., m<sub>3</sub>).

Z = (AC') (B xor D)' + (A'C) (B'D')'

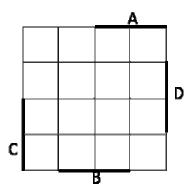

(b - 5pts) Minimize the function via the K-map method with the addition of don't cares for AB'D and A'B'D'.

(c - 5pts) List all the prime implicants for the function of part (b). Which are essential prime implicants?

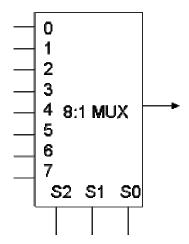

(d - 10pts) Implement your result for part (b) using an 8:1 multiplexer (provided below) and at MOST one inverter. S2 is the most significant bit of the control signals, S0 is the least significant, therefore, S2=1, S1=1, S0=0 selects input #6.

## 2. Finite State Machines (40 points)

The following Verilog was found among old papers in a dusty drawer of a now defunct dot-com company. Unfortunately, there were no comments in the code.

```

module StuffFrame(Enable, Ready, DataIn, DataOut, Sending, Clk, Reset);

input Enable, DataIn, Clk, Reset;

output

Ready, DataOut, Sending;

reg [6:0] state;

reg [6:0] next_state;

parameter START = 7'b0000000;

parameter BEGIN1 = 7'b0000000;

parameter BEGIN2 = 7'b1100001;

parameter BEGIN2 = 7'b1100010;

parameter BEGIN3 = 7'b1100011;

parameter BEGIN4 = 7'b1010100;

parameter SEND0 = 7'b1010101;

parameter SEND1 = 7'b1110110;

parameter STUFF = 7'b1100111;

parameter END1 = 7'b1101000;

parameter END2 = 7'b1101001;

parameter END3 = 7'b1101010;

parameter END4 = 7'b1001011;

always @(posedge Clk) begin

if (Reset) begin state = START;

end

else

begin state = next_state; end

end

always @(Enable or DataIn or state) begin

case(state)

START:

if (Enable) next_state = BEGIN1; else next_state = START;

BEGIN1: next_state = BEGIN2;

BEGIN2: next_state = BEGIN3;

BEGIN3: next_state = BEGIN4;

BEGIN4: if (DataIn) next_state = SEND1; else next_state = SEND0;

SEND0:

if (~Enable) next_state = END1;

else if (DataIn) next_state = SEND1; else next_state = SEND0;

SEND1: if (~Enable) next_state = END1;

else if (DataIn) next_state = STUFF; else next_state = SENDO;

STUFF:next_state = SEND0;END1:next_state = END2;END2:next_state = END3;END3:next_state = END4;END4:next_state = START;

endcase

end

assign Sending = state[6];

assign DataOut = state[5];

assign Ready = state[4];

endmodule

```

(a - 10pts) What type of state machine is being described (Mealy, Moore, synchronous Mealy)? How many states does it have? Derive its state diagram and clearly label all transitions and the values for the 3 outputs in each state.

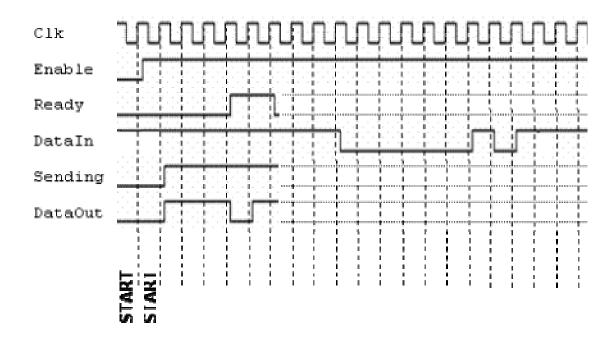

(b - 15pts) Simulate the state machine for the following sample input waveforms. Fill in the details for the signals Ready, Sending, and DataOut. Also, please indicate the state the FSM is in for each clock cycle. Assume that the FSM is initially in state "START".

(c - 15pts) We are now faced with the problem of implementing this circuit (the state diagram of part (a)) and our company has a special deal on 4-bit counters and we have to use one in our realization. We'll represent the last four bits of the state variable of our FSM using a counter – note that this state assignment (using only those 4 bits) is enough to uniquely identify each state. Verilog code describing the internals of the counter is shown below. Your job is to use its "clear", "enable", and "load" signals to control the counter's sequence so that it matches the state diagram's transitions. Don't worry about the outputs of the FSM, they will just be functions of the state bits realized by the counter.

Complete the following state table for the finite state machine. Make sure to use don't cares as much as possible. The first couple of rows are already filled in as an example.

| Inputs Outputs |             |            |                                                                             |                                                                                                                  |                                                                                                                                          |                                                                                                                                                                   |                                                                                                                                                                                           |

|----------------|-------------|------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |             | Cour       | unter Value                                                                 |                                                                                                                  |                                                                                                                                          |                                                                                                                                                                   |                                                                                                                                                                                           |

| Enable         | DataIn      | state[3:0] | next_state[3:0]                                                             | clear                                                                                                            | enable                                                                                                                                   | load                                                                                                                                                              | datain[3:0]                                                                                                                                                                               |

| х              | Х           | XXXX       | 0000                                                                        | 1                                                                                                                | Х                                                                                                                                        | Х                                                                                                                                                                 | XXXX                                                                                                                                                                                      |

| 0              | Х           | 0000       | 0000                                                                        | 1                                                                                                                | Х                                                                                                                                        | Х                                                                                                                                                                 | XXXX                                                                                                                                                                                      |

|                |             |            |                                                                             |                                                                                                                  |                                                                                                                                          |                                                                                                                                                                   |                                                                                                                                                                                           |

|                |             |            | -                                                                           |                                                                                                                  |                                                                                                                                          |                                                                                                                                                                   |                                                                                                                                                                                           |

|                |             |            |                                                                             |                                                                                                                  |                                                                                                                                          |                                                                                                                                                                   |                                                                                                                                                                                           |

|                |             |            |                                                                             |                                                                                                                  |                                                                                                                                          |                                                                                                                                                                   |                                                                                                                                                                                           |

|                |             |            |                                                                             |                                                                                                                  |                                                                                                                                          |                                                                                                                                                                   |                                                                                                                                                                                           |

|                |             |            |                                                                             |                                                                                                                  |                                                                                                                                          |                                                                                                                                                                   |                                                                                                                                                                                           |

|                |             |            |                                                                             |                                                                                                                  |                                                                                                                                          |                                                                                                                                                                   |                                                                                                                                                                                           |

|                |             |            |                                                                             |                                                                                                                  |                                                                                                                                          |                                                                                                                                                                   |                                                                                                                                                                                           |

|                |             |            |                                                                             |                                                                                                                  |                                                                                                                                          |                                                                                                                                                                   |                                                                                                                                                                                           |

|                |             |            |                                                                             |                                                                                                                  |                                                                                                                                          |                                                                                                                                                                   |                                                                                                                                                                                           |

|                |             |            |                                                                             |                                                                                                                  |                                                                                                                                          |                                                                                                                                                                   |                                                                                                                                                                                           |

|                |             |            |                                                                             |                                                                                                                  |                                                                                                                                          |                                                                                                                                                                   |                                                                                                                                                                                           |

|                |             |            |                                                                             |                                                                                                                  |                                                                                                                                          |                                                                                                                                                                   |                                                                                                                                                                                           |

|                |             |            |                                                                             |                                                                                                                  |                                                                                                                                          |                                                                                                                                                                   |                                                                                                                                                                                           |

|                |             |            |                                                                             |                                                                                                                  |                                                                                                                                          |                                                                                                                                                                   |                                                                                                                                                                                           |

|                |             |            |                                                                             |                                                                                                                  |                                                                                                                                          |                                                                                                                                                                   |                                                                                                                                                                                           |

|                |             |            |                                                                             |                                                                                                                  |                                                                                                                                          |                                                                                                                                                                   |                                                                                                                                                                                           |

|                |             |            |                                                                             |                                                                                                                  |                                                                                                                                          |                                                                                                                                                                   |                                                                                                                                                                                           |

|                |             |            |                                                                             |                                                                                                                  |                                                                                                                                          |                                                                                                                                                                   |                                                                                                                                                                                           |

|                |             |            |                                                                             |                                                                                                                  |                                                                                                                                          |                                                                                                                                                                   |                                                                                                                                                                                           |

|                |             |            |                                                                             |                                                                                                                  |                                                                                                                                          |                                                                                                                                                                   |                                                                                                                                                                                           |

|                |             |            |                                                                             |                                                                                                                  |                                                                                                                                          |                                                                                                                                                                   |                                                                                                                                                                                           |

|                |             |            |                                                                             |                                                                                                                  |                                                                                                                                          |                                                                                                                                                                   |                                                                                                                                                                                           |

|                |             |            |                                                                             |                                                                                                                  |                                                                                                                                          |                                                                                                                                                                   |                                                                                                                                                                                           |

|                | Enable<br>X | X X        | Enable         DataIn         state[3:0]           X         X         XXXX | Enable         DataIn         state[3:0]         next_state[3:0]           X         X         XXXX         0000 | Enable         DataIn         state[3:0]         next_state[3:0]         clear           X         X         XXXX         0000         1 | Enable         DataIn         state[3:0]         next_state[3:0]         clear         enable           X         X         XXXX         0000         1         X | Enable         DataIn         state[3:0]         next_state[3:0]         clear         enable         load           X         X         XXXX         00000         1         X         X |

## 3. Computer Organization (35 points)

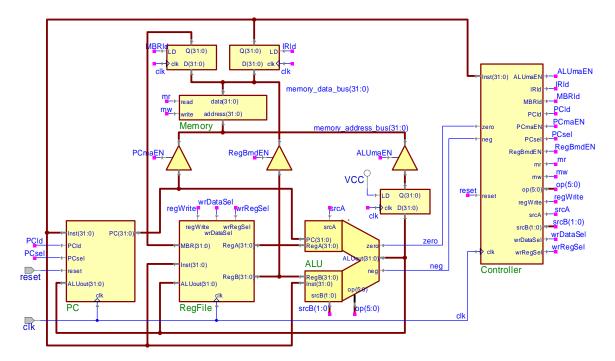

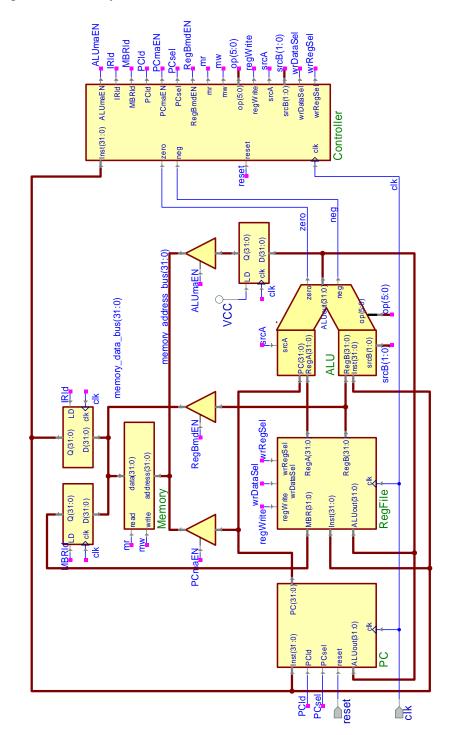

Below is the architecture diagram for the processor of Assignment #9 and #10.

Consider adding a new instruction to those that you implemented: SWI – "store word to immediate". SWI has a 6-bit op-code followed by a register specification (5-bits) and 21 bits that are to be used as the index into memory. The operation is:

(a – 10pts) What changes need to be made to the data-path to realize this instruction? Consider changes to RegFile and ALU or even adding additional paths, if needed. You can also feel free to add additional control signals, if needed. Make any changes to the diagram below (just a large version of the diagram on the previous page) with clear annotations. Recall that register "rs" is read into RegA every clock cycle and that the multiplexer on the B input of the ALU can choose between a sign-extended 16-bit offset, 0, 1, or RegB controlled by srcB[1:0].

(b - 10pts) Given the changes you specified in part a.1 and ignoring instruction fetch and instruction decode cycles, how many additional cycles do you need to execute this instruction? Specify the value of the control signals for each of these cycles in the table below (including any control signals you may have added or modified). Make sure to specify any don't cares. Using symbolic signal names is fine (as shown in the one entry below).

| Control Signal | Value in 1 <sup>st</sup> | Value in 2 <sup>nd</sup> | Value in 3 <sup>rd</sup> |  |

|----------------|--------------------------|--------------------------|--------------------------|--|

| C C            | Execute Cycle            | Execute Cycle            | Execute Cycle            |  |

|                |                          | (if needed)              | (if needed)              |  |

| IRld           |                          |                          |                          |  |

| MBRld          |                          |                          |                          |  |

| PCld           |                          |                          |                          |  |

| PCsel          |                          |                          |                          |  |

| mr             |                          |                          |                          |  |

| mw             |                          |                          |                          |  |

| PCmaEN         |                          |                          |                          |  |

| ALUmaEN        |                          |                          |                          |  |

| RegBmdEN       |                          |                          |                          |  |

| srcA           |                          |                          |                          |  |

| srcB[1:0]      |                          |                          |                          |  |

| Op[5:0]        | "pass B"                 |                          |                          |  |

| regWrite       |                          |                          |                          |  |

| wrDataSel      |                          |                          |                          |  |

| wrRegSel       |                          |                          |                          |  |

|                |                          |                          |                          |  |

|                |                          |                          |                          |  |

|                |                          |                          |                          |  |

(c – 15pts) Consider adding two flip-flops on the "zero" and "neg" signals between the ALU and the controller. How would this affect the processor? Consider the controller size (number of states), performance (minimum clock period), and any changes that may be required of the data-path. Which of the instructions: ADD, SUB, AND, OR, SLT, LW, SW, ADDI, BEQ, J, HALT would be affected by this change?