### Overview

- Last lecture

- State encoding

- Cone-hot encoding

Cone-hot enco

- ∠ Output encoding

- Today:

- Optimizing FSMs

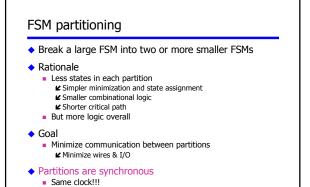

- **∠** Partitioning

- Conclusion of sequential logic

CSE370, Lecture 25

CSE370, Lecture 25

### **Definitions**

- ◆ Latency: Time to perform a computation

- Data input to data output

- ◆ Throughput: Input or output data rate

- Typically the clock rate

- Combinational delays drive performance

- Define d = delay through slowest combinational stage n = number of stages from input to output

- Latency ∝ n × d (in sec)

Throughput ∝ 1/d (in Hz)

CSE370, Lecture 25

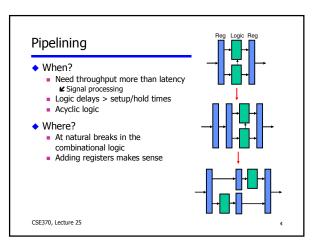

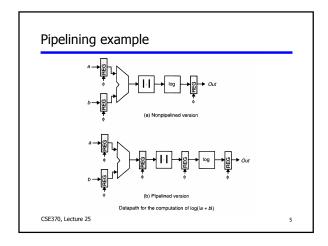

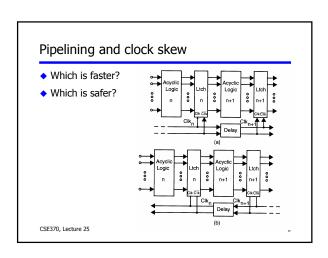

### **Pipelining** What? Subdivide combinational logic Logic Add registers between logic ♦ Why? Trade latency for throughput ✓ Increase clock speed ■ Increased latency ✓ Takes cycles to fill the pipe Increase circuit utilization ✓ Simultaneous computations

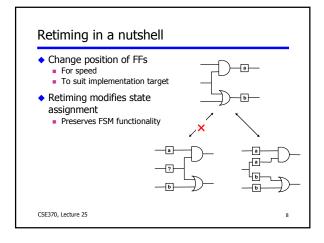

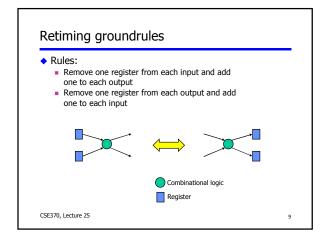

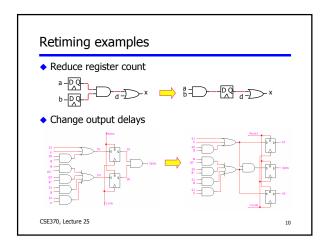

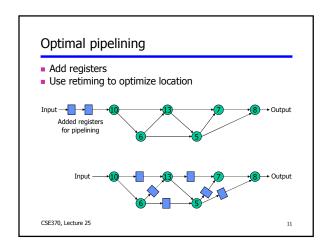

## Retiming ◆ Pipelining adds registers ■ To increase the clock speed ◆ Retiming moves registers around ■ Reschedules computations to optimize performance ✔ Minimize critical path ✔ Optimize logic across register boundaries ✔ Reduce register count ■ Without altering functionality

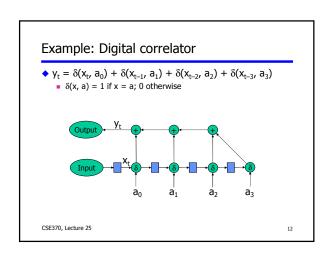

# Example: Digital correlator (cont'd) • Delays: Comparator = 3; adder = 7 Original design cycle time = 24 Input Retimed design cycle time = 13 Input Retimed design cycle time = 13 Input Retimed design cycle time = 13

14

CSE370, Lecture 25

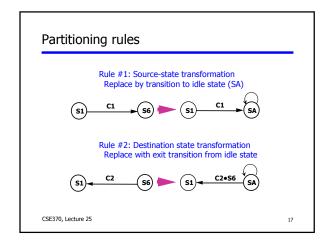

### Mealy versus Moore partitions

- Mealy machines undesirable

- Inputs can affect outputs immediately

Lambda "output" can be a handoff to another machine!!!

- Inputs can ripple through several machines in one clock cycle

- Moore or synchronized Mealy desirable

- Input-to-output path always broken by a flip-flop

- But...may take several clocks for input to propagate to output ✓ Output may derive from other side of a partition

19

21

23

CSE370, Lecture 25

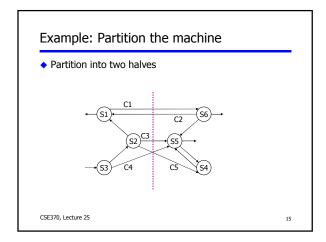

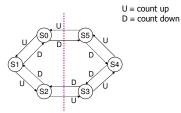

### Example: Six-state up/down counter

Break into 2 parts

20

24

CSE370, Lecture 25

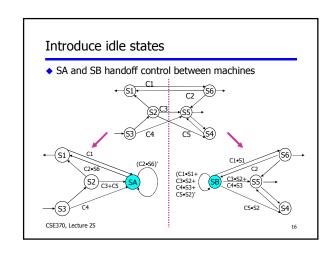

### Example: 6 state up/down counter (con't)

- ◆ Count sequence S<sub>0</sub>, S<sub>1</sub>, S<sub>2</sub>, S<sub>3</sub>, S<sub>4</sub>, S<sub>5</sub>

- S<sub>2</sub> goes to S<sub>A</sub> and holds, leaves after S<sub>5</sub>

- S<sub>5</sub> goes to S<sub>B</sub> and holds, leaves after S<sub>2</sub>

- Down sequence is similar

Minimize communication between partitions

- ◆ Ideal world: Two machines handoff control

- Separate I/O, states, etc.

- ◆ Real world: Minimize handoffs and common I/O

- Minimize number of state bits that cross boundary

- Merge common outputs

- Look for:

- Disjoint inputs used in different regions of state diagram

- Outputs active in only one region of state diagramIsomorphic portions of state diagram

- Add states, if necessary, to make them so

- Regions of diagram with a single entry and single exit point

CSE370, Lecture 25 22

### Sequential logic: What you should know

- Sequential logic building blocks

- Latches (R-S and D)

- Flip-flops (master/slave D, edge-triggered D & T)

- Latch and flip-flop timing (setup/hold time, prop delay)

- Timing diagrams

- Flip-flop clocking

- Asynchronous inputs and metastability

- Registers

Sequential logic: What you should know

- Counters

- Timing diagrams

- Shift registers

- Ripple counters

- State diagrams and state-transition tables

- Counter design procedure

Draw a state diagram

- 2. Draw a state-transition table

- 3. Encode the next-state functions4. Implement the design

- Self-starting counters

CSE370, Lecture 25

CSE370, Lecture 25

## Sequential logic: What you should know

- Finite state machines

- FINITE STATE MACHINES

Timing diagrams (synchronous FSMs)

Moore versus Mealy versus registered Mealy

FSM design procedure

1. Understand the problem (state diagram & state-transition table)

2. Determine the machine's states (minimize the state diagram)

3. Encode the machine's states (state assignment)

4. Design the next-state logic (minimize the combinational logic)

5. Implement the FSM

FSM design quidelines

- FSM design guidelines

# Separate datapath and control

One-hot encoding

Pipelining and retiming basics

CSE370, Lecture 25

25