# CSE 370 Spring 2006 Introduction to Digital Design Lecture 25: Computer Organization

Last Lecture Design Examples

#### Today

Computer Organization

#### Administrivia

Homework 9 out. Due June 2.

The following is a state transition table for a FSM which takes as input one bit, X and outputs one bit O. The machine is a Moore machine.

| Current State                                                        | Current O                                                                                   | Next Sta<br>X=0    | te<br>X=1                        |                                                 |

|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------|----------------------------------|-------------------------------------------------|

| S1                                                                   | 0                                                                                           | S2                 | S4                               |                                                 |

| S2                                                                   | 0                                                                                           | S2                 | S7                               | <i>sι <sup>≡</sup> 5ς</i><br>55 <sup>=5</sup> 2 |

| S3                                                                   | 0                                                                                           | S7                 | S4                               | 6 - 55                                          |

| S4                                                                   | 1                                                                                           | S3                 | S6                               | 22=25                                           |

| S5                                                                   | 0                                                                                           | S2                 | S4                               | 11                                              |

| S6                                                                   | 0                                                                                           | S7                 | S4                               | v                                               |

| S7                                                                   | 1                                                                                           | S6                 | S3                               | $S_1 \equiv S_2$                                |

| 52<br>53<br>54<br>54<br>55<br>54<br>54<br>54<br>54<br>54<br>54<br>54 | 2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2 | ST E<br>St E<br>St | - 55 = 5<br>= 52<br>= 52<br>- 57 | 2                                               |

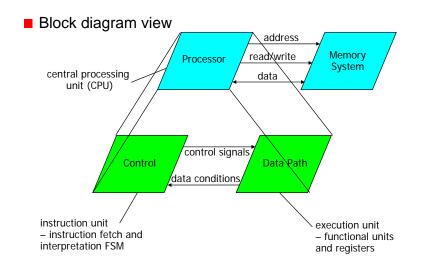

#### **Computer organization**

- Computer design an application of digital logic design procedures

- Computer = processing unit + memory system

- Processing unit = control + datapath

- Control = finite state machine

- inputs = machine instruction, datapath conditions

- outputs = register transfer control signals, ALU operation codes

- instruction interpretation = instruction fetch, decode, execute

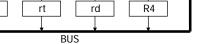

- Datapath = functional units + registers

- functional units = ALU, multipliers, dividers, etc.

- registers = program counter, shifters, storage registers

#### Structure of a computer

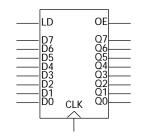

#### Registers

- Selectively loaded EN or LD input

- Output enable OE input

- Multiple registers group 4 or 8 in parallel

OE asserted causes FF state to be connected to output pins; otherwise they are left unconnected (high impedance)

LD asserted during a lo-to-hi clock transition loads new data into FFs

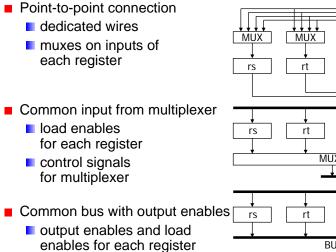

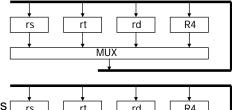

## **Register transfer**

|    |    | MUX |    |

|----|----|-----|----|

| rs | rt | rd  | R4 |

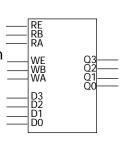

# **Register files**

- Collections of registers in one package

- two-dimensional array of FFs

- address used as index to a particular word

- can have separate read and write addresses so can do both at same time

- 4 by 4 register file

- 16 D-FFs

- organized as four words of four bits each

- write-enable (load)

- read-enable (output enable)

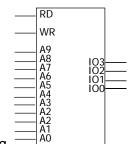

# **Memories**

- Larger collections of storage elements

- implemented not as FFs but as much more efficient latches

- high-density memories use 1 to 5 switches (transitors) per memory bit

- Static RAM 1024 words each 4 bits wide

- once written, memory holds forever (not true for denser dynamic RAM)

- address lines to select word (10 lines for 1024 words)

- read enable

- same as output enable

- often called chip select

- permits connection of many chips into larger array

- write enable (same as load enable)

- bi-directional data lines

- output when reading, input when writing

# **Instruction types**

- Data manipulation

- add, subtract

- increment, decrement

- multiply

- shift, rotate

- immediate operands

- Data staging

- Ioad/store data to/from memory

- register-to-register move

- Control

- conditional/unconditional branches in program flow

- subroutine call and return

# Instruction sequencing

- Example an instruction to add the contents of two registers (Rx and Ry) and place result in a third register (Rz)

- Step 1: get the ADD instruction from memory into an instruction register

- Step 2: decode instruction

- instruction in IR has the code of an ADD instruction

- register indices used to generate output enables for registers Rx and Ry

- register index used to generate load signal for register Rz

- Step 3: execute instruction

- enable Rx and Ry output and direct to ALU

- setup ALU to perform ADD operation

- direct result to Rz so that it can be loaded into register

# Elements of the control unit (aka instruction unit)

- Standard FSM elements

- state register

- next-state logic

- output logic (datapath/control signalling)

- Moore or synchronous Mealy machine to avoid loops unbroken by FF

- Plus additional "control" registers

- instruction register (IR)

- program counter (PC)

- Inputs/outputs

- outputs control elements of data path

- inputs from data path used to alter flow of program (test if zero)

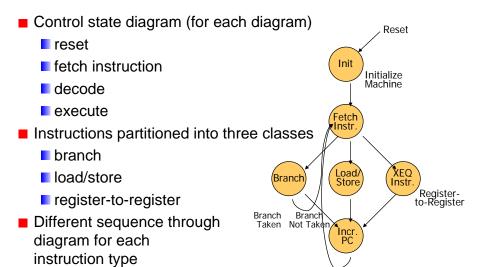

## **Instruction execution**

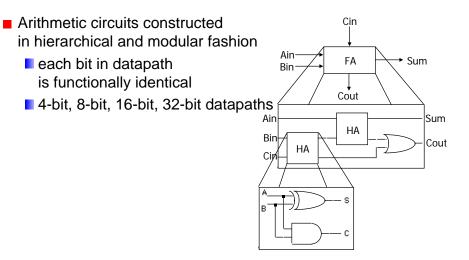

# Data path (hierarchy)

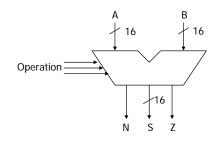

# Data path (ALU)

- ALU block diagram

- input: data and operation to perform

- output: result of operation and status information

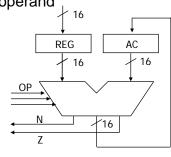

# Data path (ALU + registers)

- Accumulator

- special register

- one of the inputs to ALU

- output of ALU stored back in accumulator

- One-address instructions

- operation and address of one operand

- other operand and destination is accumulator register

- AC <- AC op Mem[addr]</p>

- "single address instructions" (AC implicit operand)

- Multiple registers

- part of instruction used to choose register operands

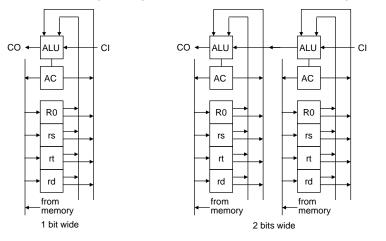

# Data path (bit-slice)

Bit-slice concept – replicate to build n-bit wide datapaths

## **Instruction path**

- Program counter (PC)

- keeps track of program execution

- address of next instruction to read from memory

- may have auto-increment feature or use ALU

- Instruction register (IR)

- current instruction

- includes ALU operation and address of operand

- also holds target of jump instruction

- immediate operands

- Relationship to data path

- PC may be incremented through ALU

- contents of IR may also be required as input to ALU immediate operands

# Data path (memory interface)

- Memory

- separate data and instruction memory (Harvard architecture)

- ■two address busses, two data busses

- single combined memory (Princeton architecture)

single address bus, single data bus

#### Separate memory

- ALU output goes to data memory input

- register input from data memory output

- data memory address from instruction register

- instruction register from instruction memory output

- instruction memory address from program counter

- Single memory

- address from PC or IR

- memory output to instruction and data registers

- memory input from ALU output

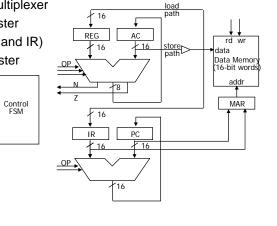

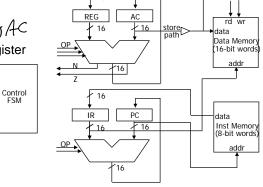

# Block diagram of processor (Harvard)

- Register transfer view of Harvard architecture

- which register outputs are connected to which register inputs

- arrows represent data-flow, other are control signals from control FSM

- two MARs (PC and IR)

- two MBRs (REG and IR) /+C

- load control for each register

# Block diagram of processor (Princeton)

- Register transfer view of Princeton architecture

- which register outputs are connected to which register inputs

- arrows represent data-flow, other are control signals from control FSM

- MAR may be a simple multiplexer

- rather than separate register

- MBR is split in two (REG and IR)

- load control for each register