#### Finite State Machines

- Sequential circuits

- primitive sequential elements

- combinational logic

- Models for representing sequential circuits

- finite-state machines (Moore and Mealy)

- Basic sequential circuits revisited

- shift registers

- counters

- Design procedure

- state diagrams

- state transition table

- next state functions

- Hardware description languages

Autumn 2003

CSE370 - VII - Finite State Machines

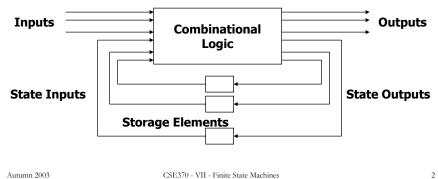

#### Abstraction of state elements

- Divide circuit into combinational logic and state

- Localize the feedback loops and make it easy to break cycles

- Implementation of storage elements leads to various forms of sequential logic

Autumn 2003

CSE370 - VII - Finite State Machines

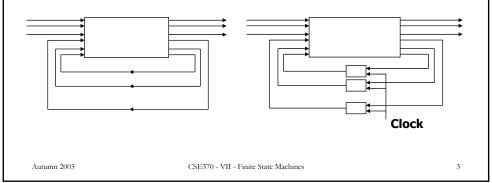

# Forms of sequential logic

- Asynchronous sequential logic state changes occur whenever state inputs change (elements may be simple wires or delay elements)

- Synchronous sequential logic state changes occur in lock step across all storage elements (using a periodic waveform - the clock)

#### Finite state machine representations

- States: determined by possible values in sequential storage elements

- Transitions: change of state

- Clock: controls when state can change by controlling storage elements

- Sequential logic

- sequences through a series of states

- based on sequence of values on input signals

- clock period defines elements of sequence

Autumn 2003

CSE370 - VII - Finite State Machines

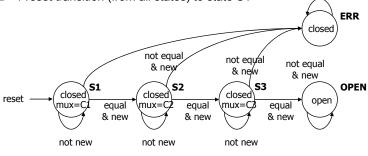

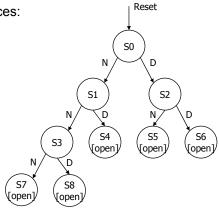

## Example finite state machine diagram

- Combination lock from introduction to course

- 5 states

- 5 self-transitions

- 6 other transitions between states

- 1 reset transition (from all states) to state S1

Autumn 2003

CSE370 - VII - Finite State Machines

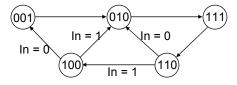

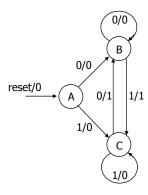

# Can any sequential system be represented with a state diagram?

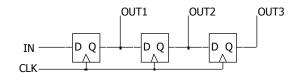

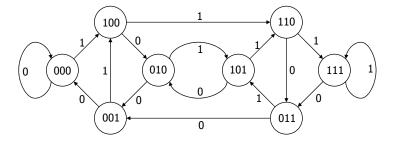

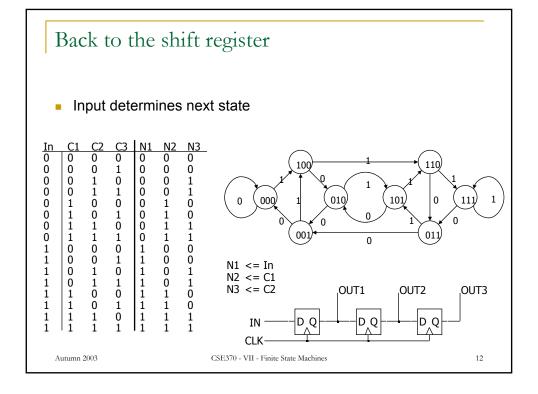

- Shift register

- input value shown on transition arcs

- output values shown within state node

Autumn 2003

CSE370 - VII - Finite State Machines

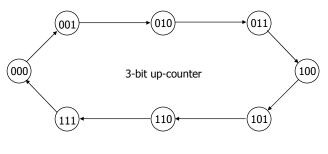

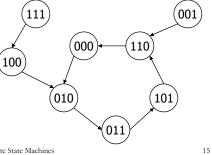

#### Counters are simple finite state machines

- Counters

- proceed through well-defined sequence of states in response to enable

- Many types of counters: binary, BCD, Gray-code

- □ 3-bit up-counter: 000, 001, 010, 011, 100, 101, 110, 111, 000, ...

- □ 3-bit down-counter: 111, 110, 101, 100, 011, 010, 001, 000, 111, ...

Autumn 2003

CSE370 - VII - Finite State Machines

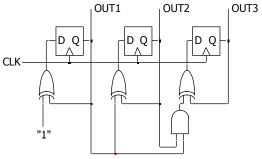

## How do we turn a state diagram into logic?

- Counter

- 3 flip-flops to hold state

- logic to compute next state

- clock signal controls when flip-flop memory can change

- wait long enough for combinational logic to compute new value

- don't wait too long as that is low performance

Autumn 2003

CSE370 - VII - Finite State Machines

## FSM design procedure

- Start with counters

- simple because output is just state

- simple because no choice of next state based on input

- State diagram to state transition table

- tabular form of state diagram

- like a truth-table

- State encoding

- decide on representation of states

- for counters it is simple: just its value

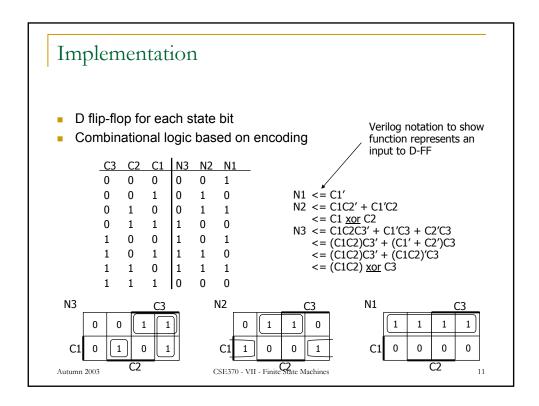

- Implementation

- flip-flop for each state bit

- combinational logic based on encoding

Autumn 2003

CSE370 - VII - Finite State Machines

0

# FSM design procedure: state diagram to encoded state transition table

- Tabular form of state diagram

- Like a truth-table (specify output for all input combinations)

- Encoding of states: easy for counters just use value

| current state |     | next state |   |  |

|---------------|-----|------------|---|--|

| 0             | 000 | 001        | 1 |  |

| 1             | 001 | 010        | 2 |  |

| 2             | 010 | 011        | 3 |  |

| 3             | 011 | 100        | 4 |  |

| 4             | 100 | 101        | 5 |  |

| 5             | 101 | 110        | 6 |  |

| 6             | 110 | 111        | 7 |  |

| 7             | 111 | 000        | 0 |  |

Autumn 2003

CSE370 - VII - Finite State Machines

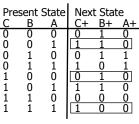

#### More complex counter example

- Complex counter

- repeats 5 states in sequence

- not a binary number representation

- Step 1: derive the state transition diagram

- count sequence: 000, 010, 011, 101, 110

- Step 2: derive the state transition table from the state transition diagram

| Present State              |                            |                            | Nex<br>C+                       | t Stat                               | te<br>Δ±                        |

|----------------------------|----------------------------|----------------------------|---------------------------------|--------------------------------------|---------------------------------|

| 0<br>0<br>0<br>0<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0 | 0<br>1<br>0<br>1<br>0<br>1 | 0<br>-<br>0<br>1<br>-<br>1<br>0 | 1<br>-<br>1<br>0<br>-<br>1<br>0<br>- | 0<br>-<br>1<br>1<br>-<br>0<br>0 |

$_{Autumn~2003}$  note the don't care conditions that arise from the unused state codes  $_{CSE370^{\circ}}$  VIII - Finite State Machines

13

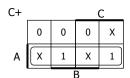

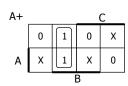

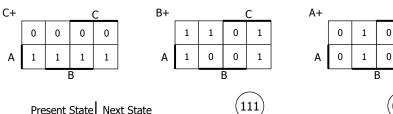

## More complex counter example (cont'd)

Step 3: K-maps for next state functions

$$B+ <= B' + A'C'$$

Autumn 2003

CSE370 - VII - Finite State Machines

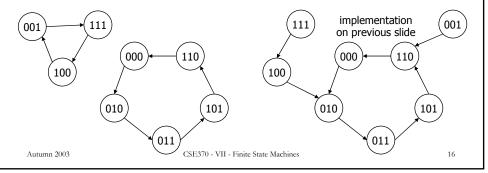

# Self-starting counters (cont'd)

Re-deriving state transition table from don't care assignment

0

0

Autumn 2003

CSE370 - VII - Finite State Machines

## Self-starting counters

- Start-up states

- at power-up, counter may be in an unused or invalid state

- designer must guarantee that it (eventually) enters a valid state

- Self-starting solution

- design counter so that invalid states eventually transition to a valid state

- may limit exploitation of don't cares

# Activity

- 2-bit up-down counter (2 inputs)

- □ direction: D = 0 for up, D = 1 for down

- □ count: C = 0 for hold, C = 1 for count

Autumn 2003

CSE370 - VII - Finite State Machines

Activity (cont'd)

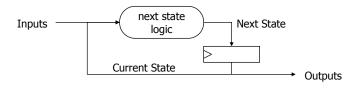

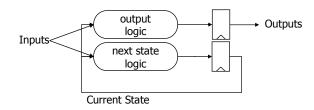

# Counter/shift-register model

- Values stored in registers represent the state of the circuit

- Combinational logic computes:

- next state

- function of current state and inputs

- outputs

- values of flip-flops

Autumn 2003

CSE370 - VII - Finite State Machines

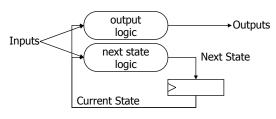

#### General state machine model

- Values stored in registers represent the state of the circuit

- Combinational logic computes:

- next state

- function of current state and inputs

- outputs

- function of current state and inputs (Mealy machine)

- function of current state only (Moore machine)

Autumn 2003

CSE370 - VII - Finite State Machines

20

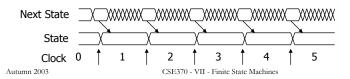

#### State machine model (cont'd)

- States: S<sub>1</sub>, S<sub>2</sub>, ..., S<sub>k</sub>

- Inputs: I<sub>1</sub>, I<sub>2</sub>, ..., I<sub>m</sub>

- Outputs: O<sub>1</sub>, O<sub>2</sub>, ..., O<sub>n</sub>

- Transition function: F<sub>s</sub>(S<sub>i</sub>, I<sub>i</sub>)

- Output function:  $F_o(S_i)$  or  $F_o(S_i, I_j)$  output logic next state logic Next State

21

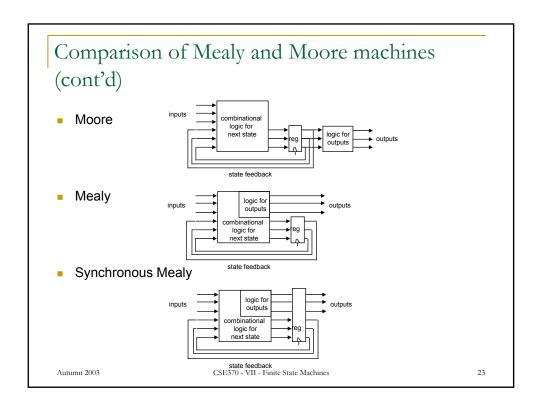

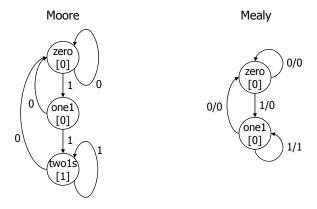

#### Comparison of Mealy and Moore machines

- Mealy machines tend to have less states

- different outputs on arcs (n²) rather than states (n)

- Moore machines are safer to use

- outputs change at clock edge (always one cycle later)

- in Mealy machines, input change can cause output change as soon as logic is done – a big problem when two machines are interconnected – asynchronous feedback may occur if one isn't careful

- Mealy machines react faster to inputs

- react in same cycle don't need to wait for clock

- in Moore machines, more logic may be necessary to decode state into outputs – more gate delays after clock edge

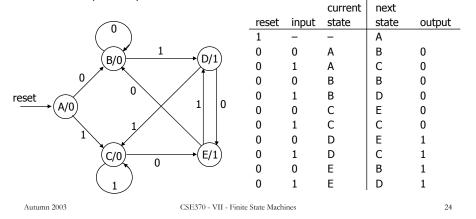

# Specifying outputs for a Moore machine

- Output is only function of state

- specify in state bubble in state diagram

- example: sequence detector for 01 or 10

# Specifying outputs for a Mealy machine

- Output is function of state and inputs

- specify output on transition arc between states

- example: sequence detector for 01 or 10

|             |             | current     | next        |             |

|-------------|-------------|-------------|-------------|-------------|

| reset       | input       | state       | state       | output      |

| 1           | -           | -           | Α           | 0           |

| 0           | 0           | Α           | В           | 0           |

| 0           | 1           | Α           | С           | 0           |

| 0           | 0           | В           | В           | 0           |

| 0           | 1           | В           | С           | 1           |

| 0           | 0           | С           | В           | 1           |

| 0           | 1           | С           | С           | 0           |

|             |             |             |             |             |

| 0<br>0<br>0 | 0<br>1<br>0 | B<br>B<br>C | B<br>C<br>B | 0<br>1<br>1 |

Autumn 2003

CSE370 - VII - Finite State Machines

25

## Registered Mealy machine (really Moore)

- Synchronous (or registered) Mealy machine

- registered state AND outputs

- avoids 'glitchy' outputs

- easy to implement in PLDs

- Moore machine with no output decoding

- outputs computed on transition to next state rather than after entering

- view outputs as expanded state vector

Autumn 2003

CSE370 - VII - Finite State Machines

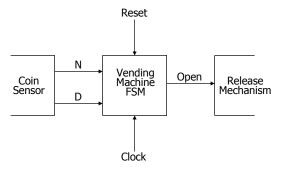

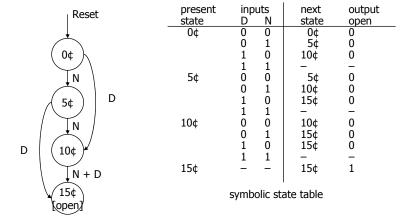

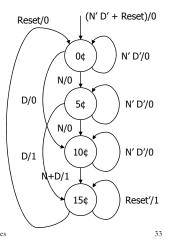

## Example: vending machine

- Release item after 15 cents are deposited

- Single coin slot for dimes, nickels

- No change

Autumn 2003

CSE370 - VII - Finite State Machines

#### Example: vending machine (cont'd)

- Suitable abstract representation

- tabulate typical input sequences:

- 3 nickels

- nickel, dime

- dime, nickel

- two dimes

- draw state diagram:

- inputs: N, D, reset

- output: open chute

- assumptions:

- assume N and D asserted for one cycle

- each state has a self loop for N = D = 0 (no coin)

Autumn 2003

CSE370 - VII - Finite State Machines

28

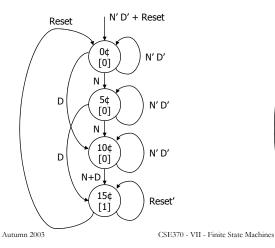

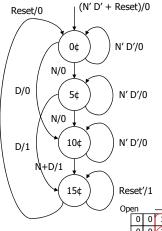

# Example: vending machine (cont'd)

Minimize number of states - reuse states whenever possible

Autumn 2003 CSE370 - VII - Finite State Machines

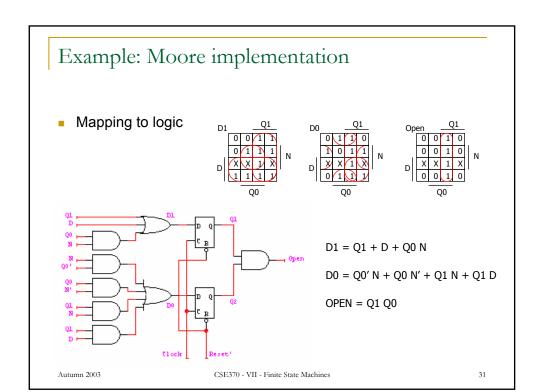

Example: vending machine (cont'd)

Uniquely encode states

| present stateQ1_Q0 | inputs<br>D N | next state<br>D1 D0 | output<br>open |

|--------------------|---------------|---------------------|----------------|

| 0 0                | 0 0           | 0 0                 | 0              |

|                    | 0 1           | 0 1                 | 0              |

|                    | 1 0           | 1 0                 | 0              |

|                    | 1 1           |                     |                |

| 0 1                | 0 0           | 0 1                 | 0              |

|                    | 0 1           | 1 0                 | 0              |

|                    | 1 0           | 1 1                 | 0              |

|                    | 1 1           |                     |                |

| 1 0                | 0 0           | 1 0                 | 0              |

|                    | 0 1           | 1 1                 | 0              |

|                    | 1 0           | 1 1                 | 0              |

|                    | 1 1           |                     | _              |

| 1 1                |               | 1 1                 | 1              |

Autumn 2003

CSE370 - VII - Finite State Machines

30

# Example: vending machine (cont'd)

#### One-hot encoding

| present state | inputs | next state output |                              |

|---------------|--------|-------------------|------------------------------|

| Q3 Q2 Q1 Q0   | D N    | D3 D2 D1 D0 open  |                              |

| 0 0 0 1       | 0 0    | 0 0 0 1 0         | D0 = Q0 D' N'                |

|               | 0 1    | 0 0 1 0 0         | 20 402 11                    |

|               | 1 0    | 0 1 0 0 0         |                              |

|               | 1 1    |                   | D1 = Q0 N + Q1 D' N'         |

| 0 0 1 0       | 0 0    | 0 0 1 0 0         |                              |

|               | 0 1    | 0 1 0 0 0         | D2 = Q0 D + Q1 N + Q2 D' N'  |

|               | 1 0    | 1 0 0 0 0         | 52                           |

|               | 1 1    |                   |                              |

| 0 1 0 0       | 0 0    | 0 1 0 0 0         | D3 = Q1 D + Q2 D + Q2 N + Q3 |

|               | 0 1    | 1 0 0 0 0         |                              |

|               | 1 0    | 1 0 0 0 0         | OPEN = Q3                    |

|               | 1 1    |                   | S. E.I. QS                   |

| 1 0 0 0       |        | 1 0 0 0 1         |                              |

Autumn 2003

CSE370 - VII - Finite State Machines

# Equivalent Mealy and Moore state diagrams

- Moore machine

- outputs associated with state

- Mealy machine

- outputs associated with transitions

# Example: Mealy implementation

| present state | inputs |   | next state |    | output |

|---------------|--------|---|------------|----|--------|

| Q1 Q0         | D      | N | D1         | D0 | open   |

| 0 0           | 0      | 0 | 0          | 0  | 0      |

|               | 0      | 1 | 0          | 1  | 0      |

|               | 1      | 0 | 1          | 0  | 0      |

|               | 1      | 1 | _          | _  |        |

| 0 1           | 0      | 0 | 0          | 1  | 0      |

|               | 0      | 1 | 1          | 0  | 0      |

|               | 1      | 0 | 1          | 1  | 1      |

|               | 1      | 1 | –          | _  | -      |

| 1 0           | 0      | 0 | 1          | 0  | 0      |

|               | 0      | 1 | 1          | 1  | 1      |

|               | 1      | 0 | 1          | 1  | 1      |

|               | 1      | 1 | –          | _  | _      |

| 1 1           | _      | _ | 1          | 1  | 1      |

|               |        |   | ı          |    |        |

Autumn 2003 QCSE370 - VII - Finite State Machines

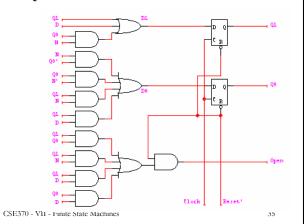

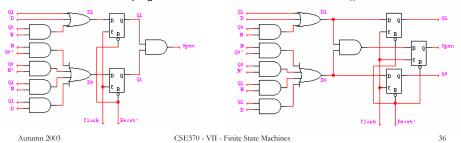

# Example: Mealy implementation

D0 =

$$Q0'N + Q0N' + Q1N + Q1D$$

D1 =  $Q1 + D + Q0N$

$$OPEN = Q1Q0 + Q1N + Q1D + Q0D$$

Autumn 2003

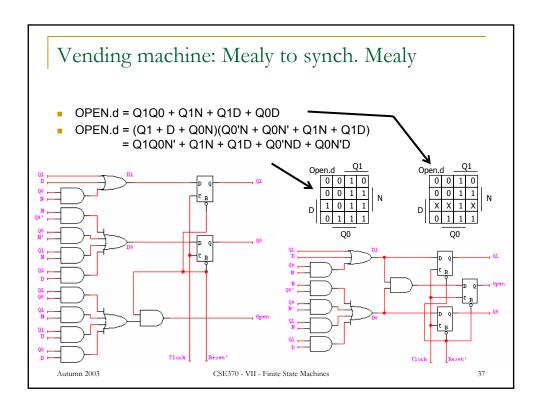

## Vending machine: Moore to synch. Mealy

- OPEN = Q1Q0 creates a combinational delay after Q1 and Q0 change in Moore implementation

- This can be corrected by retiming, i.e., move flip-flops and logic through each other to improve delay

- OPEN.d = (Q1 + D + Q0N)(Q0'N + Q0N' + Q1N + Q1D) = Q1Q0N' + Q1N + Q1D + Q0'ND + Q0N'D

- Implementation now looks like a synchronous Mealy machine

- it is common for programmable devices to have FF at end of logic

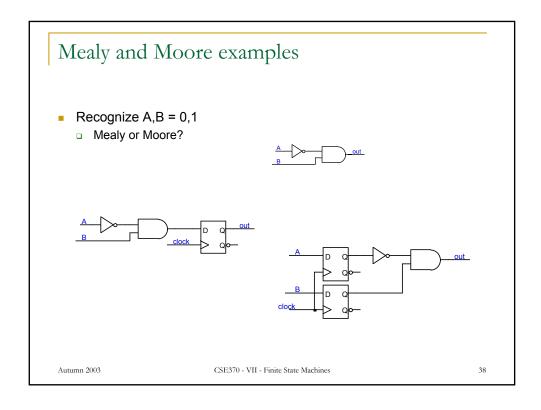

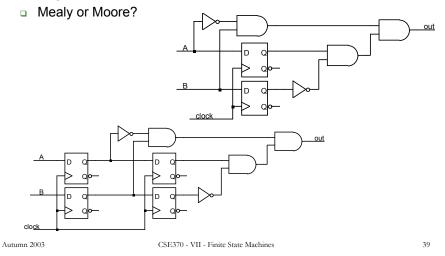

## Mealy and Moore examples (cont'd)

Recognize A,B = 1,0 then 0,1

# Hardware Description Languages and Sequential Logic

- Flip-flops

- representation of clocks timing of state changes

- asynchronous vs. synchronous

- FSMs

- structural view (FFs separate from combinational logic)

- behavioral view (synthesis of sequencers not in this course)

- Data-paths = data computation (e.g., ALUs, comparators) + registers

- use of arithmetic/logical operators

- control of storage elements

#### Example: reduce-1-string-by-1

Remove one 1 from every string of 1s on the input

CSE370 - VII - Finite State Machines Autumn 2003

## Verilog FSM - Reduce 1s example

Moore machine

```

parameter zero = 2'b00;

parameter one1 = 2'b01;  state assignment (easy to change, if in one place)

parameter two1s = 2'b10;

module reduce (clk, reset, in, out);

input clk, reset, in;

output out;

reg [2:1] state; // state variables

reg [2:1] next_state;

always @(posedge clk)

if (reset) state = zero;

```

Autumn 2003

CSE370 - VII - Finite State Machines

42

## Moore Verilog FSM (cont'd)

```

always @(in or state) ←

crucial to include

case (state)

all signals that are

zero:

input to state determination

// last input was a zero

begin

if (in) next_state = one1;

else next_state = zero;

end

note that output

one1:

// we've seen one 1

depends only on state

begin

if (in) next_state = two1s;

next state = zero;

end

two1s:

always @(state)

// we've seen at least 2 ones

case (state)

begin

zero: out = 0;

if (in) next_state = two1s;

one1: out = 0;

next state = zero;

two1s: out = 1;

end

endcase

endcase

endmodule

Autumn 2003

CSE370 - VII - Finite State Machines

```

43

44

#### Mealy Verilog FSM

```

module reduce (clk, reset, in, out);

input clk, reset, in;

output out;

reg out;

reg state; // state variables

reg next_state;

always @(posedge clk)

if (reset) state = zero;

0/0

state = next_state;

zero

[0]

always @(in or state)

case (state)

1/0

// last input was a zero

zero:

begin

one1

out = 0;

[0]

if (in) next_state = one;

1/1

else next_state = zero;

// we've seen one 1

one:

if (in) begin

next_state = one; out = 1;

end else begin

next_state = zero; out = 0;

endcase

endmodule

Autumn 2003

CSE370 - VII - Finite State Machines

```

#### Synchronous Mealy Machine

```

module reduce (clk, reset, in, out);

input clk, reset, in;

output out;

reg out;

reg state; // state variables

always @(posedge clk)

if (reset) state = zero;

else

case (state)

zero: // last input was a zero

begin

out = 0;

if (in) state = one;

else state = zero;

// we've seen one 1

one:

if (in) begin

state = one; out = 1;

end else begin

state = zero; out = 0;

end

endcase

endmodule

Autumn 2003

CSE370 - VII - Finite State Machines

```

Finite state machines summary

- Models for representing sequential circuits

- abstraction of sequential elements

- finite state machines and their state diagrams

- inputs/outputs

- Mealy, Moore, and synchronous Mealy machines

- Finite state machine design procedure

- deriving state diagram

- deriving state transition table

- determining next state and output functions

- implementing combinational logic

- Hardware description languages

Autumn 2003

CSE370 - VII - Finite State Machines

46