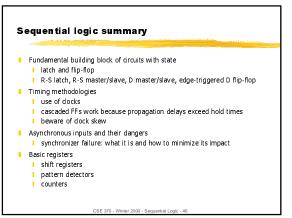

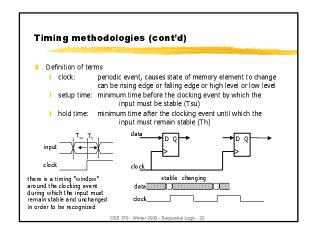

# Timing methodologies Rules for interconnecting components and clocks guarantee proper operation of system when strictly followed Approach depends on building blocks used for memory elements we'll focus on systems with edge-triggered flip-flops found in programmable logic devices many custom integrated circuits focus on level-sensitive latches Basic rules for correct timing: (1) correct inputs, with respect to time, are provided to the flip-flops (2) no flip-flop changes state more than once per clocking event

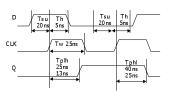

# Typical timing specifications

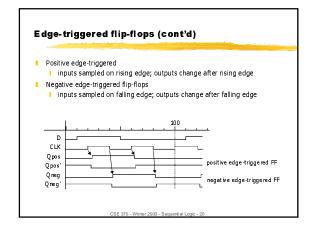

- Positive edge-triggered D flip-flop

- setup and hold times

- minimum clock width

- propagation delays (low to high, high to low, max and typical)

all measurements are made from the clocking event that is, the rising edge of the  $\mbox{clock}$

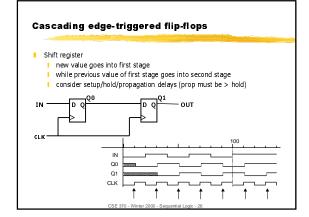

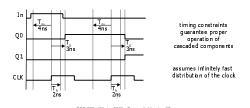

# Cascading edge-triggered flip-flops (cont'd)

- Why this works

- propagation delays exceed hold times

- clock width constraint exceeds setup time

- this guarantees following stage will  ${\rm \dot{a}}$  latch current value before it changes to new value

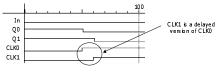

# Clock skew

### The problem

- correct behavior assumes next state of all storage elements

- determined by all storage elements at the same time this is difficult in high-performance systems because time for clock to arrive at flip-flop is comparable to delays through logic

- effect of skew on cascaded flip-flops:

original state: IN = 0, Q0 = 1, Q1 = 1 due to skew, next state becomes: Q0 = 0, Q1 = 0, and not Q0 = 0, Q1 = 1

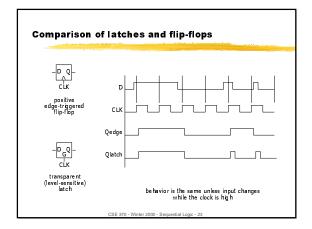

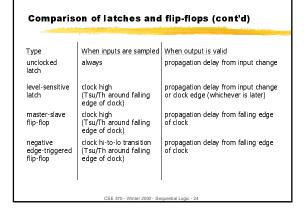

# Summary of latches and flip-flops

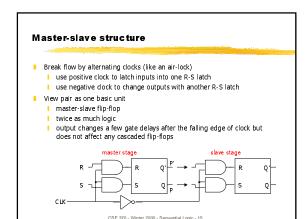

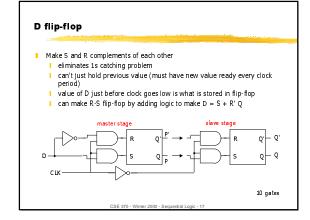

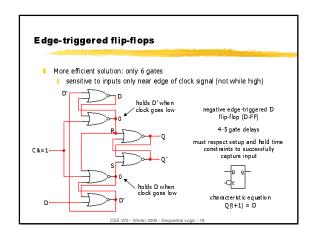

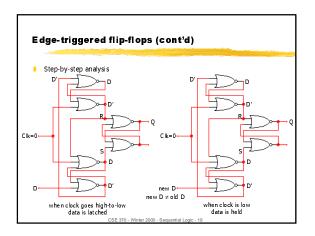

- Development of D-FF

- I level-sensitive used in custom integrated circuits can be made with 4 switches

- edge-triggered used in programmable logic devices

- good choice for data storage register

- Historically J-K FF was popular but now never used

- similar to R-S but with 1-1 being used to toggle output (complement state)

- good in days of TTL/SSI (more complex input function: D = JQ' + K'Q

- not a good choice for PALs/PLAs as it requires 2 inputs

- can always be implemented using D-FF

- Preset and clear inputs are highly desirable on flip-flops

- used at start-up or to reset system to a known state

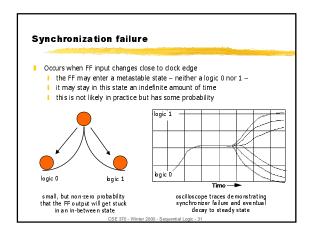

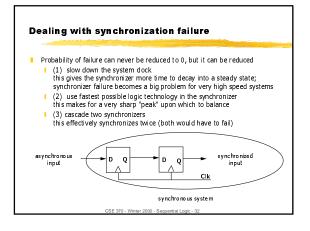

# Metastability and asynchronous inputs

- Clocked synchronous circuits

- I inputs, state, and outputs sampled or changed in relation to a common reference signal (called the clock)

- e.g., master/slave, edge-triggered

- Asynchronous circuits

- inputs, state, and outputs sampled or changed independently of a common reference signal (glitches/hazards a major concern)

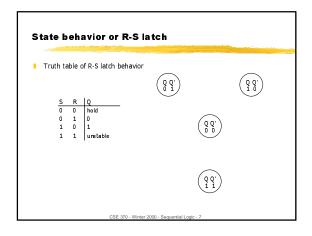

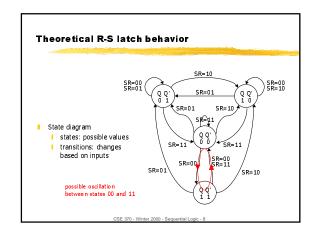

- e.g., R-S latch

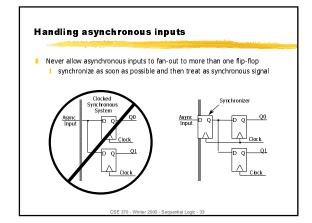

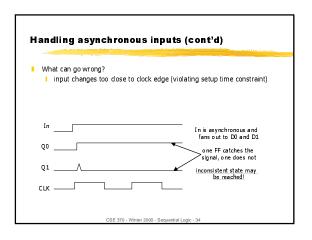

- Asynchronous inputs to synchronous circuits

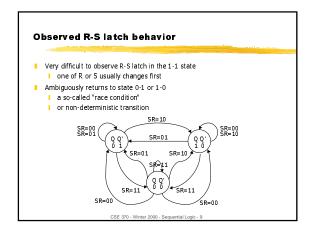

- inputs can change at any time, will not meet setup/hold times

- dangerous, synchronous inputs are greatly preferred

- cannot be avoided (e.g., reset signal, memory wait, user input)

# Flip-flop features Reset (set state to 0) - R synchronous: Dnew = R' • Dold (when next clock edge arrives) asynchronous: doesn't wait for clock, quick but dangerous ■ Preset or set (set state to 1) – S (or sometimes P) synchronous: Dnew = Dold + S (when next clock edge arrives) asynchronous: doesn't wait for clock, quick but dangerous Both reset and preset I Dnew = R' • Dold + S (set-dominant) I Dnew = R' • Dold + R'S (reset-dominant) ■ Selective input capability (input enable or load) – LD or EN I multiplexor at input: Dnew = LD' • Q + LD • Dold I load may or may not override reset/set (usually R/S have priority) ■ Complementary outputs - Q and Q'