Lab 4: High-Level Verilog

Overview

Implementing designs directly in schematics or structural (gate-level) Verilog can give you the best control, and often the smallest designs. But, sometimes it can be a real pain to optimize all the way down at that level. An alternative is high-level (Register Transfer Level – RTL) Verilog, where you tell the CAD tools what you what the output to look like, and it automatically does the Boolean algebra for you!

Instructions

Task 1 – Seven-Segment Displays

In lecture, we presented a seven-segment display driver. RTL code for that seven-segment display is given above (code).

- Create a new project in Quartus Prime and add the seg7 code to it.

- Create a new module that uses two instances of the seg7 code – one that uses SW3-SW0 as inputs and outputs to HEX0, and another that uses SW7-SW4 as inputs and outputs to HEX1.

Task 2 – UPC Code to Display

In Lab 3, we built a system that took in a UPC and output whether a returned Nordstrom item was on sale for a discount and whether it was stolen. A nearby store, McCluskey's Pawn Shop, buys used items from customers that were originally purchased from various stores that also use the UPC system. Old Mr. McCluskey wants a similar item-checking system, but has found that devious customers are changing the UPC stickers on the items they are selling to misrepresent the price. To combat that, Mr. McCluskey would like you to add a display on HEX5-HEX0 that describes the product corresponding to that UPC – if the description doesn't match the item, then someone is trying to cheat Mr. McCluskey!

- Come up with exactly six new items to fill out the

leftmost column of the table below – three expensive items and

three inexpensive items.

You are not allowed to use any of the items from Lab 3 or

the example given below. You are also not allowed to change any of the values in the "expensive" or "discounted" columns. Just change the names.

- Since we only have six 7-segment displays, you should consider what items will lend themselves to "good" (easily-distinguishable) displays.

Item NameUPCDiscounted?Expensive?<New Item 1>0 0 0NoYes<New Item 2>0 0 1NoNo<New Item 3>0 1 1YesNo<New Item 4>1 0 0NoYes<New Item 5>1 0 1YesYes<New Item 6>1 1 0YesNo - Determine corresponding 7-segment encodings for

your six items.

The displays do not need to use the entire item name, but they need

to be at least 3 letters each and easily-distinguishable from the

other UPC descriptions.

You may use upper- and lower-case letters or pictograms.

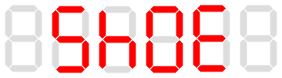

- Example: The item "Dress Shoe" could be displayed as

There is no "correct" way to encode the entire alphabet on 7-segment displays. You may use online resources such as http://tinyurl.com/h99785g or https://www.youtube.com/watch?v=RTB5XhjbgZA for inspiration, but you should decide for yourself whether or not your display is easily read or more of a stretch to interpret correctly. - Example: The item "Dress Shoe" could be displayed as

- Draw a block diagram for a circuit that implements the above functionality.

It should be called

UpcDisplayand have three inputs (U, P, and C), similar to the seg7 module, but will instead have six 7-bit outputs for the 7-seg displays. Each output should be driven by a 7-bit 6-to-1 multiplexor, illustrated with standard "trapezoid" notation. Be sure to label the select value for each mux inputs and indicate the bit width of every bus in your diagram. If you're unsure whether you're using correct notation, ask your course staff. - Translate your circuit diagram to RTL code in Verilog, using case statements to implement your diagram's multiplexors.

- Simulate your module thoroughly in ModelSim to make sure it works.

- In your lab's top level module, instantiate your

UpcDisplaymodule alongside your Lab 3'sNordstrommodule. The design should use them both so the system simultaneously computes the Discounted LED, Stolen LED, and HEX displays. Test and debug with ModelSim, then load onto your board.

- Signals from multiple modules can be displayed at the same time. Select modules in the sim tab and then drag-and-drop signals from the Objects pane to the Wave pane.

- To (re-)order signals, you can click and drag names in the Wave pane.

- You can create groups of signals. Highlight multiple signals in the Wave pane, then right-click on one of the signal names and select "Group." You can now move the signals as a group, and hide/expose them easily. Note: You can only group signals from the same module.

- Don't forget to save the formatting into the <modulename>_wave.do file!

Task 3 – Don't Cares

Your design has outputs for only 6 of the 8 possible UPC codes. For the other two cases, a line such as "default: LEDs = 7'bX;" tells Quartus Prime that it can treat these cases as a Don't Care condition. If you didn't do this, go back and correct it to do so. Test your design on the circuit board, and record the pattern it shows for these Don't Care conditions (hand drawn or photo will work).

Lab Requirements

Lab Report

Due before Wednesday section, submitted as a PDF on .

- Your completed item table, showing your new items, their UPC codes, and classifications.

- Your

UpcDisplaymodule's block diagram - A screenshot of the ModelSim simulations you will demonstrate during the demo.

- Drawings of the 7-seg display output for each of the unused UPC codes.

- How many hours (estimated) it took to complete this lab in total, including reading, planning, designing, coding, debugging, and testing.

- Separately, upload the SystemVerilog code for your the double 7-seg and McCluskey's Pawn Shop designs and related test bench(es).

Lab Demo

Due by the end of the day on Friday, but typically during your assigned demo slot or a scheduled support hour.

- Demonstrate both the double 7-seg and the McCluskey's Pawn Shop circuits in ModelSim.

- Demonstrate both the double 7-seg and the McCluskey's Pawn Shop circuits on the DE1 board.

- Be prepared to answer questions on both the theoretical and practical parts of the lab.

Grading

Working Design

60 points for correctness, style, and testing.