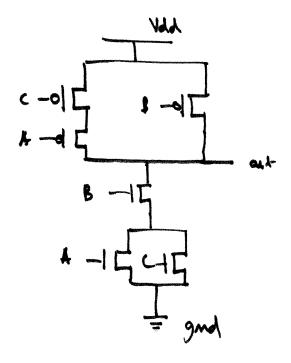

### Question 1) CMOS transistor level circuits

Part 1 (20 points): Draw the CMOS transistor level circuit that implements the following function:  $\sim$ ((A + C)B). Use as few transistors as possible. Make sure to label ground, Vdd and the input and output signals. This problem will be graded on the quality of the circuit as well as its correctness.

#### Question 2) Flip-flops

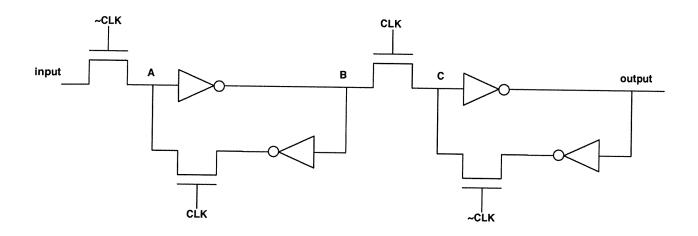

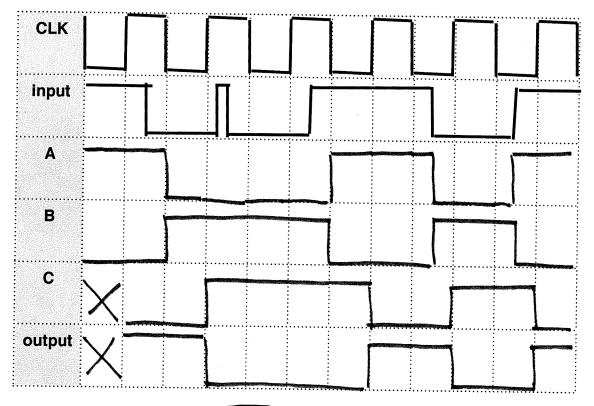

Part 1 (15 points): Given the following flip-flop (PMOS transistors are not shown for simplicity):

Fill in the following table. If something cannot be known, place an X in that region.

Part 2 (5 points): Is this a positive edge triggered flip flop or negative edge triggered flip flop?

#### Question 3) Full Adders

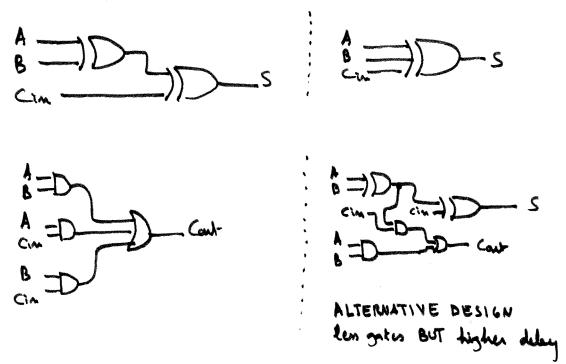

Part 1 (10 points): Draw the gate-level circuit for a full adder. Clearly label the inputs, and outputs.

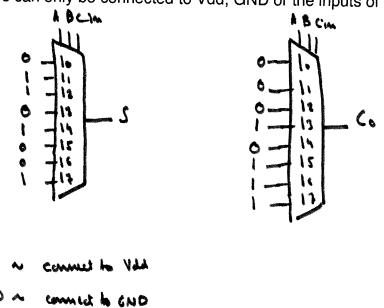

Part 2 (10 points): Implement a full adder using two 8:1 multiplexers. The inputs of the multiplexers can only be connected to Vdd, GND or the inputs of your full adder.

Question 4) Arithmetic Circuits (2 pages!)

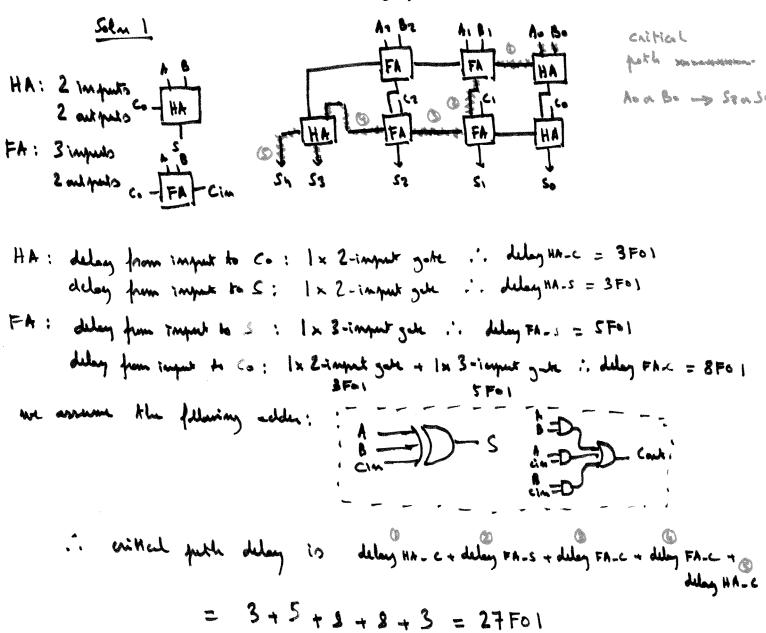

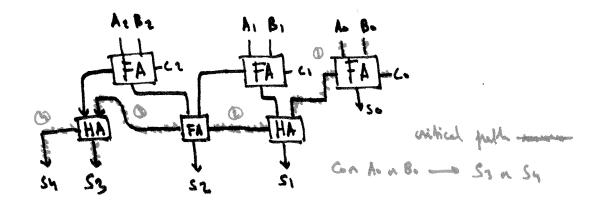

Part 1 (10 points): Design a circuit using only full adders (FA) and half adders (HA) that computes the sum of three unsigned 3-bit integers A[2:0], B[2:0], C[2:0]. You will be graded based on correctness and efficiency.

Your full adders and half adders can be represented as block diagrams. For each adder, indicate which output is the sum, and which output is the carry. Make sure to clearly label your circuit to leave no room for ambiguity.

#### Part 2 (10 points):

Based on the following delays:

1 input gate = 1 FO1

2 input gate = 3 FO1

3 input gate = 5 FO1

(4 points) What is the critical path of your circuit (indicate on your diagram)?

(6 points) What is the critical path **delay** of your circuit? Show your work and state your assumptions.

Soln 2

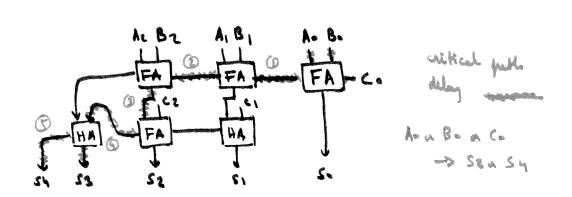

cuitical path dulay = dulay FA - c + dulay HA - c + dulay FA - c + dulay HA - c + dulay FA - c + dulay HA - c + dulay FA - c + dulay HA - c +

:. Forth them Solut & she 2!

Same resources on who 1

Question 5) Short answer (2 pages!)

4.1) (3 points) Order SRAM, DRAM and flip-flop by increasing number of transistors used per bit cell?

him DRAM, SRAM, flip-flip mu

- 4.2) (3 points) Provide one reason for using FPGAs vs. ASIC to implement a product.

- . boun up-front out

- . forter from to market

- . ormster design eycle

- · field uprogrammability

- 4.3) (3 points) Why are glitches undesirable?

glitches consume from

4.4) (3 points) Discuss the area and delay trade-offs between using a ripple-carry adder vs. a carry-select adder:

Ripph any adder: smaller are but longer delay comy relect adder: large area but shorter delay

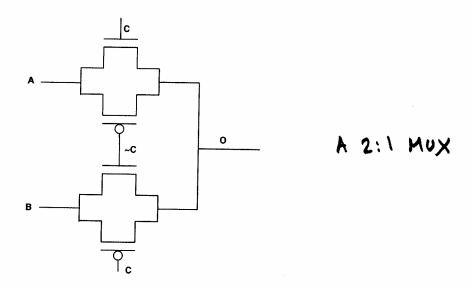

## 4.5) (4 points) What does this circuit implement?

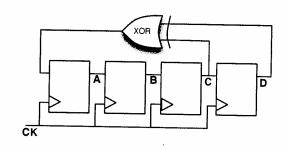

# 4.6) (4 points) This is the LFSR that you put together in Lab 3:

Derives the values of A, B, C, D at every clock tick for 4 consecutive clock ticks.

| Time | A | В | С | D |

|------|---|---|---|---|

| t=0  | 1 | 0 | 0 | 1 |

| t=1  | ١ | 1 | 0 | Ó |

| t=2  | ٥ | 1 | ١ | 0 |

| t=3  | 1 | 0 | ١ | 1 |

| t=4  | 0 | ١ | 0 | 1 |