## Q1: H&H4.2.

Parta

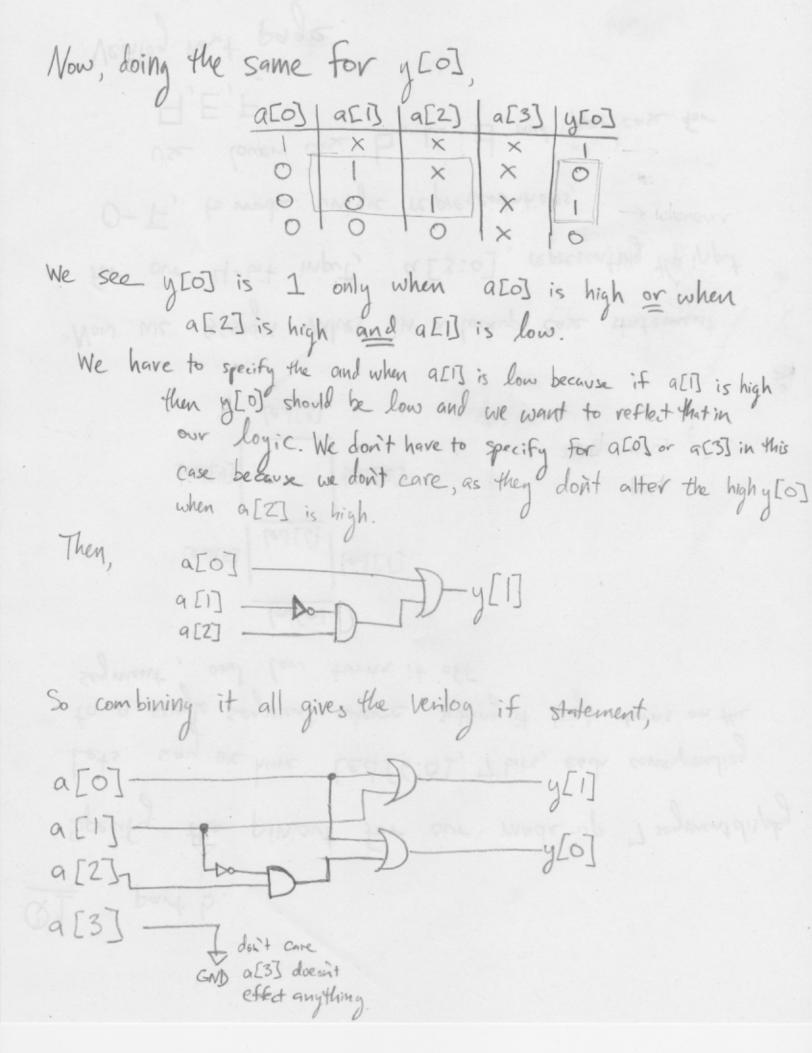

First, we will want to write out a trith table from the if-else logic. We will use X to denote don't care, as in the case of if a [o] is high, we don't care what any other input is, but we know y will be , y[1:0]=11. This helps simplify our trith table substantially.

Ly this final case is the default statement, and in this case a [1:0] is 0,0, which gives our y values.

If we had gone into k-maps you could step through to prove the optimal result, but we can readily see it here,

first consider y[1],  $\frac{q[0]}{|x|} = \frac{q[0]}{|x|} = \frac{q[0]}{|x|$

We see that y[1] is only high if a[0] or a[1] are high, y[1] is only Low if a[0] and a[1] are low.

Therefore, a[o] — y[i] completely describes the behavior in the Veritory code for y[i].

## Q1 part b.

Specify the pinout for our made-up 7 segment display Let's say we have Led [6:0], 7 bits, each corresponding to a single segment, where setting it high turns on the segment, and low turns it off.

Now we assign values in a lookup case statement

For our 4-bit input, a [3:0], representing the input

O-F, to make unique representations,

use lower case b, E, H and upper case for

F, E, F.

Verilog next page.

```

module display(

input [3:0]in,

output [6:0]out);

//for pins,

//a[0] is top a[1] is top right a[2] is bottom right

//a[3] is bottom a[4] is bottom left a[5] is top left

//a[6] is center

//b'1 is high for pin

//b'0 is low

//Decoder will implement as combo logic

assign out = (in == 4'h0) ? 7'b011 1111 :

(in == 4'h1) ? 7'b000_0110 :

(in == 4'h2) ? 7'b101_1011 :

(in == 4'h3) ? 7'b100_1111 :

(in == 4'h4) ? 7'b110 0110 :

(in == 4'h5) ? 7'b110 1101 :

(in == 4'h6) ? 7'b111 1101 :

(in == 4'h7) ? 7'b000_0111 :

(in == 4'h8) ? 7'b111 1111 :

(in == 4'h9) ? 7'b110 1111 :

(in == 4'hA) ? 7'b111_0111 :

(in == 4'hB) ? 7'b111_1100 :

(in == 4'hC) ? 7'b010 0111 :

(in == 4'hD) ? 7'b101 1110 :

(in == 4'hE) ? 7'b111 1001 :

(in == 4'hF) ? 7'b111_0011 : 7'b000_0000;

```

endmodule

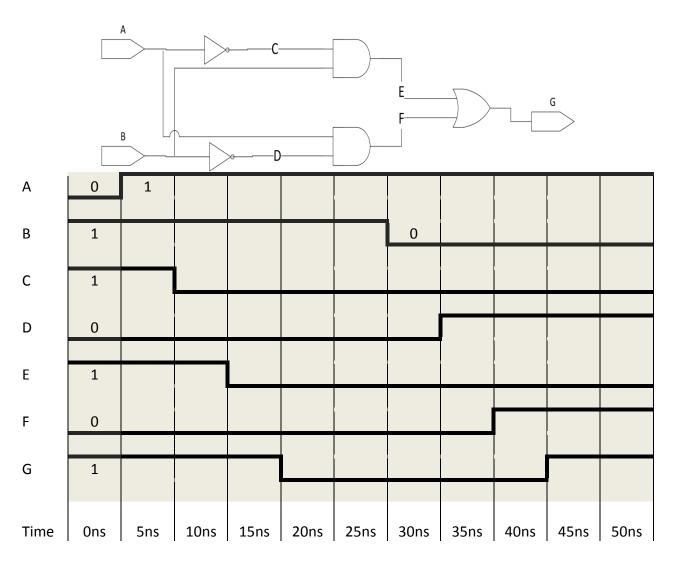

Q2: For the circuit below, assume that all gates have the same delay (including inverters) of 5 ns, complete the timing diagrams.

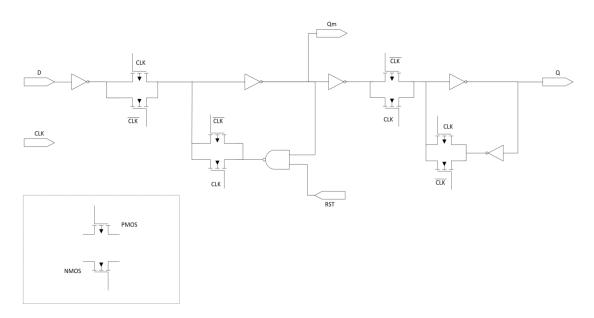

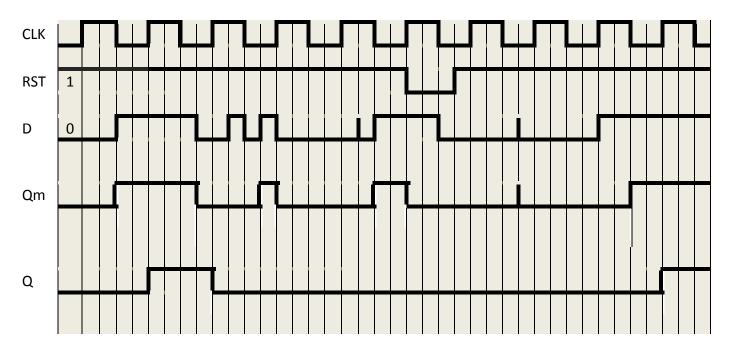

Q3: Complete the timing diagram for the circuit below for 10 clock cycles. Is the reset signal active low or active high? **Active low**

You have learned from class that this circuit is a crucial component in sequential logic design. What is it and why do you think it might be useful? This is a DFF, a main component in building registers, state machines and ALU.