## Memory & Caches IV

CSE 351 Autumn 2022

#### **Instructor:**

#### **Teaching Assistants:**

Justin Hsia

Angela Xu Assaf Vayner David Dai James Froelich Paul Stevans Arjun Narendra Carrie Hu Dominick Ta Jenny Peng Renee Ruan

Armin Magness Clare Edmonds Effie Zheng Kristina Lansang Vincent Xiao

| REFRESH TYPE    | EXAMPLE SHORTCUTS                            | EFFECT                                |

|-----------------|----------------------------------------------|---------------------------------------|

| SOFT REFRESH    | GMAIL REFRESH BUTTON                         | REQUESTS UPDATE WITHIN JAVASCRIPT     |

| NORMAL REFRESH  | F5, стя⊩R, ЖR                                | REFRESHES PAGE                        |

| HARD REFRESH    | ctrl-F5, ctrl-습, 瑞ዕR                         | REFRESHES PAGE INCLUDING CACHED FILES |

| HARDER REFRESH  | CTRL-①-HYPER-ESC-R-F5                        | REMOTELY CYCLES POWER TO DATACENTER   |

| HARDEST REFRESH | CTRL-H■①#-R-F5-F-5-<br>ESC-O-Ø-Ø-≜-50R0LLOCK | INTERNET STARTS OVER FROM ARPANET     |

http://xkcd.com/1854/

#### **Relevant Course Information**

- Lab 4 released today, due Monday, Nov. 28

- Cache parameter puzzles and code optimizations

- hw17 due Wed (11/16), hw19 due Fri (11/18)

- Lab 4 preparation

- Midterm scores posted

- See Ed post for common misconceptions

- Regrade requests open from Nov. 15-17 (Tue-Thu)

## **Growth vs. Fixed Mindset**

- Students can be thought of as having either a "growth" mindset or a "fixed" mindset (based on research by Prof. Carol Dweck)

- In a fixed mindset students believe their basic abilities, their intelligence, their talents, are just fixed traits. They have a certain amount and that's that, and then their goal becomes to look smart all the time and never look dumb."

- "In a growth mindset students understand that their talents and abilities can be developed through effort, good teaching and persistence. They don't necessarily think everyone's the same or anyone can be Einstein, but they believe everyone can get smarter if they work at it."

#### **Reading Review**

- Terminology:

- Write-hit policies: write-back, write-through

- Write-miss policies: write allocate, no-write allocate

- Cache blocking

- Questions from the Reading?

## What about writes? (Review)

- Multiple copies of data may exist:

- multiple levels of cache and main memory

- What to do on a write-hit?

- Write-through: write immediately to next level

- Write-back: defer write to next level until line is evicted (replaced)

- Must track which cache lines have been modified ("dirty bit")

- What to do on a write-miss?

- Write allocate: ("fetch on write") load into cache, then execute the write-hit policy

- Good if more writes or reads to the location follow

- No-write allocate: ("write around") just write immediately to next level

- Typical caches:

- Write-back + Write allocate, usually

- Write-through + No-write allocate, occasionally

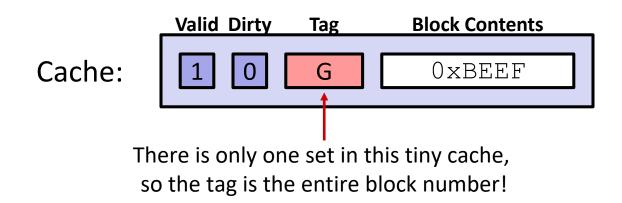

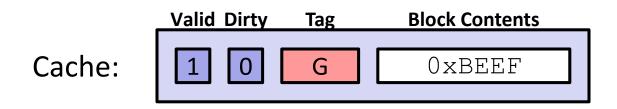

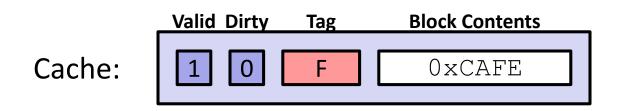

<u>Note</u>: We are making some unrealistic simplifications to keep this example simple and focus on the cache policies

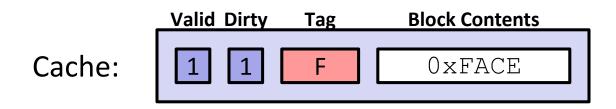

1) mov \$0xFACE, (F) ✓ Not valid x86, assume we mean an address associated with this block num Write Miss

<u>Step 1</u>: Bring **F** into cache

#### 1) mov \$0xFACE, (F) Write Miss

<u>Step 1</u>: Bring **F** into cache

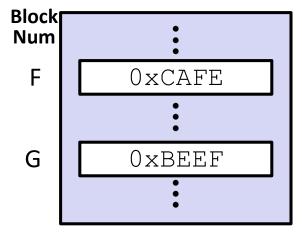

Step 2: Write 0xFACE to cache only and set the dirty bit

#### 1) mov \$0xFACE, (F) Write Miss

<u>Step 1</u>: Bring **F** into cache

Step 2: Write 0xFACE to cache only and set the dirty bit

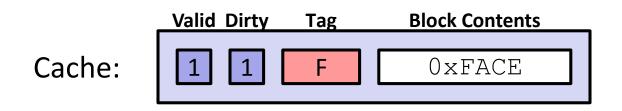

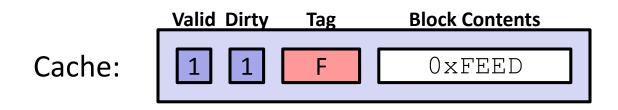

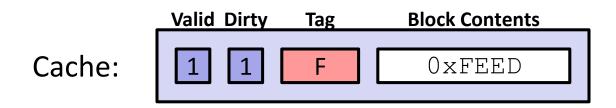

1) mov \$0xFACE, (F)2) mov \$0xFEED, (F)Write MissWrite Hit

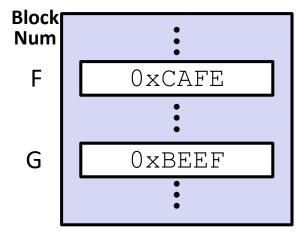

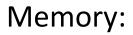

Memory:

Step: Write 0xFEED to cache only (and set the dirty bit)

1) mov \$0xFACE, (F) 2) mov \$0xFEED, (F) Write Miss Write Hit

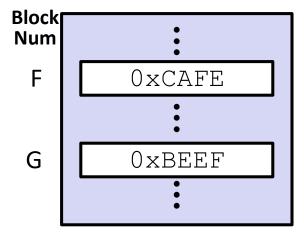

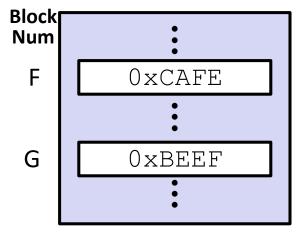

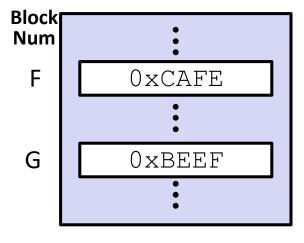

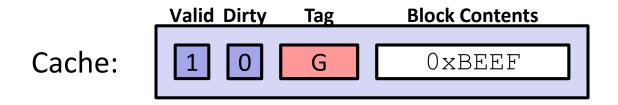

1) mov \$0xFACE, (F)

2) mov \$0xFEED, (F)

3) mov (G), %ax

Write Miss

Write Hit

Read Miss

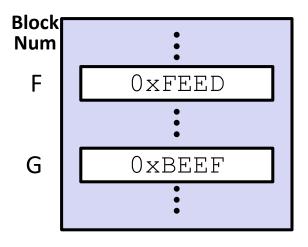

<u>Step 1</u>: Write **F** back to memory since it is dirty

1) mov \$0xFACE, (F)2) mov \$0xFEED, (F)Write MissWrite Hit

3) mov (G), %ax Read Miss

Memory:

<u>Step 1</u>: Write **F** back to memory since it is dirty

Step 2: Bring **G** into the cache so that we can copy it into %ax

#### **Cache Simulator**

- Want to play around with cache parameters and policies? Check out our cache simulator!

- https://courses.cs.washington.edu/courses/cse351/cachesim/

- Way to use:

- Take advantage of "explain mode" and navigable history to test your own hypotheses and answer your own questions

- Self-guided Cache Sim Demo posted along with Section 7

- Will be used in HW19 Lab 4 Preparation

## **Polling Question**

- Which of the following cache statements is FALSE?

- Vote in Ed Lessons

- A. We can reduce compulsory misses by decreasing our block size

- **B.** We can reduce conflict misses by increasing associativity

- C. A write-back cache will save time for code with good temporal locality on writes

- **D.** A write-through cache will always match data with the memory hierarchy level below it

- E. We're lost...

## **Optimizations for the Memory Hierarchy**

- Write code that has locality!

- Spatial: access data contiguously

- <u>Temporal</u>: make sure access to the same data is not too far apart in time

- How can you achieve locality?

- Adjust memory accesses in *code* (software) to improve miss rate (MR)

- Requires knowledge of *both* how caches work as well as your system's parameters

- Proper choice of algorithm

- Loop transformations

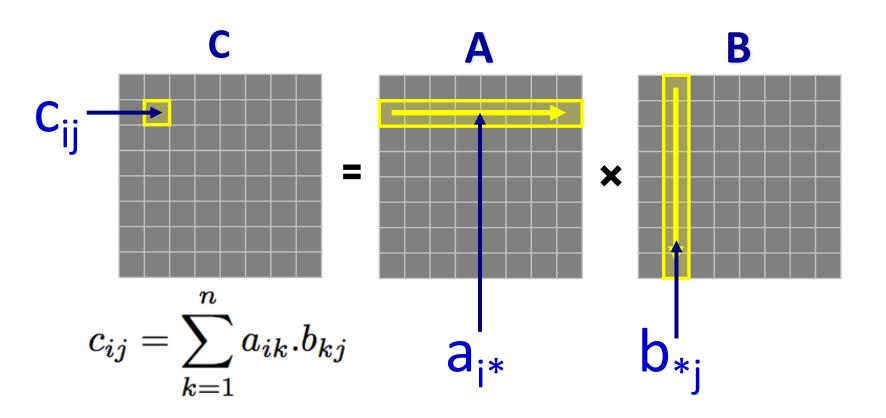

#### **Example:** Matrix Multiplication

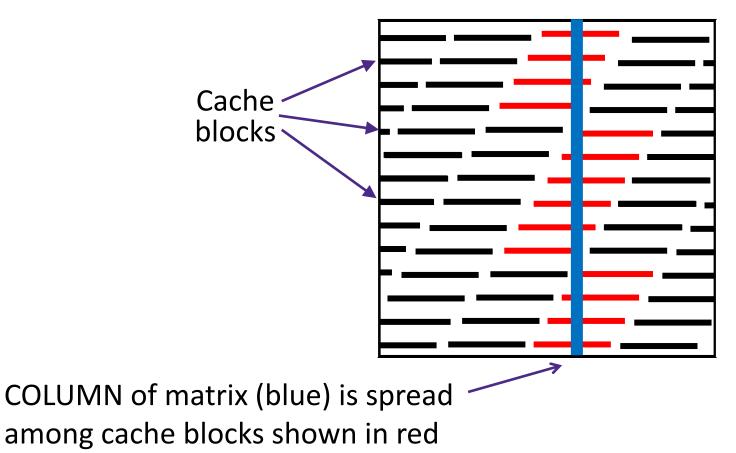

#### **Matrices in Memory**

- How do cache blocks fit into this scheme?

- Row major matrix in memory:

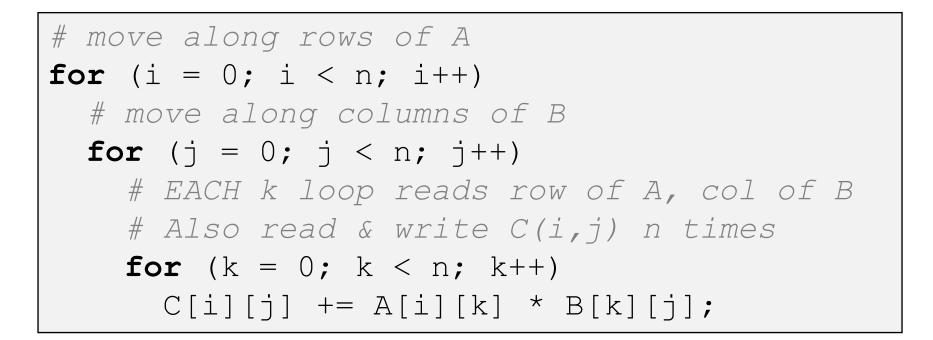

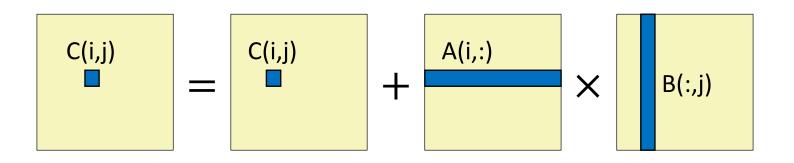

#### Naïve Matrix Multiply

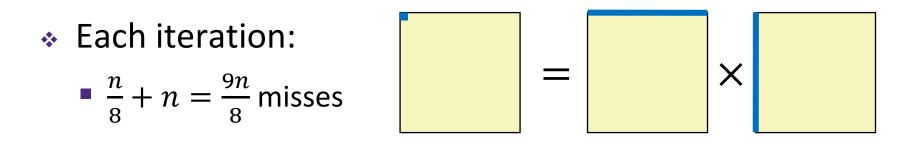

## Cache Miss Analysis (Naïve)

- Scenario Parameters:

- Square matrix (n × n), elements are doubles

- Cache block size K = 64 B = 8 doubles

- Cache size is much smaller than n

## Cache Miss Analysis (Naïve)

- Scenario Parameters:

- Square matrix (n × n), elements are doubles

- Cache block size K = 64 B = 8 doubles

- Cache size is much smaller than n

8 doubles wide

## Cache Miss Analysis (Naïve)

- Scenario Parameters:

- Square matrix (n × n), elements are doubles

- Cache block size K = 64 B = 8 doubles

- Cache size is much smaller than n

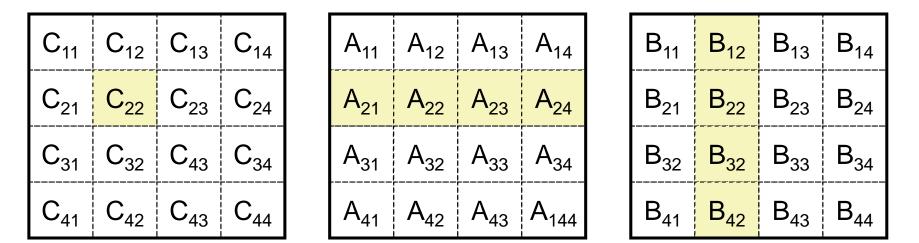

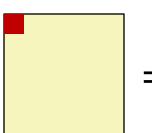

## Linear Algebra to the Rescue (1)

- Can get the same result of a matrix multiplication by splitting the matrices into smaller submatrices (matrix "blocks")

- For example, multiply two 4×4 matrices:

$$A = \begin{bmatrix} a_{11} & a_{12} & a_{13} & a_{14} \\ a_{21} & a_{22} & a_{23} & a_{24} \\ a_{31} & a_{32} & a_{33} & a_{34} \\ a_{41} & a_{42} & a_{43} & a_{44} \end{bmatrix} = \begin{bmatrix} A_{11} & A_{12} \\ A_{21} & A_{22} \end{bmatrix}, \text{ with } B \text{ defined similarly.}$$

$$AB = \begin{bmatrix} (A_{11}B_{11} + A_{12}B_{21}) & (A_{11}B_{12} + A_{12}B_{22}) \\ (A_{21}B_{11} + A_{22}B_{21}) & (A_{21}B_{12} + A_{22}B_{22}) \end{bmatrix}$$

## Linear Algebra to the Rescue (2)

This is extra (non-testable) material

Matrices of size  $n \times n$ , split into 4 blocks of size r (n=4r)

$$C_{22} = A_{21}B_{12} + A_{22}B_{22} + A_{23}B_{32} + A_{24}B_{42} = \sum_{k} A_{2k}^{*}B_{k2}$$

- Multiplication operates on small "block" matrices

- Choose size so that they fit in the cache!

- This technique called "cache blocking"

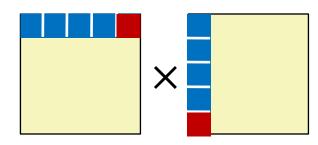

#### **Blocked Matrix Multiply**

Blocked version of the naïve algorithm:

```

# move by rxr BLOCKS now

for (i = 0; i < n; i += r)

for (j = 0; j < n; j += r)

for (k = 0; k < n; k += r)

# block matrix multiplication

for (ib = i; ib < i+r; ib++)

for (jb = j; jb < j+r; jb++)

for (kb = k; kb < k+r; kb++)

C[ib][jb] += A[ib][kb] * B[kb][jb];

```

r = block matrix size (assume r divides n evenly)

Ignoring

matrix

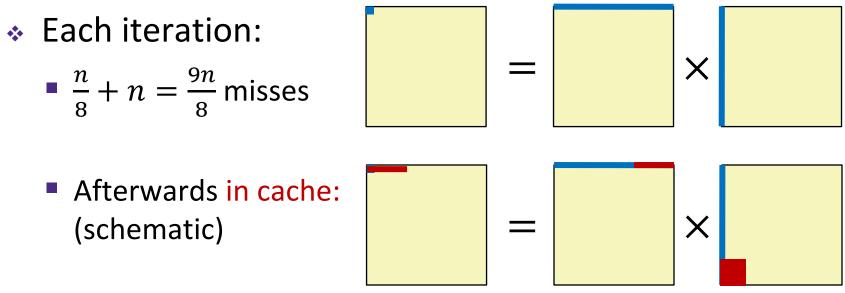

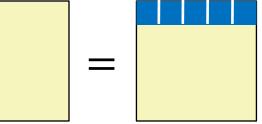

# Cache Miss Analysis (Blocked)

- Cache block size K = 64 B = 8 doubles

- Cache size is much smaller than n

- Three blocks  $\square$  ( $r \times r$ ) fit into cache:  $3r^2 <$  cache size

$r^2$  elements per block, 8 per cache block

- Sech block iteration:

- $r^{2}/8$  misses per block

$$2n/r \times r^2/8 = nr/4$$

n/r blocks

n/r blocks in row and column

Ignoring

matrix ()

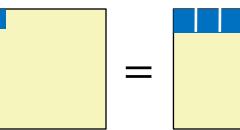

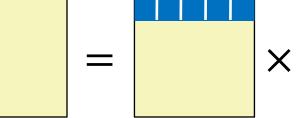

# Cache Miss Analysis (Blocked)

- Scenario Parameters:

- Cache block size K = 64 B = 8 doubles

- Cache size is much smaller than n

- Three blocks  $\square$  ( $r \times r$ ) fit into cache:  $3r^2 <$  cache size

$r^2$  elements per block, 8 per cache block

- Sech block iteration:

- $r^{2}/8$  misses per block

$$2n/r \times r^2/8 = nr/4$$

n/r blocks in row and column

Afterwards in cache (schematic)

Ignoring

matrix

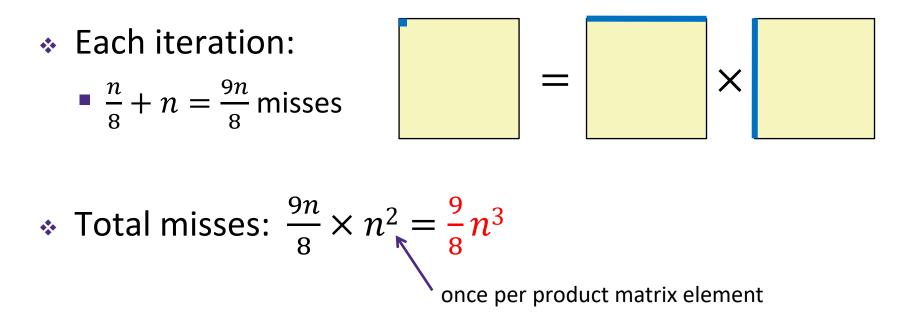

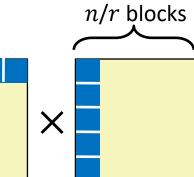

# Cache Miss Analysis (Blocked)

- Scenario Parameters:

- Cache block size K = 64 B = 8 doubles

- Cache size is much smaller than n

- Three blocks  $\square$  ( $r \times r$ ) fit into cache:  $3r^2 <$  cache size

$r^2$  elements per block, 8 per cache block

- Each block iteration:

- $r^2/8$  misses per block

$$2n/r \times r^2/8 = nr/4$$

$\times$

n/r blocks in row and column

- Total misses:

- $nr/4 \times (n/r)^2 = n^3/(4r)$

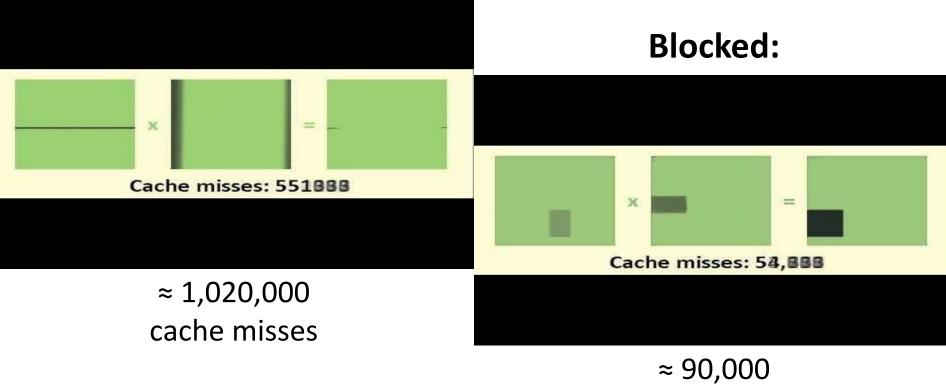

#### **Matrix Multiply Visualization**

cache misses

#### **Cache-Friendly Code**

- Programmer can optimize for cache performance

- How data structures are organized

- How data are accessed

- Nested loop structure

- Blocking is a general technique

- All systems favor "cache-friendly code"

- Getting absolute optimum performance is very platform specific

- Cache size, cache block size, associativity, etc.

- Can get most of the advantage with generic coding rules

- Keep working set reasonably small (temporal locality)

- Use small strides (spatial locality)

- Focus on inner loop code

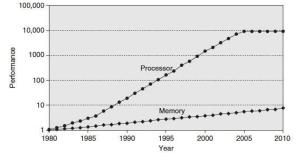

#### Cache Motivation, Revisited

- Memory accesses are expensive!

- Massive speedups to processors without similar speedups in memory only made the problem worse

- "Processor-Memory Bottleneck":

- We defined "locality", based on observations about existing programs, written by an extremely small subset of the population

- We built hardware that utilizes locality to improve performance (*e.g.*, AMAT)

## Cache "Conclusions"

- All systems favor "cache-friendly code"

- Can get most of the advantage with generic coding rules

- Me implicitly made value judgments about "good" and "bad" code

- "Good" code exhibits "good" locality

- "Good" code might be considered the (desired) common case

## **Common Case Optimizations**

- Optimizing for the common case is a classic (arguably foundational) CS technique!

- *e.g.*, algorithms analysis often uses worse case or average case performance

- e.g., caches optimize for an average program ("most programs") that exhibits locality

- Natural conclusion is to make the common case as performant as possible at the expense of edge-cases

- Generally, bigger performance impact with common case than edge case optimizations

- What's the danger here?

#### The Common Case and Normativity

- "Normativity is the phenomenon in human societies of designating some actions or outcomes as good or desirable or permissible and others as bad or undesirable or impermissible."

- https://en.wikipedia.org/wiki/Normativity

- Norms are what are considered "usual" or "expected"

- These often get conflated with the common case: norm gets "common case" treatment, abnormal gets "edge case" treatment

- Who determines the norms?

**D**ProVision

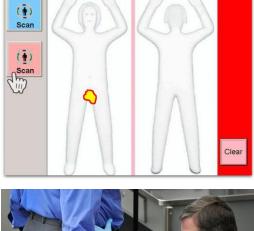

## **Example: TSA Body Scanners**

- TSA used machine learning to determine predictable variation among "average" bodies

- Built two models: one for "men" and one for "women"

- TSA agent chooses model to use based on how the traveler is presenting:

- Who are the "edge cases?"

- What is the "edge case performance?"

#### **Design Considerations**

- Make sure you account for non-normative cases

- Is this (change to) edge-case behavior okay/acceptable?

- Be careful of implicit normative assumptions

- Can erase people's experiences and diversity, even labeling/categorizing them as threats

- Caches aren't neutral, either they assume that the underlying data doesn't change

- Changes can come from above (the CPU), but not from below

- *e.g.*, changing your name in Google Drive "breaks" the browser cache

- Discuss: Where else do you see normative assumptions made in tech or CS?