Effie Zheng

CSE351, Autumn 2022

# Memory & Caches III

CSE 351 Autumn 2022

Instructor: Teaching Assistants:

Justin Hsia Angela Xu Arjun Narendra Armin Magness

Assaf Vayner Carrie Hu Clare Edmonds

David Dai Dominick Ta

James Froelich Jenny Peng Kristina Lansang

Paul Stevans Renee Ruan Vincent Xiao

http://xkcd.com/908/

#### **Relevant Course Information**

- Lab 3 due Friday (11/11)

- Lab 4 released Monday, due after Thanksgiving

- Can do Part 1 after today; will need Lecture 19 to do Part 2

- hw17 due Wednesday (11/16)

- Covers the major cache mechanics BIG homework

## Making memory accesses fast!

- Cache basics

- Principle of locality

- Memory hierarchies

- Cache organization

- Direct-mapped (sets; index + tag)

- Associativity (ways)

- Replacement policy

- Handling writes

- Program optimizations that consider caches

## **Reading Review**

- Terminology:

- Associativity: sets, fully-associative cache

- Replacement policies: least recently used (LRU)

- Cache line: cache block + management bits (valid, tag)

- Cache misses: compulsory, conflict, capacity

- Questions from the Reading?

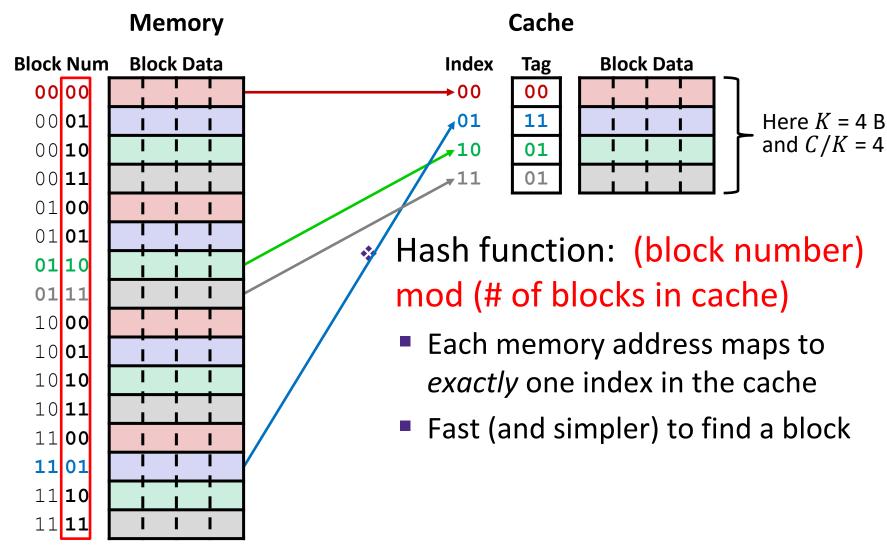

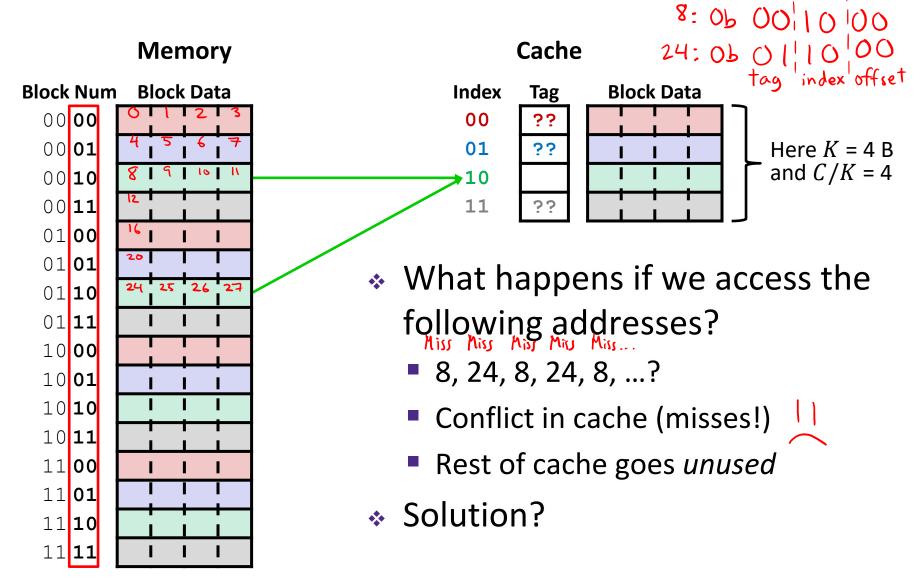

#### **Review: Direct-Mapped Cache**

# **Direct-Mapped Cache Problem**

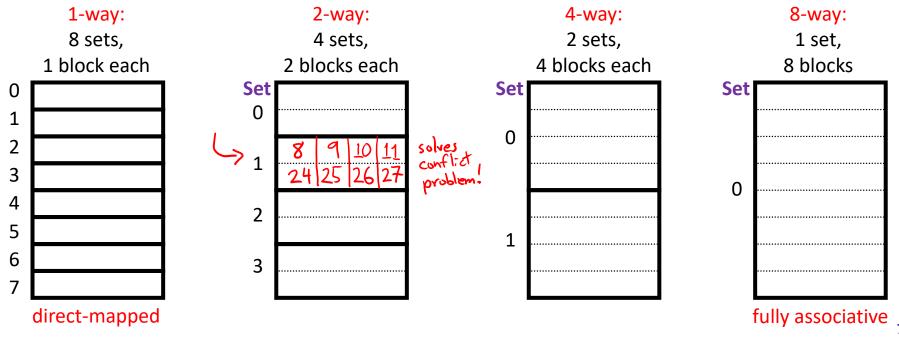

# **Associativity**

- What if we could store data in any place in the cache?

- More complicated hardware = more power consumed, slower

- So we combine the two ideas:

- Each address maps to exactly one set

- Each set can store block in more than one way

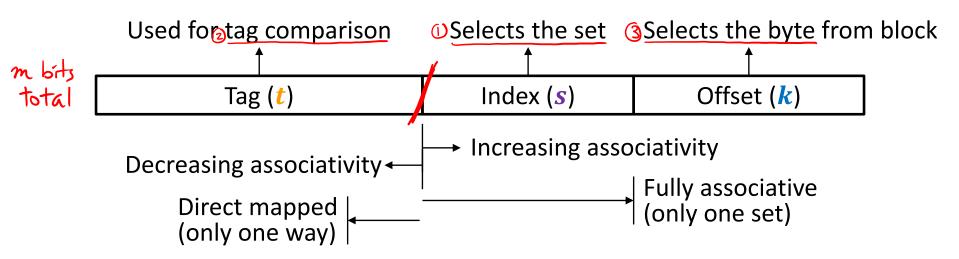

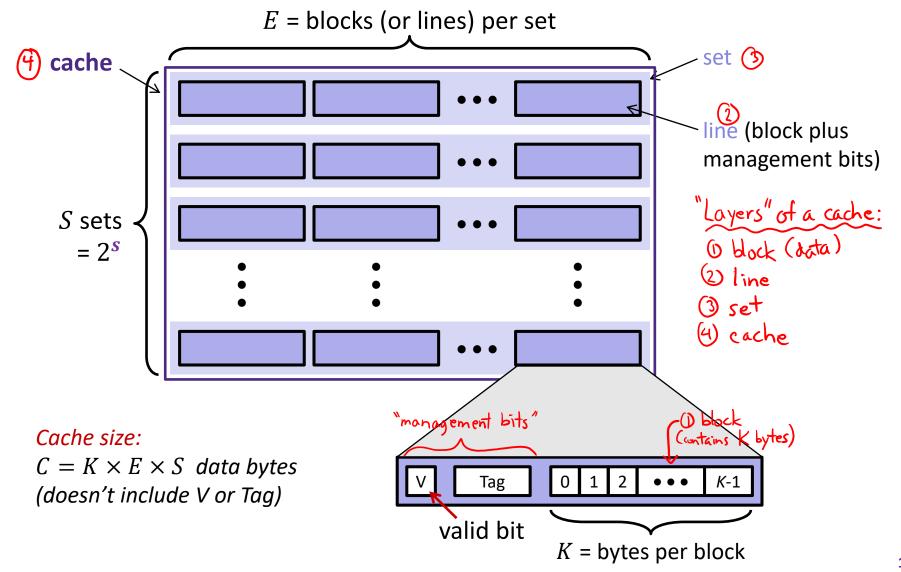

# **Cache Organization (3)**

**Note:** The textbook uses "b" for offset bits

- $\star$  Associativity (E): # of ways for each set

- Such a cache is called an "E-way set associative cache"

- We index into cache *sets*, of which there are S = (C/K)/E

- Use lowest  $log_2(S) = s$  bits of block address

- <u>Direct-mapped</u>: E = 1, so  $s = \log_2(C/K)$  as we saw previously

- Fully associative: E = C/K, so s = 0 bits

# **Example Placement**

block size: 16 B

capacity: 8 blocks

address: 16 bits

\* Where would data from address  $0 \times 1833$  be placed?

■ Binary: 0b 0001 1000 0011, 0011

t = m - s - k  $s = \log_2(C/K/E)$   $k = \log_2(K)$

*m*-bit address:

Tag (t) Index (s) Offset (k)

S = ?

Direct-mapped

Set Tag Data

(00) 0

(001) 1

(00) 2

(01) 3

(10) 4

(10) 5

(10) 6

(11) 7

s = ?

s = ?

# **Block Placement and Replacement**

- Any empty block in the correct set may be used to store block

- Valid bit for each cache block indicates if valid (1) or mystery (0) data

- If there are no empty blocks, which one should we replace?

- No choice for direct-mapped caches

- Caches typically use something close to least recently used (LRU)

(hardware usually implements "not most recently used")

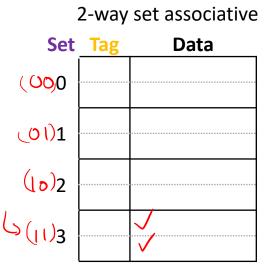

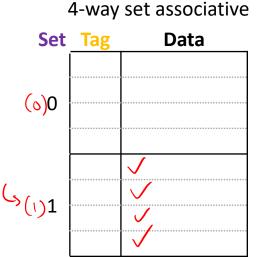

|     |   | Dire | 2-way set associative |     |   |     | 4-way set associative |     |   |     |      |

|-----|---|------|-----------------------|-----|---|-----|-----------------------|-----|---|-----|------|

| Set | V | Tag  | Data                  | Set | V | Tag | Data                  | Set | V | Tag | Data |

| 0   |   |      |                       | 0   |   |     |                       |     |   |     |      |

| 1 [ |   |      |                       | U   |   |     |                       | 0   |   |     |      |

| 2   |   |      |                       | 1   |   |     |                       | U   |   |     |      |

| 3   |   |      |                       | 1   |   |     |                       |     |   |     |      |

| 4   |   |      |                       | 2   |   |     |                       |     |   |     |      |

| 5   |   |      |                       |     |   |     |                       | 1   |   |     |      |

| 6   |   |      |                       | 2   |   |     |                       | 1   |   |     |      |

| 7   |   | ·    |                       | 3   |   |     |                       |     |   |     |      |

# **Polling Questions**

- We have a cache of size 2 KiB with block size of 128 B.

If our cache has 2 sets, what is its associativity?

- Vote in Ed Lessons

each set has

cache holds C/K=211-7=24=16 blocks

Α. 2

B. 4

C. 8

D. 16

E. We're lost...

set 0

S = C/K/E E = (C/K)/S = 16/2 = 8cache size

M=16

\* If addresses are 16 bits wide, how wide is the Tag field?  $k = log_2(K) = 7 bits$ ,  $s = log_2(S) = 1 bit$ , t = m - s - k = 8 bits

CSE351, Autumn 2022

#### **Notation Review**

- We just introduced a lot of new variable names!

- Please be mindful of block size notation when you look at past exam questions or are watching videos

| Parameter          | Variable                     | Formulas                                                                                                                         |  |  |  |  |

|--------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Block size         | K (B in book)                |                                                                                                                                  |  |  |  |  |

| Cache size         | С                            | $M = 2m \times m = \log M$                                                                                                       |  |  |  |  |

| Associativity      | E                            | $M = 2^{m} \leftrightarrow m = \log_{2} M$ $S = 2^{s} \leftrightarrow s = \log_{2} S$ $K = 2^{k} \leftrightarrow k = \log_{2} K$ |  |  |  |  |

| Number of Sets     | S                            |                                                                                                                                  |  |  |  |  |

| Address space      | M                            | $C = K \times E \times S$                                                                                                        |  |  |  |  |

| Address width      | m                            | $\mathbf{s} = \log_2(C/K/E)$                                                                                                     |  |  |  |  |

| Tag field width    |                              | m = t + s + k                                                                                                                    |  |  |  |  |

| Index field width  | S                            |                                                                                                                                  |  |  |  |  |

| Offset field width | <b>k</b> ( <b>b</b> in book) |                                                                                                                                  |  |  |  |  |

## **Example Cache Parameters Problem**

>210 B (=> m=10 bits MP

4 1 KiB address space, 125 cycles to go to memory.

Fill in the following table:

| C                     | Cache Size    | 64 B                            | 2° 1             |  |

|-----------------------|---------------|---------------------------------|------------------|--|

| K                     | Block Size    | 8 B                             | 2 <sup>3</sup> 2 |  |

| E                     | Associativity | 2-way                           | 2' 3             |  |

| HT                    | Hit Time      | 3 cycles                        |                  |  |

| MR                    | Miss Rate     | 20%                             |                  |  |

| t=m-s-k               | Tag Bits      | 5                               |                  |  |

| $\leq = log_2(C/K/E)$ | Index Bits    | 2                               | 2 /2 /21         |  |

| $k = log_2(k)$        | Offset Bits   | 3                               |                  |  |

| AMAT= HT+MR*MP        | AMAT          | 3+(1.2(125)= 28 clock<br>cycles |                  |  |

Locate set

Check if any line in set

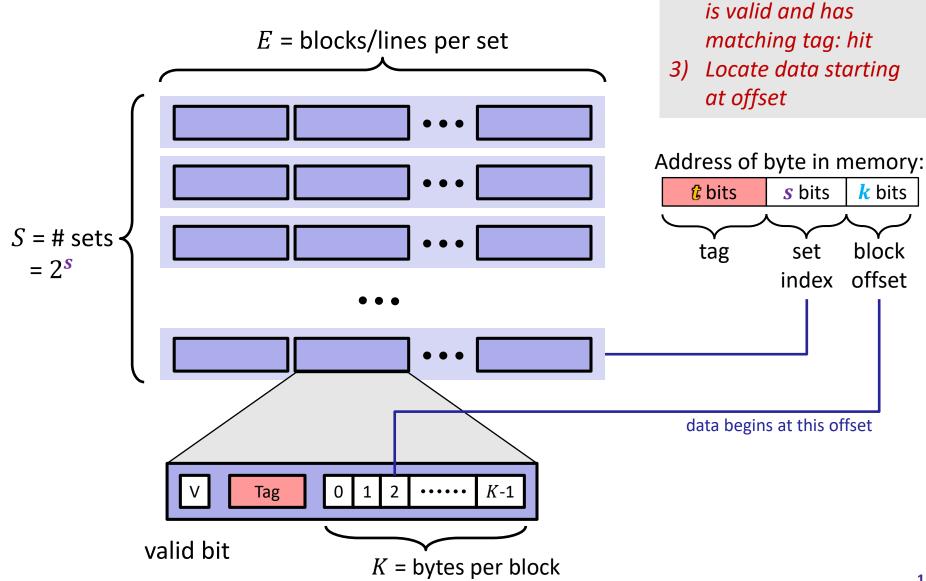

#### **Cache Read**

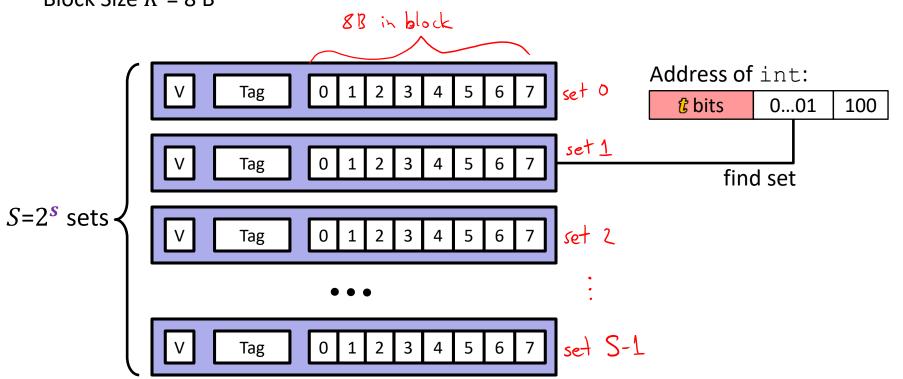

# Example: Direct-Mapped Cache (E = 1)

Direct-mapped: One line per set

Block Size K = 8 B

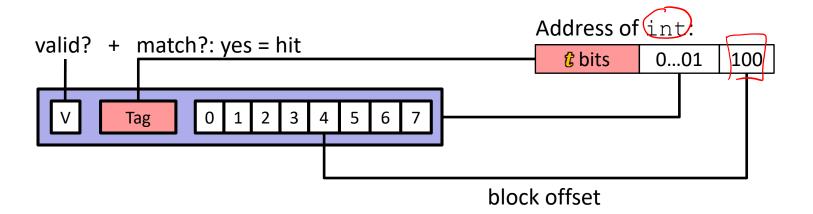

# Example: Direct-Mapped Cache (E = 1)

Direct-mapped: One line per set

Block Size K = 8 B

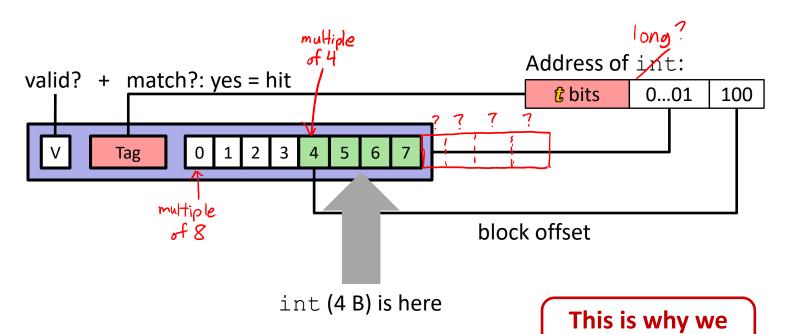

# Example: Direct-Mapped Cache (E = 1)

L18: Caches III

Direct-mapped: One line per set

Block Size K = 8 B

No match? Then old line gets evicted and replaced

no unnecessary extra cache accesses across block boundaries

want alignment!

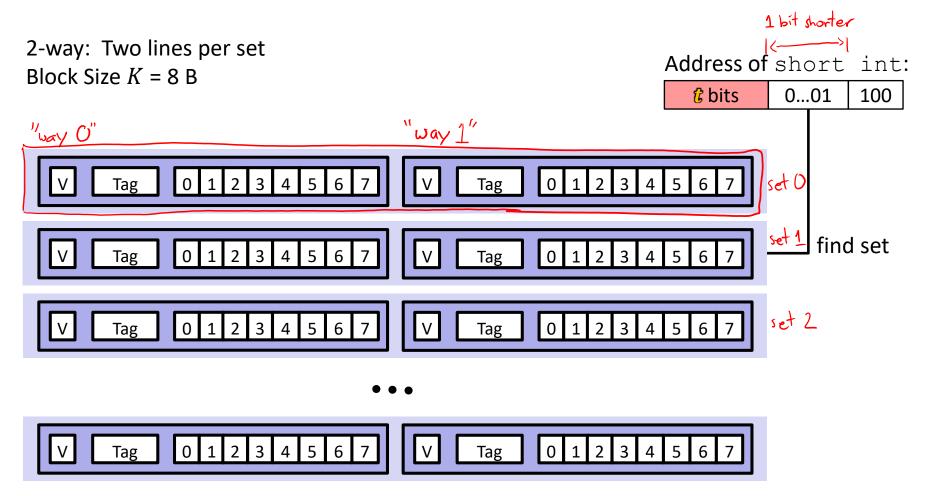

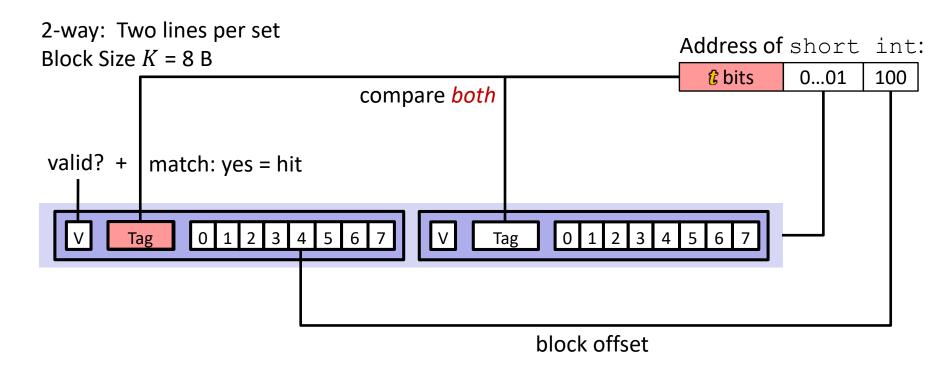

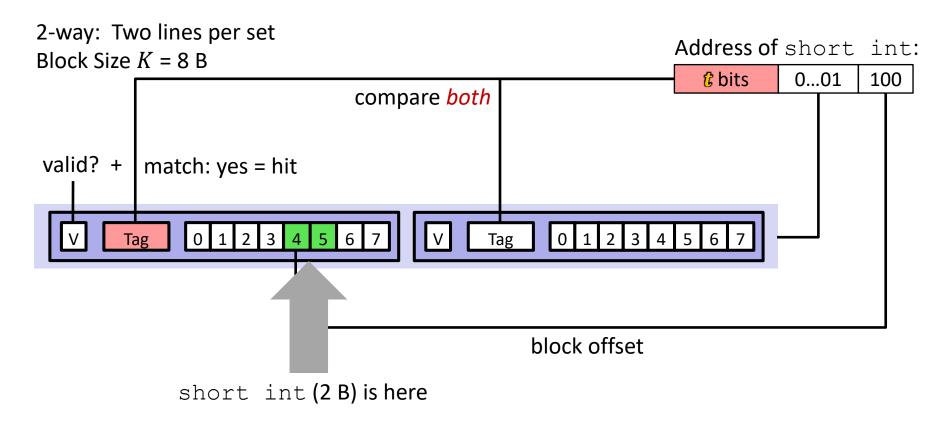

# Example: Set-Associative Cache (E = 2)

# Example: Set-Associative Cache (E = 2)

# Example: Set-Associative Cache (E = 2)

#### No match?

- One line in set is selected for eviction and replacement

- Replacement policies: random, least recently used (LRU), ...

#### Types of Cache Misses: 3 C's!

- Compulsory (cold) miss

- Occurs on first access to a block

- Conflict miss

- Conflict misses occur when the cache is large enough, but multiple data objects all map to the same slot

- e.g., referencing blocks 0, 8, 0, 8, ... could miss every time

- Direct-mapped caches have more conflict misses than E-way set-associative (where E > 1)

- Capacity miss

- Occurs when the set of active cache blocks (the working set)

is larger than the cache (just won't fit, even if cache was fullyassociative)

- Note: Fully-associative only has Compulsory and Capacity misses

# **Example Code Analysis Problem**

- Assuming the cache starts <u>cold</u> (all blocks invalid) and sum, i, and j are stored in registers, calculate the **miss rate**:

- $\blacksquare$  m = 10 bits, C = 64 B, K = 8 B, E = 2

```

#define SIZE 8

short ar[SIZE][SIZE], sum = 0; // &ar=0x200

for (int i = 0; i < SIZE; i++)

for (int j = 0; j < SIZE; j++)

sum += ar[i][i];

|index | offset

4 shorts

(1" way)

10 0000

block:

cache: 03

61

Cache block holds

10

```